---

# Dimensionierung von passiven Bauteilen elektronischer Hochfrequenzschaltungen unter Berücksichtigung der parasitären Effekte auf Leiterplatten

Workshop Robustheit

Hannover, 28. Oktober 2008

---

Sebastiaan Wielens

Fraunhofer-Institut für Integrierte Schaltungen

Institutsteil Entwurfsautomatisierung Dresden

---

## Robuste Systeme

---

### Motivation

Durch zunehmende Verkleinerung der elektronischen Baugruppen und die Erhöhung der Arbeitsfrequenzen sind Einflüsse des mechanischen Aufbaus einer Schaltung nicht mehr vernachlässigbar:

- Parasitären Kapazitäten der Leiterplatten wirken sich direkt auf das elektrische Verhalten aus,

- die induktive Kopplung zwischen den einzelnen Bauteilen (z.B. Spulen) spielt eine immer größere Rolle.

Um trotz dieser nicht idealen Effekte **robuste Systeme** entwerfen zu können, müssen sie bereits innerhalb des Entwurfsprozesses berücksichtigt werden:

- Zur Dimensionierung der Bauteilwerte,

- Optimierung der Platinelayout,

- Zur Überprüfung des Einflusses der Bauteiltoleranzen auf das Gesamtsystem.

*Die Toleranzen der Bauteile sind entscheidend für deren Kosten, aber auch für den Robustheit des Gesamtsystems*

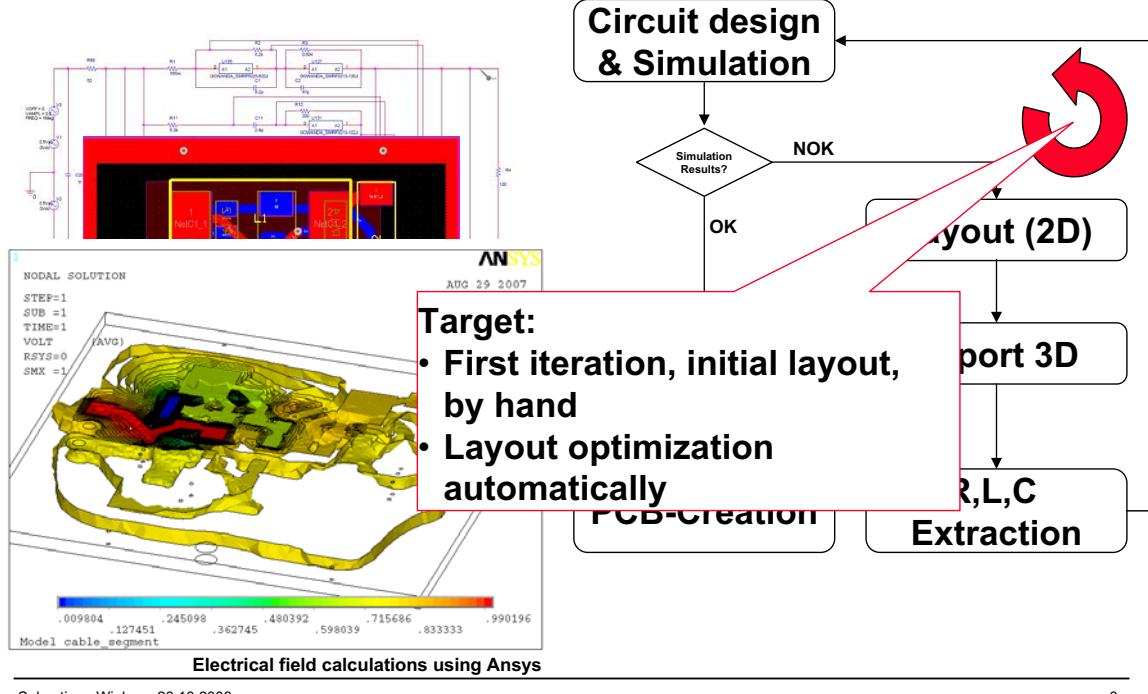

### Vorgehensweise

### Teilaspekte

Definition der Datenformate für die verschiedenen Werkzeuge (2D-, 3D-Formate)

Untersuchung der verschiedenen Werkzeuge und deren Exportmöglichkeiten für die

- Schaltungssimulation

- Layouterstellung

- Extraktion der RLC-Matrizen

Automatische Optimierung des Layouts innerhalb vorgegebener Grenzen

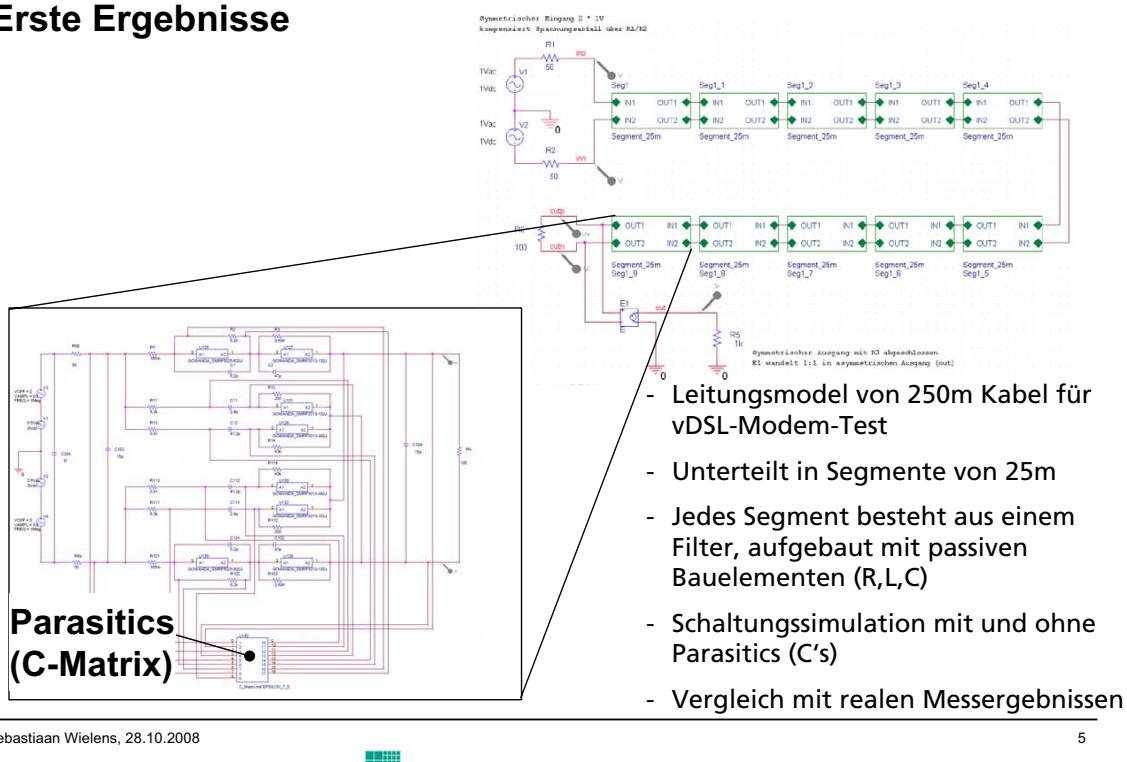

## Erste Ergebnisse

Sebastiaan Wielens, 28.10.2008

5

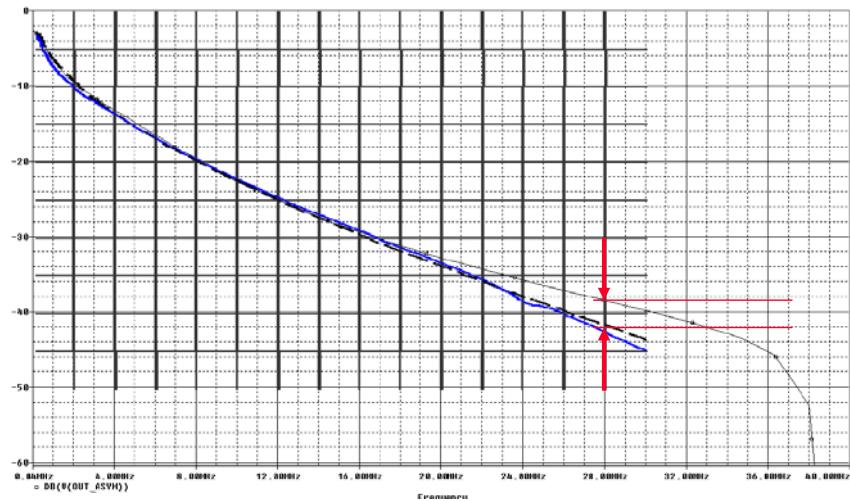

## Erste Ergebnisse – Pspice ohne Parasitics (C)

4dB Differenz @ 28MHz

Sebastiaan Wielens, 28.10.2008

6

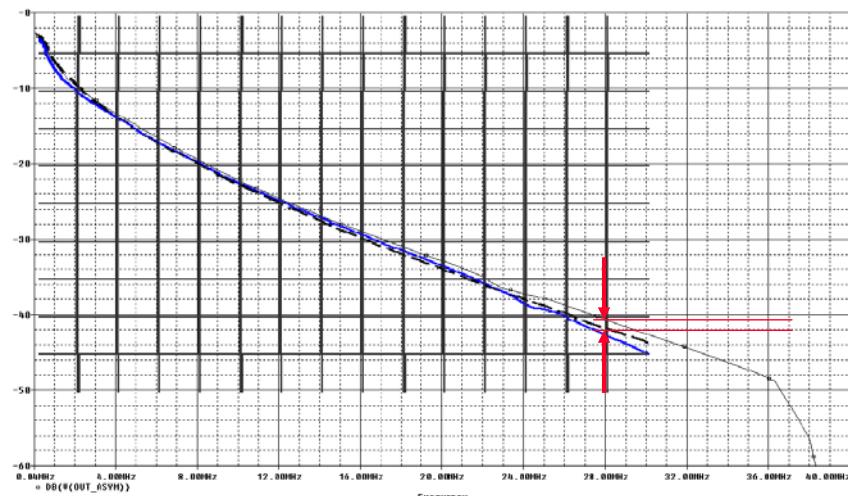

## Erste Ergebnisse – Pspice mit Parasitics (C)

2dB Differenz @ 28MHz