# newsletter edacentrum 03 2007

10,- Euro ISSN 1862 2283

electronic design automation centrum

[www.edacentrum.de/newsletter](http://www.edacentrum.de/newsletter)

## edaWorkshop 07

### Projektspiegel

„PRODUKTIV+: Messung der Produktivität beim Entwurf nanoelektronischer Systeme“, dazu Schlussberichte von LEONIDAS+ und SIDRA

### edaWorkshop – Erfolgreich aus der Taufe gehoben

Deutsche EDA-Forschung zu Gast in Hannover –

Ein Bericht vom edaWorkshop07

### EDA-Service

Der vom edacentrum erstellte „edaTrend DAC07“-Bericht ist für Mitglieder kostenfrei verfügbar

# Editorial

Liebe Leserinnen und Leser,

was für ein Sommer! – Nein, eigentlich ist das ein Satz aus dem Herbst 2006. Genauer betrachtet, passt er aber eigentlich immer, denn irgend etwas Bemerkenswertes gibt es wohl in jedem Sommer. Aber eins ist wohl sicher, im Gegensatz zum letzten Jahr gehörte das Wetter nicht, oder höchstens negativ dazu: So war der April in diesem Jahr bisher der sonnenreichste Monat, der es in Kaiserslautern auf fast 350 Sonnenstunden brachte, während dort in den Monaten Mai bis August jeweils nur etwa 200 Stunden die Sonne schien [1]. Und, was hatte denn der Sommer im Bezug auf EDA zu bieten?

[1] Quelle: Jörg Kachelmann in den ARD-Wetternachrichten am 10.9.2007 um 22:45 Uhr

zigartige Kombination ergeben sich vielseitige Chancen zum Dialog zwischen Industrie und Forschung sowie zur Vorbereitung einer industriellen Verwertung von Forschungsergebnissen. Einen ausführlichen Bericht vom edaWorkshop07 finden Sie auf den Seiten 22–31.

Das sicher bedeutendste EDA-Ereignis des vergangenen Quartals war die Design Automation Conference (DAC). In diesem Zusammenhang möchten wir Sie noch einmal darauf hinweisen, dass der am 25. Juli erschienene „edaTrend DAC“ in diesem Jahr für Mitglieder und Projektpartner der Ekompass-Projekte letztmalig kostenfrei verfügbar ist. Wir hoffen, dass Inhalte und Form Sie überzeugen.

Ein kurzes DAC-Fazit, sowie weitere Informationen zu den edaTrend-Berichten finden Sie auf Seite 34.

Neben den Mitarbeitern des edacentrum haben auch die Partner der Projekte PRODUKTIV+, SIDRA und LEONIDAS+ fleißig Berichte geschrieben, die Sie auf den Seiten 5–17 finden.

Schließlich möchten wir Sie noch auf das edaForum07 am 5. und 6. Dezember in München hinweisen, dessen interessantes Programm bereits feststeht und Ihnen in diesen Tagen per Post zugehen wird. Eine kurze Übersicht der Vortragenden finden Sie auf Seite 32–33.

Darüber hinaus enthält der newsletter edacentrum wie üblich EDA-Neuigkeiten von weiteren Ekompass-Projekten, den Mitgliedern und der weiten Welt. Viel Freude beim Lesen dieser Ausgabe wünscht Ihnen

Ralf Popp für das edacentrum

Informationen zu den „edaTrend“-Berichten zu DATE und DAC finden Sie auf S. 34 und unter [www.edacentrum.de/edatrend/](http://www.edacentrum.de/edatrend/)

## Was war:

**Abbildung 0.2:**

Impressionen von der DAC07 (S. 34)

**Abbildung 0.1:** Der erste edaWorkshop war ein voller Erfolg (S. 22)

Zunächst ist hier natürlich der zum ersten Mal veranstaltete edaWorkshop zu nennen. Bei dieser aus dem Ekompass-Workshop der Jahre 2002 bis 2006 hervorgegangenen Veranstaltung ist es gelungen, den Schwung und die Erfahrung der Vergangenheit mitzunehmen und eine neuartige Plattform für den Informationsaustausch zu schaffen: Der edaWorkshop ist dabei genauso ein wissenschaftlicher Workshop mit hohem Qualitätsanspruch geworden, wie eine Plattform zur Präsentation und zum Austausch von Forschungsergebnissen, die in öffentlich geförderten, industriellen Verbundprojekten erarbeitet werden. Durch diese ein-

**Abbildung 0.3:**

Fachlicher Austausch beim VeronA-Tutorial (S. 19)

Abbildung 0.02

Abbildung 0.03

Abbildung 0.04

Abbildung 0.05

**Abbildung 0.4:**

Entspannter Austausch auf dem edaWorkshop07 in Hannover (S. 22)

**Abbildung 0.5:**

Ergänzende Informationen zum newsletter edacentrum finden Sie unter [www.edacentrum.de/newsletter/](http://www.edacentrum.de/newsletter/)

# Inhaltsverzeichnis

**edaWorkshop 07**

Seite 05

**Projektspiegel**

**Projektbericht**

**PRODUKTIV+:**

**Referenzsystem zur**

**Messung der Produk-**

**tivität beim Entwurf**

**nanoelektronischer**

**Systeme**

PRODUKTIV+ ist ein F&E-Projekt, das sich von den anderen Projekten des Ekompass-Förderkomplexes abhebt – denn das Projekt hat sich die „Modellierung und Messung der Entwurfsproduktivität in der Halbleiterindustrie“ zum Ziel gesetzt. Keine leichte Aufgabe ... .

Seite 22

**edaVeranstaltung**

**edaWorkshop –**

**Der Start ist gegückt!**

Aus dem Ekompass-Workshop wurde in diesem Jahr der edaWorkshop. Lesen Sie die Zusammenfassung der Keynote- und Übersichtsvorträge und anderer wesentlicher Programmteile des edaWorkshop07. Erfahren Sie wichtige Details über die Teilnehmer des Kooperationsmarktes (S. 30). Und denken Sie schon jetzt an neue Beiträge für den edaWorkshop08. (Deadline wird der 18. Dezember 2007 sein).

Seite 32

**edaVeranstaltung**

**edaForum07**

Das Programm des am 6. und 7. Dezember in München stattfindenden edaForum07 steht fest. Während es in diesen Tagen verschickt wird, können Sie schon einmal „schnuppern“. Verschaffen Sie sich einen Überblick über die Votragenden und lesen Sie, welche Themen vorgestellt und diskutiert werden.

Seite 34

**edaTrend**

**Der „edaTrend DAC07“-Bericht ist für Mitglieder kostenlos**

Der „edaTrend DAC07“ ist am 25. Juli 2007 erschienen und berichtet umfassend von der diesjährigen DAC. An dieser Stelle sei noch einmal darauf hingewiesen, dass dieser Bericht den Mitgliedern des edacentrum e.V. in diesem Jahr letztmalig kostenlos als PDF-Datei zur Verfügung steht. Wie Sie den Bericht erhalten können, lesen Sie in diesem Beitrag.

**Überblick**

**Inhaltsverzeichnis**

Seite 03

**Projektspiegel**

**Abschlußbericht vom Projekt SIDRA**

Forschung zur Robustheit von ICs gegen elektrostatische Entladungen (ESD).

Seite 11

**Projektspiegel**

**Abschlußbericht vom Projekt LEONIDAS+**

Jüngste Ergebnisse beim leitbahnorientierten Entwurf applikationspezifischer Schaltungen.

Seite 15

**Projektspiegel**

**Nachrichten von den Projekten**

Meldungen der Ekompass-Projekte HERKULES, VeronA und VISION.

Seite 18

**Projektspiegel**

**Neues aus der EDA-Clusterforschung**

Neues von den Projekten AIS, FEST und SAMS.

Seite 20

**Neues aus dem edacentrum**

**Erfolgreiches edacentrum-Musterdepot**

Positive Entwicklung des Aktien-Musterdepots des edacentrum e.V.

Seite 20

**edaWorkshop 2007**

**edaMedaille 2007 an Udo Steinkopf**

Freuen Sie sich zusammen mit dem diesjährigen Preisträger und lesen Sie seine Laudatio.

Seite 29

**edaWorkshop 2007**

**Kooperationsmarkt schlägt wieder ein**

Unter dem Motto „Ideen suchen Abnehmer – Markt sucht Innovationen“ trafen sich zahlreiche Experten.

Seite 30

**EDA-Veranstaltung**

**Design Automation Conference**

Highlights von der diesjährigen DAC in San Diego, CA.

Seite 34

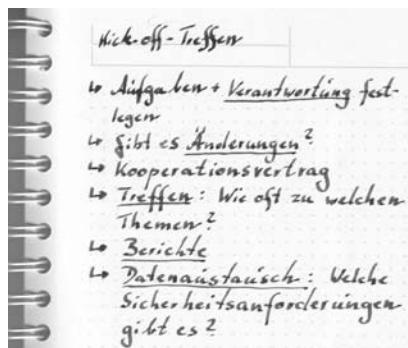

**Projektmanagement**

**Alex und Bill – Aufsetzen zum Kick-off**

Die Fortsetzungsgeschichte zum Projektmanagement.

Seite 35

**Panorama**

**Meldungen aus der EDA-Welt**

Eine EDA-Rückschau auf die vergangenen Monate mit dem „Pressescan“ im newsletter edacentrum.

Seite 39

**Panorama**

**Meldungen aus dem Ausland**

Neue interessante Nachrichten haben Si2, ENIAC und AENEAS zu vermelden.

Seite 41

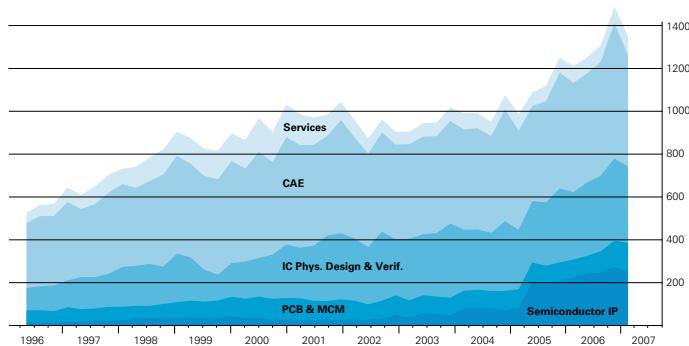

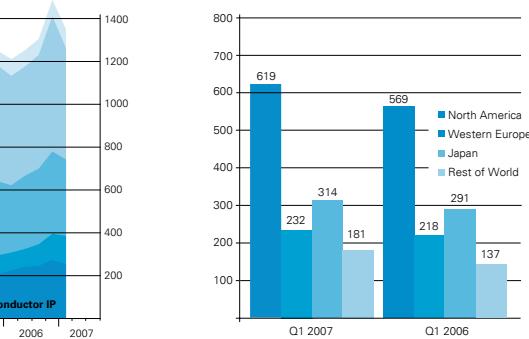

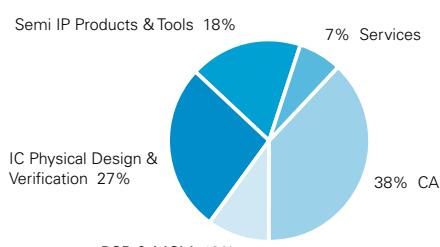

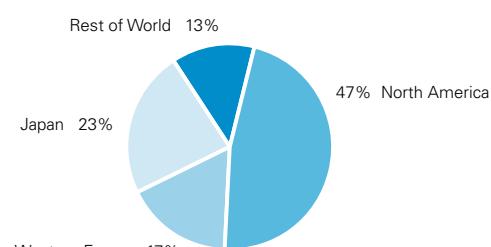

**Marktbeobachtung**

**10% EDA-industry revenue growth in Q1/2007**

Entwicklung der aktuellen Umsatzzahlen im Bereich EDA.

Seite 42

**Neues von den Mitgliedern**

**Portraits und Neuigkeiten unserer Mitgliedsfirmen**

Mitgliedsfirmen stellen sich und neue Produkte vor.

Seite 43

**Ausblick**

**Vorschau auf die kommende Ausgabe**

Seite 47

# 1 Projektspiegel

## Der Ekompass-Förderkomplex

[www.edacentrum.de/ekompass](http://www.edacentrum.de/ekompass)

Die zur Zeit vom edacentrum betreuten Projekte gehören zu dem vom Bundesministerium für Bildung und Forschung (BMBF) zur Stimulation von EDA-Forschungsaktivitäten eingerichteten Förderkomplex namens Ekompass. Ekompass steht für „Entwurfsplattformen für komplexe angewandte Systeme und Schaltungen der Mikroelektronik“. Mit diesem Förderkomplex will das BMBF in erster Linie dazu beitragen, die einer starken internationalen Konkurrenz ausgesetzten Arbeitsplätze in der System- und Halbleiterindustrie sowie im EDA-Umfeld zu erhalten und auszubauen.

Ziel ist es, durch ein gemeinsames Vorgehen von Industrie, Forschung und öffentlicher Hand, in den für Deutschland (und für Europa) wichtigen Bereichen neue Entwurfsmethoden zu entwickeln, um die Komplexität zukünftiger Chipsysteme qualitätsgerecht und

effektiv beherrschen zu können. Dabei wird der Fokus auf solche Themen gelegt, denen für die Wettbewerbsfähigkeit der deutschen Industrie die größte Bedeutung zukommt.

Der Förderkomplex Ekompass ist nicht nur von nationaler Bedeutung. Die meisten Forschungsvorhaben haben ein internationales Umfeld, insbesondere auf europäischer Ebene, wo Synergien aus gemeinsamen Stärken entstehen. Die für Ekompass sehr wichtige europäische Zusammenarbeit wird auch dadurch transparent, dass einige der Ekompass-Projekte in MEDEA+ Projekte eingebettet sind.

Der Newsletter des edacentrum berichtet in loser Folge über die Projekte des Ekompass-Förderkomplexes.

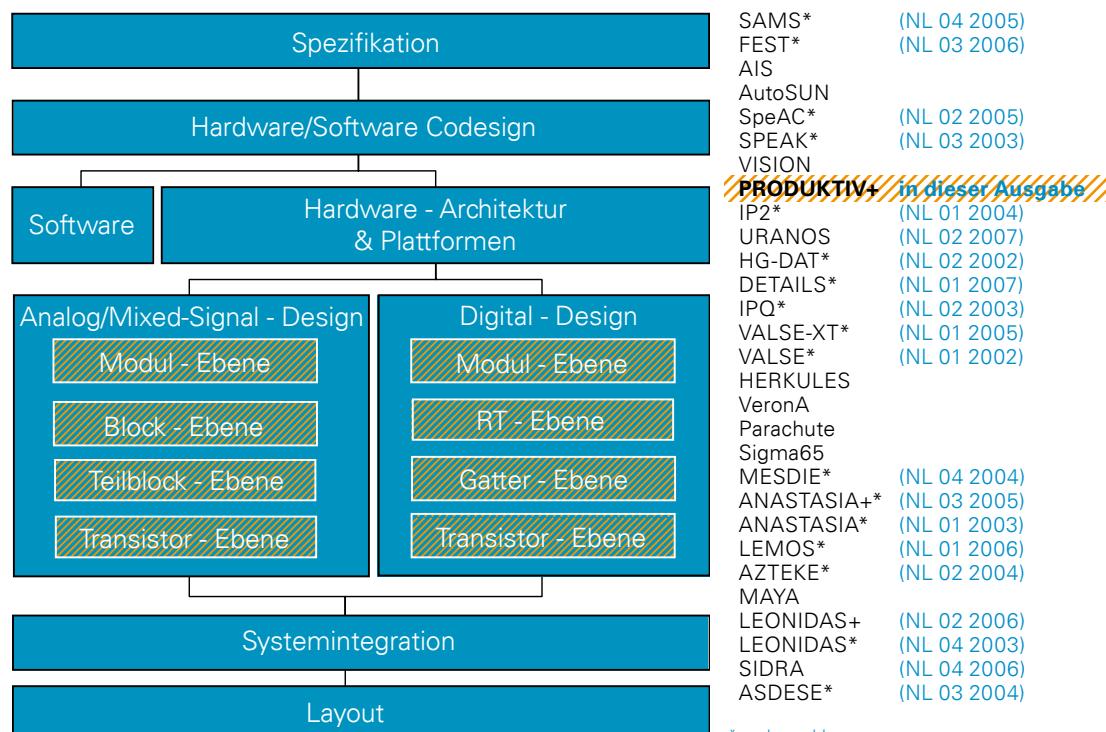

**Abbildung 1.01:**

Übersicht über die aktuellen

Ekompass-Projekte.

| Projekt    | FKZ     | Laufzeit                | Projektkoordination                                             |

|------------|---------|-------------------------|-----------------------------------------------------------------|

| AIS        | 01M3083 | 01.12.2006 – 30.11.2009 | Dr. Volker Schöber, schoeber@edacentrum.de                      |

| AutoSUN    | 01M3178 | 01.07.2007 – 30.06.2010 | Dr. Daniel Baumeister,<br>daniel.baumeister@contiautomotive.com |

| MAYA       | 01M3172 | 01.06.2006 – 31.05.2009 | Dr. Sebastian Sattler, sebastian.sattler@infineon.com           |

| Parachute  | 01M3169 | 01.04.2006 – 31.03.2009 | Thomas Steinecke, thomas.steinecke@infineon.com                 |

| PRODUKTIV+ | 01M3077 | 01.10.2005 – 30.09.2008 | Frank Badstübner, frank.badstuebner@infineon.com                |

| Sigma65    | 01M3080 | 01.10.2006 – 30.09.2009 | Dr. Manfred W. Dietrich, manfred.dietrich@eas.iis.fhg.de        |

| URANOS     | 01M3075 | 01.07.2005 – 30.06.2008 | Dr. Hans-Jürgen Brand, hans-juergen.brand@amd.com               |

| VeronA     | 01M3079 | 01.06.2006 – 31.05.2009 | Peter Jores, peter.jores@de.bosch.com                           |

| VISION     | 01M3078 | 01.05.2006 – 30.04.2009 | Dr. Joachim Gerlach, joachim.gerlach@de.bosch.com               |

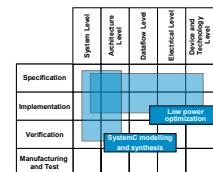

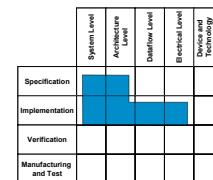

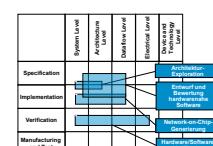

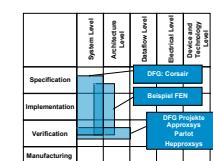

**Abbildung 1.02:**

Das Bild zeigt verschiedene Entwurfsvorgänge des Schaltungsentwurfs. Dabei sind die Schwerpunkte des Projektes PRODUKTIV+ hervorgehoben, weil sich das Projekt PRODUKTIV+ in dieser Ausgabe des Newsletters präsentiert.

\* = abgeschlossen

# PRODUKTIV+: Messung der Produktivität beim Entwurf nanoelektronischer Systeme

Ein Meßsystem für die Wirksamkeit von Electronic Design Automation

J. Alt<sup>1</sup>, F. Badstübner<sup>1</sup>, H.-J. Brand<sup>2</sup>, E. Jentzsch<sup>3</sup>, C. Sebeke<sup>4</sup>, A. Vörg<sup>5</sup>

<sup>1</sup> Infineon Technologies AG, <sup>2</sup> AMD, <sup>3</sup> Cadence Design Systems GmbH, <sup>4</sup> Robert Bosch GmbH, <sup>5</sup> edacentrum GmbH

## PRODUKTIV+ – der Exot unter den F&E Projekten

Der Titel dieses Projektes und seine Inhalte klingen für langjährige Leser des Newsletters sicher etwas exotisch. Während die hier üblicherweise vorgestellten Projekte neue Verfahren erforschen, die den Entwurf nanoelektronischer Systeme verbessern, beschäftigt sich PRODUKTIV+ mit der Quantifizierung der Wirksamkeit von EDA-Maßnahmen. Denn erst die quantitative Messung ermöglicht die objektive Bewertung der Entwurfsproduktivität, die Simulation von Projekten zur Gewährleistung der Planungssicherheit und die wirksame Planung und Umsetzung von EDA-Maßnahmen.

Dafür hat das Projektkonsortium in PRODUKTIV+ die Einflussgrößen auf nanoelektronische Entwurfsprojekte in einem bisher einzigartigen Detaillierungsgrad modelliert. Hierbei werden nicht nur die technische Infrastruktur, wie EDA-Werkzeuge, Methodik und ihr Anwendungsbereich sowie Bibliotheken berücksichtigt, sondern auch der personelle Aufwand und die Fähigkeiten des Entwurftteams. Da in der Nanoelektronik Unikate entwickelt werden, ist die Beschreibung der für ein Produkt notwendigen Innovationen notwendig. Dies sind wirtschaftliche Randbedingungen wie Kosten, Projektlaufzeit und „time-to-market“ für die Quantifizierung sowie die Komplexität eines Projektes und die Qualität seiner Entwurfsartefakte für die Vergleichbarkeit einzigartiger Projekte. Alle diese Aspekte sind Bestandteile des in PRODUKTIV+ modellierten Designsystems. Auf Basis dieses Modells kann die Frage: „Was macht ein erfolgreiches Projekt aus?“ beantwortet werden. Dafür wurden basierend auf dem PRODUKTIV+-Modell Beziehungen zwischen technischen und finanziellen Kennzahlen hergestellt.

## PRODUKTIV+ kennt die Antwort – Wie technische Kennzahlen finanzielle Kennzahlen beeinflussen

Für Unternehmen, die mikro- oder nanoelektronische Systeme entwerfen, sind Investitionen in Electronic Design Automation (EDA) notwendig, um die gewünschten Produkte überhaupt zu ermöglichen. Modernste elektronische Systeme, z.B. aus der Automobilelektronik, der Kommunikation, der Medizin- und Sicherheitstechnik oder dem Unterhaltungssektor, wären ohne EDA nicht verfügbar. Diese ‚Enabling‘-Funktion von EDA ist unstrittig. Weiterhin ist ein positiver Zusammenhang zwischen Investitionen in Entwurfsautomatisierung und dem ROI

(return-on-investment) einer Firma belegt ([2], [3]).

Wenn es darum geht, festzulegen, wie viel EDA für ein bestimmtes Projekt oder eine Entwicklungsaufgabe notwendig ist, gibt es keine eindeutigen Antworten. Für Investitionen in EDA lässt sich bis heute der ROI nicht angeben. Das bedeutet auch, dass die Leistungen, die Innovationen einzelner Ekompass-Projekte für den Entwurf nanoelektronischer Systeme bei steuern, sich bisher nicht objektiv quantifizieren lassen.

Hier wird PRODUKTIV+ Abhilfe schaffen. Mit den Ergebnissen aus PRODUKTIV+ wird es möglich sein, komplexe Fragen wie die Folgenden quantitativ zu beantworten:

- » Der Standort im Billiglohnland hat niedrigere Stundensätze. Um welchen Faktor muss meine Produktivität höher sein, um meine höheren Stundensätze zu rechtfertigen?

- » Welche und wie viele Ressourcen muss ich einsetzen, um mein Produkt optimal am Markt zu platzieren?

- » Wie kann ich die Produktivität ermitteln, auch wenn jedes Arbeitsergebnis ein Unikat ist und die statistische Basis zur Ermittlung eher gering ist?

- » Wie viel EDA ist zur Durchführung eines Projekts notwendig?

- » Welche Parameter im Designsysten müssen geändert werden, um ein Projekt zum Erfolg zu führen?

- » Lässt sich ein Projekt erfolgreich abschließen?

- » Welche Produktivität hat(te) ein Projekt?

- » Warum hat(te) das Projekt eine zu niedrige Produktivität?

- » Wie hat sich die Produktivität durch eine Maßnahme im Designsysten verändert?

Die Hauptrolle zur Beantwortung dieser Fragen spielt die Produktivität. So wie in der Fertigung Investitionen in Automatisierungsanlagen die Produktivität der eingesetzten Arbeitskräfte erhöhen, so erhöhen EDA-Investitionen die Produktivität der Schaltungsentwickler. Allerdings ist „Produktivität“ selbst ein vielfach verwendeter Begriff, der bisher nicht eindeutig definiert ist. Er dient unter anderem innerhalb einer Firma zum Vergleich von Einheiten (z.B. Fabrikationsstätten). Als Vergleich über die Zeit wird die Entwicklung der Produktivität gemessen. Einzelne Firmen, aber auch ganze Volkswirtschaften, nutzen die Produktivität zum

## Zusammensetzung des Projektkonsortiums:

### Projektpartner:

- » AMD Saxony LLC & Co. KG – DDC

- » Cadence Design Systems GmbH

- » Infineon Technologies AG

- » Robert Bosch GmbH

### Unterauftragnehmer:

- » Fraunhofer-IIS, EAS

- » Friedrich-Schiller-Universität Jena

- » OFFIS e.V. – Institut für Informatik

- » Leibniz Universität Hannover – IMS

- » Eberhard Karls Universität Tübingen – (TI)

### Förderkennzeichen

01 M 3077

### Laufzeit des Vorhabens:

01.10.2005–30.09.2008

### Homepage:

[www.edacentrum.de/prodktiv+/-](http://www.edacentrum.de/prodktiv+/)

Vergleich untereinander. Die Firma Numetrics ist für den Bereich des Schaltungsentwurfs auf diese Art des Benchmarkings spezialisiert [4]. Für die genannten Vergleiche wird die Produktivität stark abstrahiert, z. B. in Fahrzeuge pro Tag oder auch Transistoren pro Designer und Jahr.

Zur Beantwortung der zuvor gestellten Fragen ist die Aussagekraft dieser abstrakten Darstellungen nicht ausreichend. Beispielsweise bleiben Komplexität und Qualität der Entwurfsartefakte bei diesen abstrakten Ansätzen unberücksichtigt, so dass ein Vergleich basierend auf Transistoren zwischen Analog- und Digital-Entwürfen unweigerlich falsche Informationen liefert. Zur gezielten Verbesserung des Entwicklungsprozesses durch, z. B. EDA-Maßnahmen, oder zur Optimierung der Projektsteuerung sind detaillierte Messungen und Analysen notwendig. Diese Zusammenhänge wurden bereits im Projektkurzbericht über PRODUKTIV+ dargestellt [1].

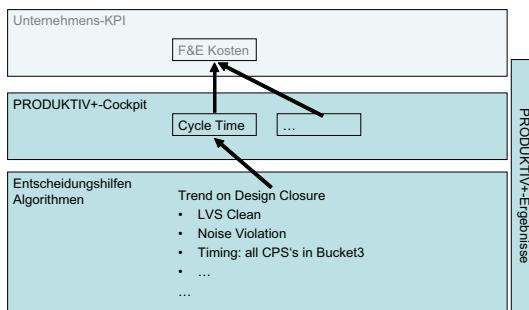

Zur Steuerung eines Unternehmens ist die Reduktion der Produktivität auf eine einzelne Kennzahl wenig geeignet. Hierzu haben sich in den letzten Jahren KPI-Systeme (engl. Key Performance Indicators) etabliert. Ein KPI-System wird auch als „Management-Cockpit“ bezeichnet, das regelmäßig aktuelle Werte über den internen Zustand des Unternehmens liefert. Auf der Basis des entwickelten Modells des Designsystems stellt PRODUKTIV+ die zur Planung, Beobachtung und Steuerung von Entwurfsprojekten abstrakten Aspekte durch aussagekräftige KPI dar. Von PRODUKTIV+ dürfen Entscheidungshilfen und Algorithmen zur objektiven Darstellung der KPI erwartet werden. So wie die Messinstrumente im Cockpit eines Flugzeugs den Piloten und seine Crew in die Lage versetzen, das Flugzeug schnell und sicher ans Ziel zu bringen, wird das „PRODUKTIV+ Cockpit“ durch die Anzeige der relevanten KPI EDA-Entscheider, Projektverantwortliche und das Management in die Lage versetzen, Projekte mit hoher Planungssicherheit und Wirksamkeit durchzuführen (Abbildung 1.03).

Abbildung 1.03: PRODUKTIV+ KPI-Cockpit

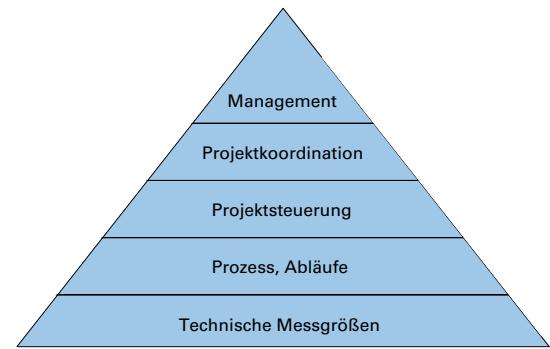

Abbildung 1.04 zeigt verschiedene Ebenen eines Unternehmens von den technischen Messgrößen bis hinauf

zum Management, in denen KPI definiert sind. So geben KPI unter anderem Auskunft über die Leistungsfähigkeit einer Abteilung, eines Entwicklungs- oder Logistikprozesses. Naturgemäß abstrahieren die Ebenen in Richtung Management mehr von technischen hin zu finanziellen KPI.

Abbildung 1.04: Ebenen für KPI's (Quelle: IFX, OFFIS)

Wesentlich für den Erfolg eines Unternehmens ist es, den Zusammenhang zwischen den technischen und finanziellen Kenngrößen möglichst exakt zu kennen. So gliedert sich der Umsatz für ein Produkt, einen Unternehmensbereich oder das gesamte Unternehmen auf in Gewinn (hoffentlich) und Kosten (unvermeidlich). Die Kosten wiederum sind aufgeteilt in:

- » Allgemeine Verwaltungskosten

- » Vertriebskosten

- » Entwicklungskosten

- » Herstellkosten

Für die Betrachtung des Einflusses von EDA auf die finanzielle Leistungsfähigkeit kommen die Entwicklungs- und Herstellkosten in Frage. Die Entwicklungskosten sind dabei unabhängig von der Anzahl der hergestellten Produkte. Die Herstellkosten umfassen die zur Produktion eines Stücks notwendigen Kosten wie Material oder Arbeitskraft und sind somit abhängig von der gefertigten Stückzahl. Die Laufzeit eines EDA-Werkzeugs oder der Aufwand für einen Designschnitt tragen zur Projektdauer und damit zu den Kosten eines Projektes bei. Insbesondere werden die Entwicklungskosten durch EDA beeinflusst. Die Projektlaufzeit hat auch Auswirkungen auf den Umsatz, der mit einem Produkt erreicht werden kann (time-to-market). Ein EDA-Werkzeug zur automatischen Layoutgenerierung hat signifikanten Einfluss auf die Chipfläche und die verwendeten Maskenebenen. Damit sind auch die Herstellkosten von der Leistungsfähigkeit einzelner EDA-Werkzeuge beeinflusst. Somit können Wirkungsketten von technischen Kenngrößen des Designsystems hin zu finanziellen Kenngrößen wie Umsatz, Entwicklungs- und Herstellkosten aufgestellt werden.

Dieser kurze Einblick in die Zusammenhänge soll genügen, um den Einfluss von EDA auf finanzielle KPI zu verstehen. Tatsächlich sind die Zusammenhänge und Einflüsse auf die KPI, die im PRODUKTIV+-Modell des Designsystems erfasst sind, viel komplexer.

Das kontinuierliche Beobachten der KPI erlaubt der Projektsteuerung:

- » das Überwachen und Verbessern des Entwicklungsprozesses,

- » das Überprüfen der finanziellen Zielgrößen des Projektes/Produktes,

- » eine gezielte Modifikation des Ressourceneinsatzes für einzelne Entwicklungsprojekte.

Abbildung 1.05 zeigt schematisch die Abbildung der technischen KPI über das PRODUKTIV+-Cockpit auf die vorhandenen Unternehmens-KPI.

**Abbildung 1.05:** Ableitung der Unternehmens-KPI aus dem PRODUKTIV+-Cockpit (Quelle: edacentrum)

In den folgenden Abschnitten wird die Modellierung des Designsystems und die automatisierte Datenerfassung beschrieben. Diese erfolgreich abgeschlossenen Aktivitäten sind die Voraussetzung für die weitere Entwicklung der Analyse- und Prognoseverfahren mit Data-Mining und simulativen Verfahren und deren Validierung mittels prototypischer Implementierungen bei den Partnern im industriellen Umfeld.

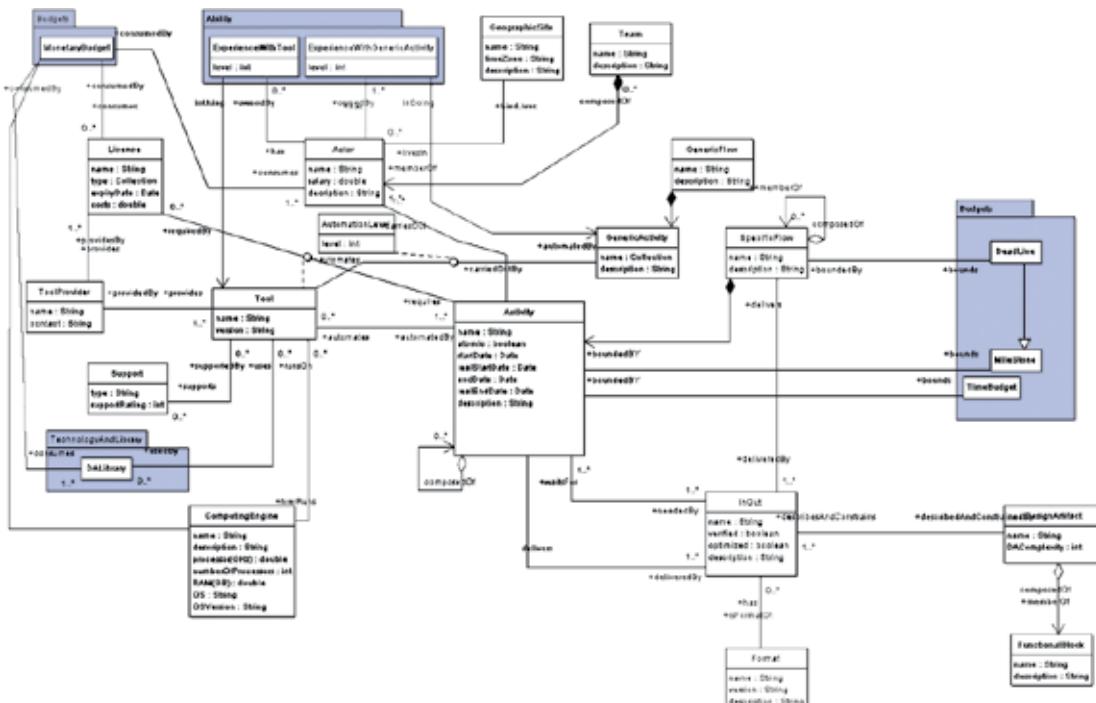

## Modellierung des Designsystems

Die Modellierung des Designsystems ist die theoretische und formale Grundlage für die Bestimmung der Produktivität eines Designsystems. Hierfür haben alle Partner und Unterauftragnehmer ein gemeinsames Modell entwickelt sowie Datenformate, Metriken und Messvorschriften spezifiziert. Als Werkzeug wird hierfür das aus der Informatik stammende Ontologiekonzept benutzt. Unter einer Ontologie versteht man in der Informatik im Bereich der Wissensrepräsentation ein formal definiertes System von Konzepten und Relationen. Zusätzlich können Ontologien Inferenz- und Integritätsregeln enthalten.

Die Entwicklung der gemeinsamen Ontologie ist abgeschlossen. Alle Partner waren mit ihren Unterauftragnehmern hieran entsprechend ihrer Kompetenz beteiligt. Robert Bosch hat die Modellierung der Komplexität im Analog- & Digitaldesign in die Projektkomplexität eingebettet. Infineon Technologies hat den Bereich Ressourcen und Design Flow bearbeitet. Cadence Design Systems entwickelte u.a. die initialen Modelle für die Designartefaktqualität und die Fähigkeiten der Designer. AMD hat das initiale Kennzahlensystem aufgebaut.

Aufgrund der Komplexität der Zusammenhänge kann an dieser Stelle lediglich die oberste, abstrakte Ebene des Designsystem-Modells (Ontologie) dargestellt werden (Abbildung 1.06).

UML (Unified Modelling Language) Beschreibungen des Modells dienen der Visualisierung. Für die formale Ontologie-Beschreibung des Designsystem-Modells

**Abbildung 1.06:** PRODUKTIV+ Ontologie – Top-Level (Quelle: CDNS, IMS, OFFIS)

verwendet PRODUKTIV+ die Ontology Web Language (OWL) [14]. Aufgrund der Verwendung beider Beschreibungssprachen wurden Konzepte entwickelt, wie die UML- und OWL-Modelle aufeinander abgebildet werden.

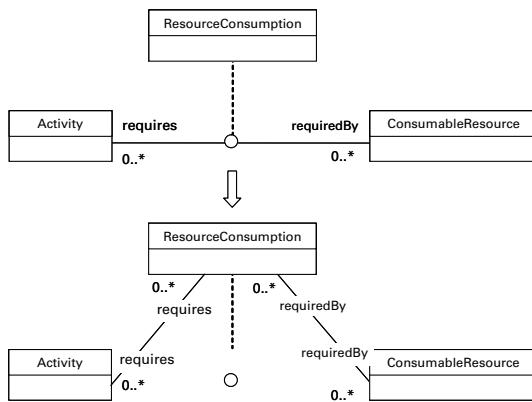

Abbildung 1.07 zeigt ein Beispiel der UML-nach-OWL-Umsetzung anhand einer UML-Assoziationsklasse.

Eine Assoziationsklasse beschreibt eine Beziehung zwischen zwei UML-Klassen (z.B. `Activity` und `ConsumableResource`). Ein solches Sprachkonstrukt existiert in OWL nicht. Daher wird das Konstrukt in eine OWL-Standardklasse mit zusätzlichen Object Properties umgesetzt. (Abbildung 1.07 unten)

**Abbildung 1.07:** Umsetzung von UML- nach OWL-Klassen

(Quelle: IMS)

Obwohl die grundlegenden Modellierungsaufwände am Anfang des Projektes geleistet wurden, wird die Ontologie kontinuierlich über die Projektlaufzeit weiter gepflegt. Dies stellt sicher, dass neue Erkenntnisse aus den nachfolgenden Arbeiten in die Modellierung einfließen.

### Datenerfassung

Die Datenerfassung zur Extraktion der in der Modellierungsphase als relevant identifizierten Parameter aus dem Designsystem basiert auf dem zuvor dargestellten Ontologiemodell. Die Bausteine der Datenerfassung können wie folgt kategorisiert werden:

- » Technische Design-Daten (z. B. Clock-Skew, Fläche Metalllagen)

- » Nutzungsdauer der Werkzeuge (Aufwand für Setup, Lizenznutzung, Aufwand für Auswertung)

- » Betriebswirtschaftliche Daten (Lizenzkosten, Nutzungskosten für Rechner, Personalkosten)

In industriellen Entwicklungsorganisationen werden die Daten mit unterschiedlichen Systemen erfasst. Insbesondere existiert keine Verbindung zwischen betriebswirtschaftlichen und technischen Daten. Die Daten der Kategorie Laufzeiten existieren in Logfiles von Werkzeugen oder IT-Systemen.

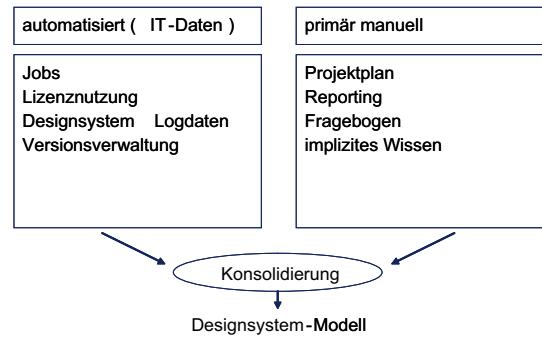

Die Abbildung 1.08 zeigt schematisch einen Auszug der verschiedenen, in PRODUKTIV+ genutzten Daten-

quellen. Unter anderem die Datenquellen zur Erfassung der Eingangsgrößen zur Berechnung des unten unter „Analyse- und Prognoseverfahren“ dargestellten Beispiels „Trend on Design Closure“ (Designsystem Logdaten). Dabei steht die automatisierte Erfassung von Daten im Mittelpunkt.

**Abbildung 1.08:** Prinzip der Datenerfassung (Quelle: IFX)

Wesentliche Quellen für technische Daten des Designsystems sind

- » Logdaten aus der Load-Sharing Facility (LSF) (Laufzeit des Jobs, Speicher- und CPU-Bedarf)

- » Lizenzdaten (Dauer der Lizenznutzung)

- » Report-Files der verwendeten EDA-Werkzeuge (z. B. Synthese-Timing (CPS), LVS, Noise Violation)

Zumindest innerhalb einer Firma sind die Formate für LSF und Lizenz-Logdaten wohl definiert. Inhalt und Format der Report-Files von EDA-Werkzeugen weisen allerdings kein einheitliches Muster auf. Hier kann der Nutzer üblicherweise festlegen, welche Daten im Report enthalten sein sollen. Auch können neue Werkzeug-Versionen zu einer Änderung des Formats führen.

Im Rahmen von PRODUKTIV+ wurde ein flexibler Daten-Extraktor entwickelt, der als sinnvolle Ergänzung für industrielle Design-Flows die gewünschten Daten extrahieren kann. Hier kann bei der Integration von EDA-Werkzeugen in den Design-Flow durch entsprechendes Skripting sichergestellt werden, dass zu bestimmten Designschritten Daten erfasst und in eine zentrale, firmeninterne Datenbank geschrieben werden.

### Analyse- und Prognoseverfahren

Bei der Entwicklung der auf den erfassten Daten aufbauenden Analyse und Prognoseverfahren werden von den Partnern parallele Ansätze verfolgt, deren Genauigkeit und Aussagekraft in der Validierungsphase von PRODUKTIV+ verglichen werden (Best-in-Class-Ansatz). In PRODUKTIV+ wird zwischen Analyseverfahren für abgeschlossene Projekte, also basierend auf realen Projektdaten, und Simulationsverfahren zur Prognose basierend auf historischen Projektdaten unterschieden. Auf den Status beider noch in der Entwicklung befindlichen Verfahren wird im Folgenden eingegangen.

## Analyse

In der Modellierungsphase von PRODUKTIV+ wurden 49 Eingangsparameter ermittelt, die zur Komplexität einer Entwicklungsaufgabe beitragen. 16 Parameter davon erscheinen signifikant und mit vertretbarem Aufwand ermittelbar. Dadurch konnte mit den ursprünglich geplanten Methoden kein funktionaler Zusammenhang ermittelt werden, da die dafür mindestens erforderlichen mehr als 250 kompletten Datensätze nicht zur Verfügung stehen. Zur Lösung dieses Problems werden zwei Ansätze verfolgt:

- » Die 49 Eingangsparameter zur Bestimmung der Komplexität können den Klassen: Fläche, Funktion, Timing, Performance, Leistung, Entwicklungstechnologie und Kommunikation zugeordnet werden. Unter der Annahme, dass eine Linearkombination dieser Klassen im Bezug auf den Entwicklungsaufwand existiert, können Subnetze identifiziert und trainiert werden. Damit sinkt die Anzahl der erforderlichen vollständigen Parametersätze.

- » Die Komplexität der Entwicklungsaufgabe wird für eindeutig identifizierbare Bereiche ermittelt, z. B. für das Layout eines digitalen Schaltungsteils. Dort liegen auch weitgehend vollständige Datensätze vor, die zwar als Vereinigungsmenge etwa 49 Eingangsparameter umfassen, in den Teilbereichen wie oben jedoch wesentlich dünner besetzt sind. Die Gesamtkomplexität der Entwicklungsaufgabe ergibt sich auch hier aus der Kombination aller Komplexitätsfunktionen. Da die Abfolge, Parallelität, und Abhängigkeit der Arbeiten durch die internen Prozesse festliegt, besteht die Erwartung, dass die Kombination zu einer Gesamtkomplexität möglich wird.

## Simulation

Es liegen erste Lösungsansätze vor, die in Kombination ein PRODUKTIV+-Gesamtsimulationssystem ermöglichen. Die Basis ist das PRODUKTIV+-Modell des Designsystems. Um dieses mit Leben zu füllen, wird von der Ontologie eine Instanz gebildet. Hierfür existieren bereits Prototypen, welche die komplexen Zusammenhänge innerhalb eines konkreten (firmenspezifischen) Designsystems darstellen und nur die relevanten Parameter zur Auswahl stellen. Erste Erfolge verzeichnet das Konsortium auch bei der Visualisierung der Ergebnisse, sowie der Einbettung von verschiedenen Berechnungs- und Einzelsimulationsmethoden. Für die Simulation werden drei Verfahren angewandt:

- » Der Design Project Character (DPC, Gesamtkomplexität der Designaufgabe) verfolgt eine schnelle, geschlossene und gesamthafte Berechnung der Entwicklungsaufgabe.

- » Petri-Netze, erweitert um eine Zeitkomponente, mit verschiedenen Marken und Konfliktlösungspotential stellen den zeitlichen Aspekt detailliert dar.

- » Ein Multi-Agentensystem, bestehend aus einer Gruppe individueller virtueller Agenten, die kollektiv ein Problem lösen, wird zur Simulation und

Optimierung eingesetzt. In PRODUKTIV+ wird ein Multiagentensystem eingesetzt, das Rollenbeschreibungen unterstützt und somit in der Lage ist, sich selbst zu regeln.

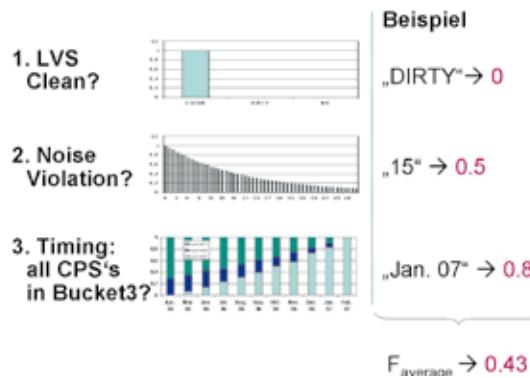

Ein bereits abgeschlossener PRODUKTIV+-Beitrag hat den Einfluss der technischen Kenngrößen des Designsystems, die unter anderem während der Synthese im Schaltungsentwurf erfasst werden, auf die Projektlaufzeit und damit einen Beitrag zu den finanziellen KPI eines Unternehmens dargestellt. Diese Darstellung ist Voraussetzung für die Beobachtung und Steuerung von Entwicklungsprozessen. Damit wird z. B. ein Projektleiter in die Lage versetzt, einzelne Designschritte kontinuierlich zu beobachten. So wird er durch diese Beobachtung in die Lage versetzt, ggf. Maßnahmen wie Prozess-Parallelisierung zu verwenden, um den gegebenen Zeitrahmen einzuhalten. Ein Beispiel ist in Abbildung 1.09 gegeben.

**Abbildung 1.09:** Beispiele für Entscheidungshilfen bzw. Algorithmen

(Quelle: AMD)

Erläuterungen zu Abbildung 1.09:

### LVS (Layout vs. Schematic)

Suche nach Unterschieden zwischen Transistor-Level-Schaltplan und Layout. Beispielsweise könnte der Fehler auftreten, dass Pins im Layout anders als die im Schaltplan verknüpft sind.

### Noise Violation (Signalstörung)

Beispiel: Die Potentialänderung der Leitung A hat zu großen Einfluss auf die parallel verlaufende Leitung B, so dass Schaltfehler im Netz der Leitung B entstehen.

### Timing

Einordnung des Critical Path Slack (CPS) in diskrete Wertebereiche (Buckets).

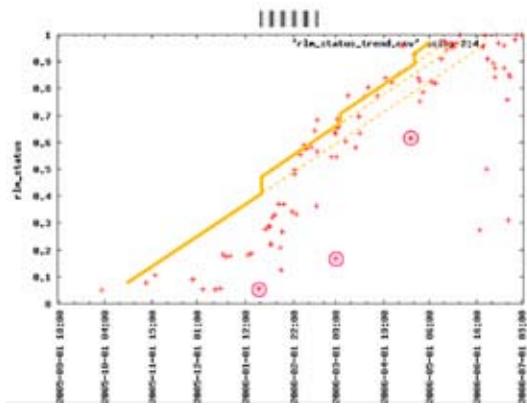

Grafisch sind in Abbildung 1.09 die Funktionen zur Bewertung von 3 technischen KPI „LVS Clean“, „Noise Violation“ und „Timing“ dargestellt. Die abgelesenen Werte werden in einer initial sehr einfach gehaltenen Gewichtungsfunktion Faverage, die das arithmetische Mittel über die Funktionswerte bildet, zu einem Bewertungsfaktor zur Ermittlung der Projektdauer (Design Closure) zusammengefasst. Der so prognostizierte Zeitverlauf ist in Abbildung 1.10 dargestellt.

**Abbildung 1.10:** PRODUKTIV+ Cockpit Einflussgröße – Trend on Design Closure (Quelle: AMD)

Die Knicke im Zusammenhang mit den markierten „Ausreißern“ im Zeitverlauf geben in der Analysephase Hinweise auf potentielle Störgrößen im Designsysteem, die durch Back-Annotation auf die technischen Messgrößen in den Log-Dateien gezielt zur Optimierung des Designsysteams eingesetzt werden.

### Validierung

Nach Abschluss der Arbeiten an den „Analyse- und Prognoseverfahren“ schließt sich eine Validierungsphase an. Die erarbeiteten Analyse- und Simulationsverfahren werden dann zu einem durchgängigen Flow zusammengefasst bzw. die Genauigkeit der Verfahren verglichen. Dabei wird davon ausgegangen, dass das entstehende System partnerspezifische Ausprägungen aufweisen wird. Ziel ist die Entwicklung eines umfassenden Referenzsystems, das standardisiert werden kann.

### Zusammenfassung

Das Projekt PRODUKTIV+ ist auf einem guten Weg, einen signifikanten Beitrag zur Transparenz des Wertes von EDA im Entwicklungsprozess für integrierte Schaltungen zu leisten. Die noch verbliebene Zeit wird insbesondere dazu genutzt werden, die Verfahren zur Analyse und Simulation prototypisch weiterzuentwickeln, einzusetzen und dadurch an realen Projekten zu validieren. Die so gewonnenen Erkenntnisse aus dem praktischen Einsatz dienen der Verfahrensoptimierung. Möglicherweise erfolgt während der Validierung eine Anpassung der Ontologie. Da Simulation und Analyse auf automatisierten Instanziierungsverfahren der Ontologie beruhen, sind keine Schwierigkeiten aufgrund von Modelländerungen zu erwarten.

#### Kontakt (PRODUKTIV+):

##### Projektkoordination:

Infineon Technologies AG

Frank Badstübner

fon (0 89) 2 34 - 2 31 41

frank.badstuebner@infineon.com

##### Projektmanagement:

edacentrum GmbH

Dr. Andreas Vörg

fon (05 11) 7 62 - 1 96 86

voerg@edacentrum.de

relevanter wirtschaftlicher Daten (z. B. ROI) durch die angestrebte Quantifizierung getroffen werden.

### Referenzen

- [1] Jürgen Alt, Andreas Vörg: „PRODUKTIV+: Referenzsystem zur Messung der Produktivität beim Entwurf nanoelektronischer Systeme“ (Projektkurzbericht), newsletter edacentrum, Ausgabe 01 2006, S. 10 ff, <http://www.edacentrum.de/projekte/files/prodktiv+-pkb-012006.pdf>

- [2] International Business Strategies, Inc: „Analysis of the Relationship Between EDA Expenditures and Competitive Positioning of IC Vendors for 2003“ (Handel Jones Report), 2004, interner Bericht für edacentrum Mitglieder, [https://secure.edacentrum.de/mitglieder\\_intern/handel\\_jones\\_reports.html](https://secure.edacentrum.de/mitglieder_intern/handel_jones_reports.html).

- [3] International Business Strategies, Inc: „Analysis of the Relationship Between EDA Expenditures and Competitive Positioning of IC Vendors“ (Handel Jones Report), 2002, interner Bericht für edacentrum Mitglieder, [https://secure.edacentrum.de/mitglieder\\_intern/handel\\_jones\\_reports.html](https://secure.edacentrum.de/mitglieder_intern/handel_jones_reports.html).

- [4] Numetrics, Homepage <http://www.numetrics.com>

- [5] Richard Sohnus, Eyck Jentzsch, Wolf-Ekkehard Matzke: „Holonic Simulation of a Design System for Performance Analysis, IEEE HoloMAS 2007 – 3rd International Conference on Industrial Applications of Holonic and Multi-Agent Systems in Regensburg, Deutschland, September 2007

- [6] Peter van Staa, Christian Sebeke: „Can Multi-Agents wake us from IC design productivity nightmare?“ (Keynote), IEEE HoloMAS 2007 – 3rd International Conference on Industrial Applications of Holonic and Multi-Agent Systems in Regensburg, Deutschland, September 2007

- [7] Vadim Ermolayev, Wolf-Ekkehard Matzke: „Towards Industrial Strength – Business Performance Management“, IEEE HoloMAS 2007 – 3rd International Conference on Industrial Applications of Holonic and Multi-Agent Systems in Regensburg, Deutschland, September 2007

- [8] Neele Hinrichs, Peter Leppelt, Erich Barke: „Building up a Performance Measurement System to Determine Productivity Metrics of Semiconductor Design Projects“, IEMC 2007 – 19th International Engineering Management Conference, GOLD track in Austin, Texas/USA, Juli 2007

- [9] Stefan Häusler (OFFIS), Frank Poppen, Sonja Preis (OFFIS), Kevin Hausmann (OFFIS), Wolfgang Nebel (OFFIS, Uni Oldenburg), Axel Hahn (OFFIS, Uni Oldenburg), Peter Leppelt (IMS), Amir Hassine (IMS), Erich Barke (IMS): „Modellierung von Kom-

plexität und Qualität als Faktoren von Produktivität in Design-Flows für integrierte Schaltungen”, eda-Workshop in Hannover, Deutschland, Juni 2007

[10] Richard Sohnies, Vadim Ermolayev, Eyck Jentzsch, Wolf-Ekkehard Matzke: „An Approach for Assessing Design Systems: Design System Simulation and Analysis for Performance Assessment”, 9th International Conference on Enterprise Information Systems in Funchal, Madeira – Portugal, Juni 2007

[11] Jürgen Alt: „Die Produktivität von Entwicklungsprojekten wird messbar”, Markt&Technik, Ausgabe 10 in Magazin, 9. März 2007

[12] Amir Hassine, Markus Olbrich, Erich Barke: „Computer Aided HRM for the Semiconductor Industry: Limits and Perspectives”, Asian Pacific Industrial Engineering and Management Systems Conference (APIEMS) in Bangkok/Thailand, Dezember 2007

[13] Peter Leppelt, Amir Hassine, Erich Barke: „An Approach to Make Semiconductor Design Projects Comparable”, Asian Pacific Industrial Engineering and Management Systems Conference (APIEMS) in Bangkok, Dezember 2007

[14] W3C: „Ontology Web Language (OWL)”, <http://www.w3.org/TR/owl-features/>

## SIDRA: Safe IC Design for Robust Applications

Von Petra Rose

**Das Projekt SIDRA wurde im Rahmen der BMBF-Förderinitiative Ekompass vom August 2004 bis zum Dezember 2006 gefördert. Technisches Ziel von SIDRA war es, Simulationsmethoden zu entwickeln, die es ermöglichen, präventiv Schwachstellen im Design festzustellen, um integrierte Schaltkreise (ICs) gegen die elektrostatische Zerstörung durch schnelle transiente Pulse nach dem Charge-Device-Modell (CDM: Pulse bis zu 10 A bei  $t < 2 \text{ ns}$ ) zu schützen. Dies ist notwendig, um für immer sensitivere Technologien die Anforderung an die Robustheit gegen elektrostatische Entladungen und gleichzeitig hohe Qualitätsanforderungen zu erfüllen.**

Wesentliche Ergebnisse der Arbeiten sind die Verbesserung der ESD-Schutzstrukturen sowie die Entwicklung der Simulations- und Messmethodik. Die steigende Qualität der ESD-Elemente hilft die Redesign-Wahrscheinlichkeit zu reduzieren und resultiert somit in einer Zeit- und damit Kostensparnis. Dadurch wird die Funktion zukünftiger, teils sicherheitskritischer Designs im Feld abgesichert.

Hauptergebnisse des SIDRA-Projektes umfassen u.a.:

- » die Entwicklung einer CDM-Simulationsmethodik zur präventiven Detektion von Schwachstellen im Design;

- » neu entwickelte Messmethoden, die in der Zukunft bei der Entwicklung und Charakterisierung von ESD-Schutzkonzepten und Produkten eingesetzt werden;

- » die Entwicklung eines Satzes freigaberelevanter Teststrukturen. Durch die Auswahl der Teststrukturen, basierend auf den Erkenntnissen in SIDRA, konnte die Testchipfläche deutlich reduziert werden;

- » Richtlinien für ein robustes und effizientes ESD-Layout.

Die erreichte Fachkompetenz ermöglicht eine bessere Konkurrenzfähigkeit hinsichtlich der Beratung externer

Foundry-Kunden. Zudem steigern die erzielten Fachkenntnisse in ESD-Fragen das Ansehen und die Konkurrenzfähigkeit der eigenen Produkte.

Neben der internen wurde auch die externe Verwertbarkeit vorbereitet. Dabei zielt die externe Verwertbarkeit in erster Linie auf die direkte Einflussnahme von ESD-Standardisierungsverfahren ab. Einige SIDRA-Partner sind Mitglieder in den Standardisierungsgremien der ESD Association (ANSI), JEDEC und IEC. Die wichtigsten aus SIDRA Themengebieten unterstützten Standardisierungsaktivitäten sind:

- » CDM-Charakterisierung (ESDA)

- » Transmission Line Pulsing (ESDA)

- » Transient Latch-up (ESDA)

- » ESD auf Systemebene (ESDA und IEC)

- Nachfolgend die Darstellung der Ergebnisschwerpunkte der deutschen SIDRA-Partner.

### Atmel Germany GmbH

Das SIDRA-Projekt gliederte sich für Atmel in zwei große Hauptschwerpunkte. Zum einen sollten im Teilbereich „Charakterisierung“ neue und bereits vorliegende ESD-Schutzstrukturen untersucht und weiterentwickelt werden. Zum anderen konzentrierte sich

Zusammensetzung des Projektkonsortiums:

**Partner:**

- » Atmel Germany GmbH

- » Infineon Technologies AG

- » Robert Bosch GmbH

- » X-Fab Semiconductor Foundries AG

**Unterauftragnehmer:**

- » Fraunhofer IZM München

- » FH Osnabrück

- » IMMS gGmbH

- » Melexis GmbH

**Europäische Projektpartner:**

- » ST Microelectronics (I)

- » Philips (NL)

- » TU Wien (A)

- » ETH Zürich (CH)

**Europäische Unterauftragnehmer:**

- » Synopsys (CH)

- » Universität Padua (I)

**Förderkennzeichen:**

01 M 3159

**Laufzeit des Vorhabens:**

01.08.2004–31.12.2006

der Teilbereich „Simulation“ auf die Einführung eines ESD-Bauelemente-Simulators, der für zukünftige Entwicklungsaufgaben auf Basis des hauseigenen 0.35 µm SmartPower SOI-Prozesses als wichtiges Werkzeug dienen wird.

Die im SIDRA-Projekt vermessenen Grundstrukturen, wie Dioden und Transistoren, zeigten schon von Beginn an eine hohe ESD-Festigkeit. Die bis dahin schon befriedigende bis gute Weitenskalierung der Elemente unter CDM-Stress konnte durch Maßnahmen wie z.B. Layoutanpassungen noch weiter verbessert werden. Mit Hilfe der gemeinschaftlich entwickelten Teststrukturen war es zudem möglich, weitere kritische Parameter wie die Anschlusswiderstände, das Gateoxid-Verhalten bei vf-TLP-Stress und den Aufbau eines Primär-Sekundär-Schutzes näher zu untersuchen und die Forschungsergebnisse in Entwicklungsrichtlinien einfließen zu lassen. Durch begleitende TIM-Messungen (Transient Interferometric Mapping) der TU Wien konnte zudem eine Schwachstelle im Metallanschluss der Basis-Diode festgestellt werden, was durch eine nachträgliche Bauelemente-Simulation bestätigt wurde. Aus diesen Erkenntnissen wurden Dioden mit wesentlich verbesserten Eigenschaften abgeleitet.

Eine ausführliche Aufgabenbeschreibung des SIDRA-Projektes finden Sie im newsletter edacentrum 04/2006.

Der während des Projektes noch mit relativ einfachen Basisstrukturen kalibrierte Bauelemente-Simulator lieferte auch bei weit komplexeren Strukturen gute bis sehr gute Übereinstimmungen mit der Messtechnik. Es konnte sowohl eine Parallelschaltung zweier Dioden, als auch eine komplexere Mehrfinger-Struktur eines ggNMOS-Transistors (grounded-gate NMOS) vollständig nachsimuliert werden. Untermauert wurden die Ergebnisse mittels der TIM-Messungen der TU Wien, so dass diese zu einem tieferen Verständnis der physikalischen Hintergründe des Schaltverhaltens und der Leistungsverteilung im Bauelement führten.

Zum Projektende lässt sich abschließend feststellen, dass das Potential von SOI auch im vieldiskutierten ESD-Bereich sehr hoch ist und mit den vorherrschenden Bulk-Technologien konkurrieren kann. Alle vermessenen Bauelemente zeigten überdurchschnittliche ESD-Festigkeiten. Mit dem im Projekt eingeführten ESD-Simulator steht nun auch ein wertvolles Tool zur Bauelemente-Entwicklung zur Verfügung, dessen Einsatz im Vorfeld einen großen Teil an Entwicklungsarbeit einsparen kann. Die aus dem Projekt abgeleiteten Erkenntnisse fließen als Komponente der zukünftigen Designmanuals direkt in hauseigene Richtlinien für ein robusteres ESD-Layout ein und dienen als Basis für interne Schulungen in der Schaltungsentwicklung.

Auf der Grundlage der erzielten Ergebnisse wird eine deutlich reduzierte Fehlerhäufigkeit in neuen Designs erwartet. Dieses wird zu Einsparungen von Redesigns bei internen Entwicklungsprojekten, sowie auch bei Kundendesigns im Foundry-Bereich führen.

## Robert BOSCH GmbH

Die Arbeit in AP 1 fokussierte sich auf die Evaluierung der neuen Charakterisierungsmethoden im CDM-Zeitbereich, die von Fraunhofer-IZM im Rahmen von SIDRA entwickelt wurden. Dies beinhaltet die Erprobung der ultra-fast TLP-Messtechnik (Pulse < 2 ns), der repetierenden Messmethode zur Analyse des transienten Verhaltens von ESD-Schutzstrukturen sowie Transient Latch-up Untersuchungen der SIDRA-Teststrukturen. Die Ergebnisse der Messungen waren die Grundlage sowohl für die Modifizierung und Kalibrierung der Bauelementmodelle als auch für die Definition der Ausfallkriterien bei zu hoher CDM-Belastung für die Schaltkreissimulation.

Der Fokus der Bosch-Aktivitäten im Arbeitspaket 2 war die Mixed-Mode-Device-Simulation von ESD-Eingangsschaltungen. Im Vergleich zu Einzelstrukturen ist die CDM-Device-Simulation von Schaltungen ein großer Schritt nach vorn auf dem Gebiet der ESD-Device-Simulation. Damit werden nicht nur Informationen über das CDM-Entladeverhalten einzelner Bauelemente gewonnen, sondern auch wichtige Hinweise über das Zusammenspiel der einzelnen Bauelemente innerhalb einer Schaltung. Die erste positive Erfahrung im Rahmen des SIDRA-Projektes demonstriert eindrucksvoll das Potential der Mixed-Mode-Device-Simulation zur Optimierung von CDM-Robustheit der ESD-Schutzschaltung.

Der Nutzen für die Absicherung von IC-Designs von Bosch gegenüber CDM mittels Schaltungssimulation, bearbeitet in AP3, besteht in der

- » Darstellbarkeit von Kompetenz im ESD-Schutz gegenüber Kunden,

- » Vermeidung von Redesigns,

- » Absicherung der Funktion im Feld, auch für zukünftige Halbleitertechnologien.

Damit ist die Wirksamkeit bei der Akquisition neuer IC-Entwicklungsprojekte, der Durchführung dieser Projekte und der späteren Nutzung beim Endverbraucher gegeben.

Direkt verwertbar sind die CDM-Entwurfshinweise, die für alle zukünftigen IC-Entwürfe genutzt werden. Es ist geplant, diese auch im Rahmen der intern verfügbaren ‚Design-Kits‘ den IC-Entwicklern kurzfristig zur Verfügung zu stellen.

Die CDM-Schaltungssimulation ist ebenfalls unmittelbar verwertbar. Sie wird seit Beginn 2007 für erste IC-Produkte genutzt. Es ist geplant, diese in die Standardumgebung der Schaltungsentwicklung bei Bosch zu implementieren.

## Infineon Technologies AG

Infineon erzielte in allen drei Arbeitspaketen ausgezeichnete Fortschritte durch die die Designsicherheit der Produkte und die Effizienz im Entwicklungsflow

deutlich verbessert werden konnten. Dies soll an Hand von zwei ausgewählten Beispielen aus Arbeitspaket 1 und Arbeitspaket 3 verdeutlicht werden.

Eine wichtige Fragestellung bei der Entwicklung von Schutzkonzepten gegen schnelle transiente Pulse ist die experimentelle Charakterisierung des Einschaltverhaltens der Schutzelemente. Aus detaillierten Simulationsstudien (Arbeitspaket 2 und Projekt ASDESE) wurde vorhergesagt, dass Schutzelemente bei Belastung mit sehr schnellen Pulsen die Spannung zu Beginn des Pulses nicht ausreichend klemmen können. Obwohl der erhöhte Spannungsabfall über dem Schutzelement nur wenige hundert Pikosekunden andauert bevor das Schutzelement vollständig einschaltet, kann durch diese Spannungsbelaistung die zu schützende Schaltung bereits geschädigt werden.

Bei der Entwicklung von experimentellen Charakterisierungsmethoden arbeitete Infineon eng mit dem FhG IZM-M zusammen. Das FhG IZM-M ist gemeinsamer Unterauftragnehmer von Atmel, Bosch, XFAB und Infineon und hat daher eine zentrale Rolle in Arbeitspaket 1. Am FhG IZM-M wurde ein Verfahren entwickelt, mit dem die zeitliche Auflösung des Einschaltverhaltens im Vergleich zu den bisher eingesetzten Charakterisierungsmethoden um mehr als eine Größenordnung verbessert werden konnte. Das neu entwickelte Verfahren beruht auf einer Belastung des Schutzelements mit repetierenden Pulsen, die über ein Sampling-Oszilloskop mit hoher zeitlicher Auflösung analysiert werden können. Mit diesem Verfahren lassen sich zeitliche Auflösungen von bis 25 ps erzielen. Die experimentelle Ausführung für Scheibenmessungen ist in Abbildung 1.11 gezeigt.

Die Anwendung des neuen Verfahrens auf Schutzstrukturen in 90-nm-CMOS- und 65-nm-CMOS-Technologien brachte zwei wesentliche Ergebnisse: Zum einen konnten damit die Vorhersagen aus der TCAD-Bauelementesimulation eindrucksvoll verifiziert werden. Zum anderen konnte das Einschaltverhalten von neuartigen komplexen Schutzelementen, die in diesen Technologien zum ersten Mal eingesetzt wurden, verifiziert werden. Es wurde nachgewiesen, dass diese Schutzstrukturen für einen sicheren Betrieb sehr gut geeignet sind. Im Vergleich zu konventionellen Schutzstrukturen verbessert der Einsatz dieser neuen Schutzstrukturen die Betriebssicherheit und spart zudem deutlich Chipfläche.

Das zentrale Ziel von Infineon in SIDRA war die Entwicklung eines ESD-Gesamtchip-Simulators. Mit diesem Simulationswerkzeug sollte die ESD-Festigkeit eines größeren Schaltungsblocks vorhergesagt und optimiert werden können. Dazu wurde ein völlig neues Simulationskonzept entwickelt, da die herkömmlichen Simulationsansätze aufgrund der Komplexität typischer Produkte von Infineon (> 200 Signalpins,

10–20 Versorgungsspannungen) nicht angewendet werden können.

**Abbildung 1.11:** Aufbau zur experimentellen Charakterisierung des Einschaltverhaltens von Schutzelementen gegen schnelle Transienten auf Scheibenebene.

Das neue Verfahren basiert auf drei Säulen:

- » Es wurden neue Kompaktmodelle mit drastisch reduzierter Komplexität entwickelt. Der negative differentielle Widerstand im Einschaltbereich von Schutzelementen und Schaltungstransistoren, der typisch für sogenannte „Snap-Back“-Schutzelemente und auch Treiberstrukturen ist und häufig zu Konvergenz- und Rechenzeitproblemen führt, wurde durch ein einfaches „An/Aus“-Modell ersetzt.

- » Für alle Bauelemente im Entladepfad werden die „An“- und „Aus“-Zustände permutiert. Damit ist eine vergleichsweise einfache DC-Simulation möglich. Die physikalisch unmöglichen Lösungen der Simulation (beispielsweise wenn der Strom durch ein Bauelement im „Aus“-Zustand größer als der Einschaltstrom ist) werden durch den Simulator eliminiert.

- » Ein neuer Simulationsflow wurde definiert und letztlich programmtechnisch umgesetzt.

Der neu entwickelte HBM-Gesamtchip-Simulator wurde auf zahlreiche Beispiele mit großem Erfolg angewandt. Beispielsweise konnte in einem Produkt mit mehr als 300 Pins und zehn verschiedenen Versorgungsspannungen eine Schwäche im ESD-Versorgungsschutzkonzept erkannt werden. Der „virtuelle“ ESD-Test wurde auch schon erfolgreich auf ein „System-On-Chip“ und ein „System-In-Package“ angewandt.

Der große Vorteil des ESD-Gesamtchip-Simulators ist offensichtlich: Der ESD-Gesamtchip-Simulator löst den extrem zeitaufwändigen und fehleranfälligen manuellen

Check ab. Der „virtuelle ESD-Test“ erlaubt nahezu eine 100%ige Vermeidung von ESD-Designschwächen. Allein die Vermeidung eines „tödlichen“ ESD-Fehlers führt leicht zu einer Einsparung von 500 k€ für Maskenkosten, die bei einem Re-Design anfallen würden. Damit kann der Nutzen des Gesamtchipssimulators gar nicht hoch genug eingeschätzt werden.

### **XFAB Semiconductor Foundries**

Neue Methoden der ESD-Charakterisierung von ESD-Strukturen konnten innerhalb des Projektes SIDRA erfolgreich entwickelt und getestet werden. Mit den entwickelten Testmethoden konnten neue Erkenntnisse bezüglich des ESD-Verhaltens von ESD-Schutzstrukturen gewonnen werden. Die neuen Methoden der ESD-Charakterisierung von Bauelementen und Schaltungen mit kurzen ESD-Pulsen sowie das im SIDRA-Projekt entwickelte Teststrukturkonzept werden in der Entwicklung von Standard I/O-Bibliotheken und speziellen ESD-Schutzschaltungen, z. B. in 0,35 µm und 0,18 µm Technologien, eingesetzt. Dabei dienen ergänzend zur Ermittlung der ESD-Festigkeit mit konventionellen 100 ns weiten Pulsen, kurze „very fast“ TLP-Pulse zur Charakterisierung des Triggerverhaltens der ESD-Strukturen sowie der zu schützenden Schaltung.

Ein wesentliches Ziel der Arbeiten von XFAB innerhalb des Projektes SIDRA war die Entwicklung einer Methodik des simulationsgestützten Entwurfs sowie der Optimierung von ESD-Schutzstrukturen. In verschiedenen XFAB-Technologien konnten erfolgreich ESD-Bauelementesimulationen durchgeführt werden. Physikalische Bauelementesimulationen dienen zur Vorhersage des ESD-Verhaltens von Bauelementen bzw. kompletter ESD-Schutzschaltungen. Durch die Vorhersage von Bauelementparametern wie Durchbruchsspannung, Triggerspannung oder Haltespannung können Teststrukturen im Entwurf von ESD-Schutzschaltungen

zielgerichtet entwickelt werden. Dadurch kann die Anzahl der Teststrukturen und damit der Aufwand für deren Erstellung und Charakterisierung reduziert werden. So konnten in 0,6 µm HV-CMOS-Technologie mit Hilfe von physikalischen Bauelementesimulationen verschiedene verbesserte ESD-Schutzstrukturen, speziell für Mixed-signal und High-voltage Anwendungen, mit vergleichsweise geringem Aufwand implementiert werden. Bei diesen konnten die Ergebnisse der Bauelementesimulation durch die ESD-Charakterisierung bestätigt werden. ESD-Schutzstrukturen, die in 0,6 µm HV-CMOS-Technologie implementiert wurden, konnten erfolgreich auf andere XFAB-Technologien transferiert werden, z.B. 0,6 µm SOI-CMOS oder 0,35 µm HV-CMOS-Technologie. Neben ESD-Simulationen von einzelnen Bauelementen wurden dabei auch komplexe Mixed-mode Simulationen von ESD-Schutzschaltungen, bei denen physikalische Bauelementmodelle und Spice-Modelle kombiniert werden, durchgeführt.

Die innerhalb des SIDRA-Projektes gesammelten Ergebnisse bezüglich des ESD-Verhaltens von Bauelementen und Schaltungen fließen in der Erstellung von ESD-Design-Guidelines ein. Neue Konzepte für ESD-Schutzstrukturen, speziell für High-Voltage-Anwendungen, konnten erfolgreich in verschiedenen XFAB-Technologien implementiert werden. Diese ermöglichen es, die gestiegenen Anforderungen an die ESD-Festigkeit von integrierten Schaltkreisen zu erfüllen. Weiterführende Arbeiten umfassen die Erstellung eines schaltungsbasierten ESD-Design-Checkers. Mit diesem ESD-Design-Checker sollen bereits in einem frühen Entwurfsstadium auf Schaltschichtebene und innerhalb der Cadence-Design-Umgebung IC-Designs auf mögliche ESD-Schwachstellen hin geprüft werden. Als Grundlage dient dafür eine Datenbasis mit Ergebnissen der ESD-Charakterisierung aller in einer Technologie zur Verfügung stehenden Bauelemente.

#### **Kont@kt (SIDRA):**

Dr. Petra Rose

Projektkoordination

Robert Bosch GmbH,

Tübinger-Strasse 123

72762 Reutlingen

fon: (0 71 21) 35 65 60

fax: (07 11) 8 11 - 5 14 65 60

[petra.rose@de.bosch.com](mailto:petra.rose@de.bosch.com)

# LEONIDAS+: Leitbahnorientierter Entwurf applikations-spezifischer Schaltungen

Von Markus Olbrich und Irmtraud Rügen-Herzig

Durch die zunehmend komplexen Eigenschaften des Verbindungsnetzwerks auf Chips ergibt sich eine schwer beherrschbare Vielfalt von möglichen gegenseitigen Beeinflussungen, von denen sich jede einzelne kritisch gegenüber einem stabilen Betrieb auswirken kann. Das Resultat kann eine Schaltung sein, die nicht funktionsfähig ist oder zumindest nicht die gewünschte Spezifikation erreicht, obwohl alle aktuellen Entwurfsregeln korrekt berücksichtigt wurden. Die Folgen sind Redesigns und verzögerte Produkteinführungen, wodurch Kosten wachsen und Gewinnchancen schwinden. Diese Problematik zeichnete sich bereits vor mehreren Jahren ab, wodurch sich der leitbahnorientierte Entwurf zu einer zusätzlichen Kernkompetenz für den Systementwurf entwickelte.

Im Fokus des Projektes stand das Know-how zur Entwicklung von spezifischen integrierten Schaltungen für Produkte in den Bereichen Broadcast-Media (Digital Audio Broadcasting), Automotive-Anwendungen zur Erhöhung der Sicherheit (ABS) und Umweltverträglichkeit (Motorsteuerung), mobile Kommunikationstechnik (Handys), DRAM-Technologie sowie der Bildsignalverarbeitung und –übertragung für Produkte der Unterhaltungselektronik (Multimedia-PC, Displays). Die genannten Anwendungen stellen aufgrund der ständigen Verkleinerung der Strukturen und der steigenden Komplexität der Verbindungsleitungen innerhalb der Schaltungen besondere Herausforderungen bei erhöhten Anforderungen an ihre Zuverlässigkeit. Außerdem müssen die Entwicklungszeiten verringert und Test-

zeiten weiter verkürzt werden, um Marktpositionen durch frühe Produkteinführungen erhalten und Kosten einsparen zu können.

Entscheidende Faktoren sind dabei die Leitungseigenschaften: Das Leitungsdelay (Signallaufzeit auf den Leitungen) ist mittlerweile größer als das Transistordelay. Zusätzlich nehmen die Kopplungen zwischen den Leitungen zu, weshalb sie nicht mehr unabhängig voneinander betrachtet werden dürfen. Heterogene Leitungssysteme in komplexen Mixed-Signal-Schaltungen sind außerdem im Entwurf wegen unterschiedlicher Anforderungen an die Modellierung schwer handhabbar. Weiterhin wird der Test von integrierten Schaltungen durch das Leitungsdelay erschwert.

Um den genannten Herausforderungen zu begegnen, musste die erforderliche Entwurfskompetenz deutlich erweitert bzw. teilweise erst entwickelt werden. Allgemeine Lösungen „von der Stange“, wie sie von den führenden amerikanischen EDA-Firmen angeboten wurden, waren nicht ausreichend für leitbahnzentrierte Entwurfsmethoden wegen der besonderen Schwerpunkte bei den durch die Projektpartner vertretenen Anwendungen. Daher mussten spezielle Tools und Methoden entwickelt werden, die eine gezielte Berücksichtigung der Leitbahnen im Entwurf ermöglichen.

Die Entwurfsfähigkeit ist eine Voraussetzung für die Verfügbarkeit spezifischer SoCs für die genannten

## Zusammensetzung des Konsortiums:

### Partner:

- » Atmel Germany GmbH

- » Robert Bosch GmbH

- » Cadence Design Systems GmbH

- » Institut für Mikroelektronische Systeme, Leibniz Universität Hannover

- » Infineon Technologies AG

- » NXP Semiconductors

### Unterauftragnehmer:

- » Universität Siegen, Institut für Mikrosystemtechnik

- » TU Dresden, Institut für Feinwerktechnik und Elektronik-Design

- » TU Darmstadt, Fachgebiet Mikroelektronische Systeme Redemund & Thiede Datentechnik GmbH

- » Universität Ulm, Abteilung Allgemeine Elektrotechnik und Mikroelektronik

- » Qimonda AG

### Förderkennzeichen:

01 M 3074

### Projektaufzeit:

01.03.2005–28.02.2007

## Steigerung der Entwurfskompetenz

## Steigerung der Entwurfseffektivität

|                                                           |

|-----------------------------------------------------------|

| Selektive Extraktion zur Beherrschung der Komplexität     |

| Modellierung von DSM-Effekten: X-Talk, Prozessvariationen |

| Constraints Mgm. und Umsetzung                            |

| Leitbahnzentrierte Place&Route-Verfahren                  |

| Leitbahnorientierter Designflow                           |

|                                                 |

|-------------------------------------------------|

| Optimale Ausnutzung der Nanometer-Technologien  |

| Kürzere Designzeiten durch weniger Designzyklen |

| Entwürfe von Chips mit hoher Zuverlässigkeit    |

| Hohe Designproduktivität                        |

Abbildung 1.12: Projektziele von LEONIDAS+

Anwendungen. Dieser Wettbewerbsvorteil sichert den Industriestandort. Daher haben die Forschungsarbeiten unmittelbaren volkswirtschaftlichen Nutzen und sichern Arbeitsplätze. Um in Deutschland die Kompetenz zum leitbahnorientierten Entwurf in den genannten Anwendungsbereichen aufzubauen, wurden durch das BMBF zwei Verbundvorhaben gefördert: LEO-NIDAS (April 2002 bis März 2004) und LEONIDAS+ (März 2005 bis Februar 2007), dessen Ergebnisse hier kurz vorgestellt werden.

### Projektziele

Entscheidend war die Erkenntnis, dass die Leitbahnenenschaften nicht mehr „parasitäre“, also störende Effekte zweiter Ordnung sind, sondern bestimmende Entwurfssparameter aktueller Chips darstellen. Sie sind zentraler Entwurfsgegenstand und müssen von Beginn an auf allen Abstraktionsebenen entworfen und mit berücksichtigt werden.

Ziel dieses Projekts war es, einen solchen leitbahnzentrierten Entwurf zu ermöglichen. Die gesamte Thematik mit ihrer allgemeinen Bedeutung hat weitreichende Auswirkungen. Der begrenzte Projektumfang erforderte es allerdings, sich auf eine Reihe von Kernbereichen innerhalb der Zielanwendungen zu konzentrieren, die für sich abgeschlossen wurden. Damit wurden in benachbarten Bereichen weitere Entwicklungen angestoßen und eine nachhaltige Wirkung erzielt. Abbildung 1.12 zeigt die technischen Projektziele im Überblick.

### Highlights der Projektergebnisse

Eine wesentliche bei Leitbahnen auftretende Komplikation ist der Crosstalk, das heißt das Übersprechen von Signalen durch Kopplungen zwischen den Leitungen. In LEONIDAS+ wurden einerseits die Kopplungen über das Substrat untersucht. Dabei entstand ein Tool, das in dieser Hinsicht kritische Bereiche identifiziert und einer Analyse zuführt. Zum anderen ist der Crosstalk zwischen Leitungen relevant für das Zeitverhalten einer digitalen Schaltung. Entscheidend dabei sind die logischen Abhängigkeiten der Signale. Hierzu wurde ein Verfahren zur Abschätzung des Worst-Case-Crosstalks entwickelt. Dabei werden auch logisch unmögliche Situationen erkannt und herausgefiltert. So können unnötige „Optimierungen“ in Zukunft vermieden werden, die andere Designparameter, wie Power und Fläche verschlechtern. Zusätzlich wird die Anzahl der Optimierungsschleifen verringert, was Entwurfszeit und Kosten einspart.

Die Arbeiten zur Berücksichtigung von Prozessvariationen im Entwurf haben zu neuen Verfahren geführt, die u.a. die Berechnung von charakteristischen Verteilungsgrößen um Größenordnungen beschleunigen. Dadurch wird der Einfluss der Interconnect-Variationen nun auch für dreidimensionale Leitungsmodelle praktikabel. Diese bessere und schnellere Analyse ermöglicht Entwürfe mit einer höheren Ausbeute bei der

Herstellung und führt zu erhöhter Zuverlässigkeit der Produkte.

Im Rahmen des Projektes sind besondere Fortschritte zur Lösung der Fragestellung erzielt worden, wie eine Menge von Constraints automatisch bei der Layoutsynthese berücksichtigt werden kann. Der entwickelte parasitensymmetrische Verdrahter legt die Leitungen eines Busses simultan unter Berücksichtigung der differentiellen Widerstände, Kapazitäten und Induktivitäten. Die entstehenden Leitungsgeometrien wurden verifiziert, indem die Leitungsparameter extrahiert und auf ihre Symmetrie hin analysiert wurden. Die Verwendung des parasitensymmetrischen Verdrahters verspricht kürzere Entwicklungszeiten von HF-Schaltungen und weniger durch falsche Leitungsführung verursachte Redesigns.

In einer weiteren Arbeit zum Umgang mit Constraints ging es um die Stromdichten in Leitungen. Die Pinanschlüsse können nun im Layout automatisch stromdichtegerecht ausgeführt und die Stromdichten verifiziert werden. Zusätzlich wurde ein Floorplanner entwickelt, der eine Vielzahl von Constraints gleichzeitig berücksichtigt. Die grundlegenden Arbeiten zur Identifikation und Speicherung der wesentlichen Constraints im leitungsorientierten Layoutentwurf fanden Eingang in ein kommerzielles Tool von Cadence.

Das Layout einer Schaltung wird üblicherweise in zwei Schritte unterteilt: Erst werden die Bauelemente platziert und anschließend die Leitungen zwischen ihnen verlegt. Dieses Vorgehen kann nicht optimal sein, weil entscheidende Details der Verdrahtung auch Rückwirkung auf die Platzierung haben müssen. Ein Teil der Arbeiten konzentrierte sich daher darauf, diese strikte Trennung aufzubrechen und einen fließenden Übergang zu ermöglichen. Das Ergebnis ist ein neues Verfahren zur gleichzeitigen Platzierung und Globalverdrahtung. Außerdem wurde ein Tool zur 3D-Platzierung entwickelt, das die Delaybedingungen von Anfang an berücksichtigt. Dadurch werden Verletzungen der Timingbedingungen frühzeitig vermieden, was verkürzte Entwicklungszeiten erwarten lässt.

Die Leitungen haben auch Einfluss auf die Testbarkeit von Signalpfaden. Es wurde eine Umgebung entwickelt, die den Designer dabei unterstützt, Testpunkte an den Stellen im Signalpfad einzufügen, wo sie die Timing-Bedingungen nicht verletzen und trotzdem die Testbarkeit deutlich erhöhen. Zusätzlich verringert das Tool die Anzahl der Testmuster bei gleicher Fehlerabdeckung. Dies erhöht die Testqualität, da die gesparten Testmuster für zusätzliche Tests verwendet werden können.

Beim Schaltungsentwurf genügt es nicht, die Leitbahnen durch grobe Ersatzschaltungen aus Widerständen zu modellieren. Der entwickelte „Partielle Layoutflow“ ermöglicht es, Leitungsgeometrien während des

Abbildung 1.13: Mitarbeiter im Projekt LEONIDAS+

Schaltungsentwurfs präzise durch parametrisierbare Zellen zu beschreiben. Diese werden vor der Simulation automatisch charakterisiert, wodurch eine vollständige Integration in den Entwurfsflow gegeben ist. Die Simulationsergebnisse sind durch bessere Modellierung aussagestärker bei guter Performance. Der partielle Layoutflow verringert dadurch die Entwurfszeit und vermeidet Redesigns, die durch unvorhergesehene Auswirkungen der Leitungseigenschaften nötig wären.

#### Fazit

Während der Projektlaufzeit ist eine Vielzahl prototypischer Entwurfswerkzeuge entstanden. Diese

werden zurzeit in den Firmen in ersten Pilotprojekten erprobt. Die Fülle an Ergebnissen konnte hier nur in Ausschnitten angerissen werden. Als Ergebnis sind die Leitbahnen als wesentlicher Entwurfsgegenstand in den bearbeiteten Bereichen deutlich handhabbar geworden. Die erfolgreichen Projektarbeiten haben zusätzlich – zu den skizzierten Ergebnissen – neue Forschungsgebiete und Förderprojekte ange regt, wie die Behandlung von Prozessvariationen in 65 nm-Technologien und darunter sowie den Constraint-geführten Entwurf. Die beteiligten Mitarbeiter (Abbildung 1.13) blicken auf ein erfolgreiches Projekt zurück.

#### Kont@kt (LEONIDAS+):

##### Projektkoordination:

Infineon Technologies AG

Irmtraud Rügen-Herzig

fon: (0 89) 2 34 - 2 10 46

irmtraud.rugen-herzig

@infineon.com

##### Projektmanagement:

Leibniz Universität

Hannover, IMS

Dr. Markus Olbrich

fon: (05 11) 7 62 - 1 96 61

markus.olbrich

@ims.uni-hannover.de

# Nachrichten von den Projekten

[www.edacentrum.de/projekte](http://www.edacentrum.de/projekte)

**Neben den Berichten von PRODUKTIV+, LEONIDAS+ und SIDRA vermelden auch andere Projekte Neuigkeiten. So ist Herkules ein Durchbruch der Verifikation gelungen, VeronA hat erfolgreich ein Tutorial veranstaltet und ein neuer Fach- und Kooperationsworkshop kündigt sich an.**

## Fach- und Kooperationsworkshop zum Thema

### Verifikation

Die Projekte HERKULES, URANOS, VeronA und VISION sowie das Clusterforschungsprojekt FEST laden dieses Jahr zu einem Kooperationsworkshop rund um das Thema „Verifikation“ ein. Der Workshop findet statt:

- » am Dienstag, den **16. Oktober 2007**, von 9:00 h bis ca. 17:00 h

- » im Werkhof Hannover Nordstadt (fünf Gehminuten vom edacentrum entfernt)

Detaillierte Informationen zum Ablauf, zur Organisation und zur Einreichung von Vorträgen finden Sie unter: [www.edacentrum.de/kooperations-workshop/verifikation](http://www.edacentrum.de/kooperations-workshop/verifikation)

**Kont@kt & Anmeldung:**

Dr. Cordula Hansen

fon: (07 11) 2 80 79 56

[hansen@edacentrum.de](mailto:hansen@edacentrum.de)

Wie bereits in den vorherigen Workshops werden auch dieses Mal die sich aus den Vorträgen ergebenden Fragestellungen und Diskussionen im Vordergrund stehen. Das Ziel des Workshops ist der Austausch von Gedanken, Sichtweisen, Lösungsansätzen und Erfahrungen zum Thema Verifikation. Um dieses Ziel zu unterstützen, wird der Workshop in einer Kombination aus Arbeitsgruppen und Vorträgen durchgeführt. (CH)

### Herkules meldet einen Durchbruch bei der Verifikation parametrierter Schaltungen

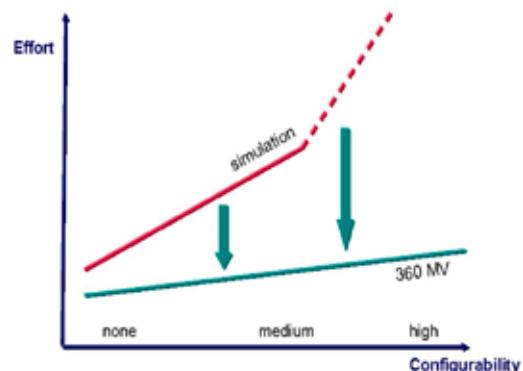

20. Juni 2007. Beim edaWorkshop in Hannover stellte der Projektpartner OneSpin Solutions GmbH eine Erweiterung seiner Verifikationslösung 360™ Module Verifier vor, mit der Anwender erstmals alle Konfigurationen einer parametrisierten Schaltung in einem einzigen Durchlauf vollständig verifizieren können.

**Kont@kt (OneSpin):**

Dr. Klaus Winkelmann

OneSpin Solutions GmbH,

München

fon: (0 89) 9 90 13 - 4 11

fax: (0 89) 9 90 13 - 1 00

[klaus.winkelmann@onespin-solutions.com](mailto:klaus.winkelmann@onespin-solutions.com)

**One-Shot-Analyseverfahren für konfigurierbare IP-Komponenten**

HERKULES präsentierte ein viel beachtetes Ergebnis zur Verifikation parametrierter IP-Komponenten (Intellectual Property). Solche Schaltungen lassen sich für die Wiederverwendung in verschiedenen konkreten

Systemumgebungen anpassen, in dem Parameter geeignet gesetzt werden. Eine sorgfältige Verifikation solcher Module erfordert derzeit die Durchführung der entsprechenden Tests separat für jeden Parametersatz, d. h. der Aufwand steigt exponentiell mit der Anzahl der Parameter.

Die neue Lösung nutzt nun Techniken der formalen Verifikation auf Basis von OneSpins Produkt-Flaggschiff OneSpin 360™ Module Verifier, um allgemeine Aussagen über alle Parametersätze zu prüfen. Im Gegensatz zu Simulations- und Assertion-basierten Verifikationsansätzen erlaubt diese Lösung bereits in einem einzigen Durchlauf die vollständige Verifikation mehrerer Konfigurationen – mit der Gewähr, dass jede einzelne Konfiguration fehlerfrei funktioniert. Dadurch müssen nicht mehr länger vielfache Konfigurationen generiert und separat verifiziert werden.

### Parametrierter DMA-Controller vollständig verifiziert

Zur Erprobung des Ansatzes wurde ein DMA-Controller (Direct Memory Access) mit 8 Parametern als Beispieldschaltung in VHDL entwickelt. Die 138240 zulässigen Konfigurationen dieser Schaltung wurden in einem einzigen Durchlauf auf einem Rechner in ca. 3 Minuten verifiziert. Die Entwicklung des vollständigen Eigenschaftssatzes für alle Konfigurationen wurde in nur 6 Personentagen – gegenüber 4 Tagen zur Entwicklung eines solchen Satzes für eine einzelne Konfiguration – geleistet. Demgegenüber steht simulatives Vorgehen, das alle (benötigten) Konfigurationen

**Abbildung 1.14:** Steigender Verifikationsaufwand bei zunehmender Parameter-Anzahl: Während für hochgradig konfigurierbare Schaltungen der Simulationsaufwand etwa exponentiell steigt, werden diese durch den Einsatz formaler Techniken mit moderatem Aufwand beherrschbar.

einzelnen, „on demand“ und unvollständig verifiziert. Zusätzlich lieferte der formale Ansatz eine exakte Beschreibung der zulässigen Parametersätze: z. B. werden alle Konfigurationen als nicht-zulässig ausgeschlossen, die für zwei verschiedene Register die gleiche Adresse vergeben.

Damit wurde das Projektziel erreicht, das Potenzial der formalen Verifikation zu einer drastischen Aufwandsersparnis bei der Verifikation parametrisierter Schaltungen zu nutzen.

### Richtigstellung zum Projektkonsortium von URANOS

Bedauerlicherweise ist der Redaktion des „newsletter edacentrum“ in der letzten Ausgabe ein Fehler unterlaufen: Beim Projektbericht zum Projekt URANOS wurde ein falsches Projektkonsortium angegeben. Das richtige Projektkonsortium besteht aus den Projekt-partnern:

- » AMD Saxony LLC & Co. KG – DDC

- » FZI Karlsruhe – SIM

- » Infineon Technologies AG

- » Silicon Image GmbH (ehem. sci-worx)

und den Unterauftragnehmern:

- » Fraunhofer-IIS, EA

- » Technische Universität Chemnitz – SSE

- » Technische Universität Chemnitz – TI

- » Universität Bremen – AGRA

- » Universität Trier – Lehrstuhl für Wirtschaftsinformatik II

Wir bitten, diesen Fehler zu entschuldigen. (Pp)

### VISION entwickelt ganzheitlichen Ansatz zum Thema „Modellierung und Analyse verteilter Systeme“

Auf dem am 10. und 11. Juli 2007 veranstalteten projektinternen Workshop zum Thema „Ganzheitliche Modellierung verteilter mikroelektronischer Systeme und Ansätze zur methodischen Analyse des Kommunikationsverhaltens“ wurden erfolgreich Ergebnisse aus den ersten beiden Arbeitspaketen zusammengeführt und gemeinsam weiterentwickelt.

Auf der, beim Projektpartner Infineon Technologies AG durchgeführten Veranstaltung stand die Evaluierung bezüglich existierender Standards zur Modellierung verteilter Systeme im Mittelpunkt. In diesem Zusammenhang wurden verschiedene Methoden diskutiert, welche einen einheitlichen Modellierungsansatz ermöglichen. Ein auf der neuesten Version der

Unified Modeling Language (UML) basierende Ansatz soll sowohl für die Darstellung der Struktur als auch des Verhaltens eines mikroelektronischen Systems der zu betrachtenden Applikationsdomänen Automobil und Mobilkommunikation angewendet werden können. Damit soll auch erstmalig die Lücke zwischen Hardware- und Softwareentwicklung bzw. zwischen Anforderungs-Management und der Entwicklungstätigkeit geschlossen werden. Das Vorgehen erlaubt eine ganzheitliche Beschreibung des zu entwerfenden Systems auf sehr hoher Abstraktionsebene, was die frühzeitige Erkennung von Fehlern im System-integrationsprozess unterstützt, kostenintensive Entwicklungs- und Korrekturzeiten minimiert und den effizienten Entwurf heutiger hochkomplexer Systeme überhaupt ermöglicht.

Weiterhin konnten sich die teilnehmenden Projektpartner auf den Aufbau eines konkreten Beispielsystems zur Veranschaulichung der im Projekt VISION adressierten Forschungsthematik verstündigen. Dieser Abgleich garantiert sowohl eine einheitliche Sichtweise auf die Anforderungen und Durchführung der Systemmodellierung und -analyse als auch ein durchgängiges Konzept zur automatisierten Erzeugung von virtuellen Prototypen, die zur frühzeitigen Evaluierung des Systems eingesetzt werden. (Tr)

### Folien des Tutorials „Formalisierte Methoden zur Verifikation analoger Schaltungen“ im Internet

Auf mehrfachen Wunsch sind die bei dem Tutorial „Formalisierte Methoden zur Verifikation analoger Schaltungen“ gezeigten Folien im Internet als PDF-Datei verfügbar. Die Datei umfasst 133 Seiten (16 MB) und enthält alle bei dem Tutorial präsentierten Folien. Zum Öffnen des Dokuments wird ein Passwort benötigt, dass unter dem hier oder auf der VeronA-Webseite ([www.edacentrum.de/verona/](http://www.edacentrum.de/verona/)) angegebenen Kontakt erfragt werden kann.

**Kont@kt (URANOS):**

AMD Saxony LLC & Co. KG –

Dresden Design Center

Dr. Hans-Jürgen Brand

fon: (03 51) 2 77 - 60 16

Weitere Informationen sind unter [www.uranos-projekt.de](http://www.uranos-projekt.de) zu finden.

Die Folien des Tutorials sind unter [www.edacentrum.de/verona/tutorial.pdf](http://www.edacentrum.de/verona/tutorial.pdf) verfügbar.

**Kont@kt (VeronA):**

Ralf Popp

fon: (05 11) 7 62 - 1 96 97

popp@edacentrum.de

Das Tutorial wurde am 21. Juni 2007 vom Projekt VeronA („Verifikation analoger Schaltungen“) mit Unterstützung des Clusterforschungsprojektes FEST („Funktionale Verifikation von Systemen“) veranstaltet. Der interessierten Öffentlichkeit wurde dabei ein umfassender Überblick über diesen zukunftsträchtigen EDA-Bereich gegeben. Die dabei behandelten Themenkomplexe umfassten Pareto-Optimierung, Verifikation hybrider Systeme, Model Checking analoger Systeme sowie Einführungen in die Theorie und den Stand der Technik der formalen Analyse digitaler Schaltungen. Neben diesem Überblick ermöglichte die Veranstaltung die projektinterne gegenseitige Information zum Stand der Forschungsarbeiten bei der formalisierten Verifikation analoger Schaltungen, die Gegenstand des Arbeitspakets 2 in VeronA sind. Das Tutorial stieß auf gute Resonanz innerhalb und außerhalb der beiden Projekte. (Pp)

**Kont@kt (VISION):**

Dr. Dieter Treytnar

fon: (05 11) 7 62 - 1 96 87

treytnar@edacentrum.de

## Neues aus der Clusterforschung

[www.edacentrum.de/clusterforschung](http://www.edacentrum.de/clusterforschung)

### Schlussveröffentlichung von SAMS auf dem edaWorkshop07

Das SAMS-Projekt präsentierte mit dem Vortragenden Prof. Dr. Christoph Grimm die Schlussveröffentlichung des Clusterforschungsprojekts und stellte ein Resümee über die Ergebnisse nach drei Jahren Projektlaufzeit vor. Die Veröffentlichung ist im Tagungsband des edaWorkshop07 enthalten und kann über das edacentrum bezogen werden.

Prof. Dr. C. Grimm

Weitere Ergebnisse zu dem Projekt werden auf dem Fach- und Kooperationsworkshop „Verifikation“ (Seite 18) am 16.10.2007 in Hannover vorgestellt.

### FEST mit dem Beitrag „Eigenschaftsbasierte Entwurfsmethodik für die Systemebene“ auf dem edaWorkshop07

In dem edaWorkshop-Vortrag von Prof. Dr. Hans Eveking wurden die Forschungsergebnisse der TU Darmstadt im FEST-Projekt näher betrachtet, die sich zum Einsatz bei der Prototypenentwicklung eignen. Durch eine Modellierung der Eigenschaften eines Blocks in einem sogenannten „Cando“-Objekt können die Moduleigenschaften für den Prototyp verifiziert werden. Diese Cando-Objekte stellen eine abstrakte Beschreibungsform der Eigenschaften von Teilen eines Systems dar, mit denen auch verbotene Eigenschaften dargestellt werden können.

### Das Projekt „Funktionale Verifikation von Systemen“ (FEST) im Juni 2007 abgeschlossen

Nach drei Jahren Laufzeit beendete FEST seine Projektarbeit. Letzte Ergebnisse wurden auch auf dem edaWorkshop07 in Hannover präsentiert. Hier gab es einen von Prof. Bernd Becker von der Uni Freiburg gehaltenen Übersichtsvortrag zu dem Sie einen Bericht in dieser Ausgabe des newsletter edacentrum auf Seite 27 finden.

Mit Hilfe dieser Modellierung kann ein Prototyp verfeinert, simuliert und dessen Eigenschaften im Gesamtkontext verifiziert werden. Während der Verfeinerung der Verifikation, werden auch die Cando-Objekte verfeinert, um somit die Blockeigenschaften zu vervollständigen. Cando-Objekte unterstützen die Verfeinerung der Verhaltensmodelle, um die Beschrei-

2

## Neues aus dem edacentrum

### Termine und Formalien für neue Projekte

[www.edacentrum.de/projekttermine](http://www.edacentrum.de/projekttermine)

Die Termine für die Einreichung zur Steuerungsgremiumssitzung am 5. Dezember 2007 in München sind:

- » Anmeldung einer Einreichung bis: 23.10.2007

- » Abgabe der ersten Version bis: 06.11.2007

- » Abgabe der letzten Version bis: 20.11.2007