# newsletter edacentrum 01 2007

10,- Euro

ISSN 1862-2283

electronic design automation centrum

[www.edacentrum.de/newsletter](http://www.edacentrum.de/newsletter)

## Projektspiegel – Projekte stellen sich vor

„DETAILS: HF-Design-Technologie für präzise analoge IP-basierte Front-End-Lösungen in höchstintegrierten Datenübertragungs-Systemen“, dazu Kurzberichte von SAMS und HERKULES

## Bewegung im zweiten Quartal 2007

Das edacentrum präsentiert sich auf der DATE in Nizza und mit dem edaWorkshop07

## edaForum06

Heiße Tage in Berlin – Fachliches Feuerwerk im lauen Berliner Winter (Teil 2)

# Editorial

Liebe Leserinnen und Leser,

**Zitat:** Blaise Pascal (1623–62), frz. Mathematiker u. Philosoph

„Zu unserer Natur gehört die Bewegung. Die vollkommene Ruhe ist der Tod.“

Bewegung ist ein zentrales Thema, das man überall finden kann, ob im direkten oder indirekten Sinne. Bewegung steht nicht nur für Fortbewegung sondern auch für Veränderung, wie zum Beispiel der Jahreswechsel.

Doch halt! Bleiben wir noch kurz im alten Jahr, da war doch noch etwas. Richtig, das edaForum06 in Berlin, Mitte November. Und weil es von dort so viel zu berichten gab, dass es für eine Ausgabe des „newsletter edacentrum“ zu viel gewesen wäre, reichen wir Ihnen in dieser Ausgabe den zweiten Teil des Berichtes über das edaForum06 nach. (s. Seite 25)

Bewegen wir uns nun zum neuen Jahr: Auch wenn sich der letzte „newsletter edacentrum“ aus dem Jahr 2006 zeitlich ein wenig verirrt hatte, so halten Sie mit dieser Ausgabe das erste Heft des Jahres 2007 in Händen, hoffentlich nicht allzu fest, weil gerade wieder ein wenig bewegte Luft über die Lande zieht.

Weit mehr als „ein wenig bewegte Luft“ war Sturmorkan Kyrill, der so massiv über Deutschland hinweg blies, dass ganze Dächer die Luft unsicher machten, sich Bäume einen neuen Standort suchten (allerdings nicht aus eigenem Antrieb) und letztlich der gesamte Bahnverkehr lahm gelegt wurde. Wie sagte Pascal so schön, die Bewegung (der Luft) gehört zu unserer Natur, und die Ruhe nach dem Sturm kann Schreckliches ans Licht bringen, wie die Tatsache, dass Tausende von Menschen während des Orkans auf den Bahnhöfen übernachten mussten. Auch Frau Dr. Hansen vom edacentrum durfte die Auswirkungen des Sturmes am eigenen Leibe erfahren und hat ihre Erlebnisse als Bericht für Sie festgehalten. (s. Seite 30).

Wenn Sie dorthin blättern, werden Sie feststellen, dass sich die Nummerierung der Rubriken etwas geändert hat. Kyrill hat hiermit jedoch nichts zu tun und auch der Satz ist nicht durcheinander gekommen. Grund für die Umnummerierung ist die neue Rubrik „Veranstaltungen“, unter der künftig alle Ankündigungen und Berichte von Veranstaltungen zu finden sind.

## Was war:

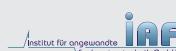

**Abbildung 0.03:**

Das edaForum06 in Berlin (S. 25)

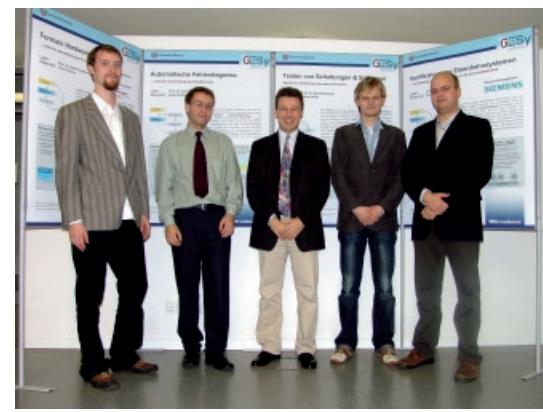

**Abbildung 0.04:**

Begutachtungen und Kickoff-Treffen verschiedener Ekompass-Projekte (S. 20)

**Abbildung 0.05:**

Kyrill – Ein Januar-Orkan über Deutschland (S. 30)

**Abbildung 0.06:**

Ergänzende Informationen zum newsletter edacentrum finden Sie unter [www.edacentrum.de/newsletter/](http://www.edacentrum.de/newsletter/)

Abbildung 0.03

Abbildung 0.04

Abbildung 0.05

Abbildung 0.06

Wo wir schon bei sich bewegenden Zahlen sind: Die Mitarbeiterzahl des edacentrum ist ebenfalls gestiegen und schon hinterlässt eine neue Autorin im „newsletter edacentrum“ ihre Spuren. Doch zurück zur Bewegung ...

Auch in der Entwurfsautomatisierung findet Bewegung statt, wie die Entwicklung von Innovation, der Austausch von Gedanken, Kommunikation. Schlimm wäre, wenn all das stillstehen würde, denn, da hat Pascal schon Recht, zu unserer Natur gehört Bewegung. Und zur Bewegung gehören mehrere kleine Schritte.

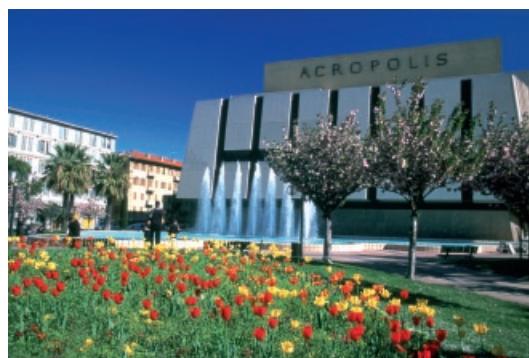

Einer dieser Schritte kann Sie zur DATE07, die vom 16.–20. April stattfindet, bringen (s. Seite 32). Bewegt hat sich übrigens auch der Veranstaltungsort selbst. Extra zum 10jährigen Jubiläum findet die DATE weder in Paris noch in München statt, sondern weiter im Süden in Nizza, der inoffiziellen Hauptstadt der Côte d’Azur in Frankreich. Auf der DATE07, die wie immer zahlreiche Konferenzen und Ausstellungen zum Thema EDA vereint, ist auch das edacentrum mit einem Stand als Guest bei Synopsys vertreten. Zudem organisieren wir dieses Jahr wieder das Exhibition Theatre und ermöglichen Beiträge von Ekompass-Projekten in der University Booth.

Ein weiterer Schritt könnte ein Besuch des edaWorkshop07 am 19.–20. Juni 2007 im Courtyard by Marriott Hotel in Hannover sein. Dort erwarten Sie Vorträge zu wissenschaftlichen Fachthemen und zu den Ergebnissen der EDA-Forschungsprojekte, eine Posterausstellung, der Kooperationsmarkt unter dem Motto „Ideen suchen Abnehmer - Markt sucht Innovationen“ und insbesondere reichlich Gelegenheit zum Networking. Forschung und Industrie sind hierbei gleichermaßen präsent, so dass der fachliche Austausch verbunden werden kann mit der Initiierung von Kooperation zur Vorbereitung eines industriellen Nutzens. Nutzen auch Sie diese Gelegenheiten. Wir freuen uns auf Sie!

Vorerst wünschen wir Ihnen jedoch viel Spaß mit dieser Ausgabe des Newsletters!

*Susanne Sass*

Susanne Sass für das edacentrum

# Inhaltsverzeichnis

Seite 5

**Projektspiegel**

**Projektbericht DETAILS:**

**Neue Möglichkeiten für Konzipierung und Entwurf von höchst-integrierten Endgeräten mit besonderer Berücksichtigung von eingebetteten HF-IP Baugruppen.**

Das F&E-Projekt DETAILS wurde am 31.3.2007 abgeschlossen. Dieser Bericht stellt die in der dreijährigen Laufzeit durchgeföhrten Arbeiten vor und zeigt, wie die dabei erreichten Ergebnisse in zukünftige Anwendungen integriert werden können.

Seite 25

**EDA-Veranstaltung**

**edaForum06 – Heiße Tage in Berlin (Teil 2)**

Im zweiten Teil der Berichterstattung über das im November 2006 in Berlin stattgeföndene edaForum lesen Sie eine Zusammenfassung der beiden „Business Sessions“ mit den Titeln „The Times They are a-Changin‘ – Chip Business is System Business“ und „With a little help from my friends – Leadership Means Partnership“.

## Überblick

### Inhaltsverzeichnis

Seite 3

## Projektspiegel

### **MAYA - Hardwareentwurfstechnik für Null-Fehler-Designs**

Eine Kurzvorstellung des neuen Verifikationsprojektes.

Seite 14

## Projektspiegel

### **SAMS - Struktursynthese von analogen Schaltungen**

Seite 17

Schlußbericht des am 31.10.2006 abgeschlossenen ersten EDA-Clusterforschungsprojektes.

## Projektspiegel

### **Nachrichten von den Projekten**

Seite 20

Lesen Sie die Meldungen der Ekompass-Projekte und erfahren Sie mehr über den Fach- und Kooperationsworkshop „Technologie und deren Auswirkung“ im Mai.

## Projektspiegel

### **Neues aus der Clusterforschung**

Seite 22

Die Planungen für das vierte EDA-Clusterforschungsprojekt sind angelaufen.

## Neues aus dem edacentrum

### **Neue Personen am edacentrum**

Seite 22

Im Steuerungsgremium des edacentrum gibt es Wechsel und am edacentrum eine neue Mitarbeiterin.

## EDA-Veranstaltung

### **MEDEA+/ENIAC Forum**

Seite 28

Ein Bericht vom MEDEA+/ENIAC-Forum 2006, die Ende November 2006 in Monaco stattgefunden haben.

## EDA-Veranstaltung

### **Arbeitskreis „IC Design“ mit einem Workshop im Mai**

Seite 34

Geballte Kompetenz zahlreicher Unternehmen und Forschungseinrichtungen auf dem Gebiet des Entwurfs von Analog-, Mixed-Signal- und HF-Bauelementen.

## Trendberichte

### **Unser Angebot: Der „edaTrend DATE07“**

Seite 38

Sie können nicht vor Ort sein, möchten sich aber über alles Wissenswerte von der DATE informieren? Dann wird Sie das neue Angebot vom edacentrum interessieren!

## Projektmanagement

### **Alex und Bill – Die Notwendigkeit, an einem Strang zu ziehen**

Seite 38

Die Fortsetzungsgeschichte zum Projektmanagement.

## Panorama

### **Meldungen aus der EDA-Welt**

Seite 42

Halten Sie eine EDA-Rückschau auf die vergangenen Monate mit dem „Pressescan“ im newsletter edacentrum.

## Marktbeobachtung

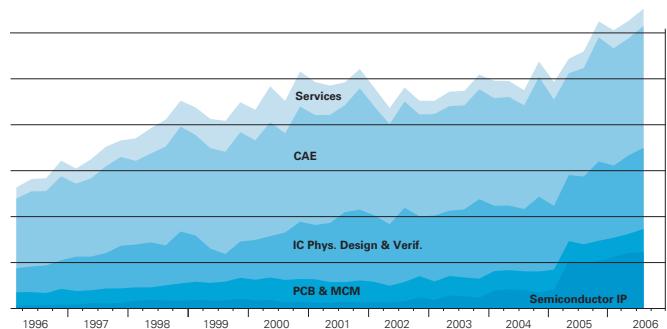

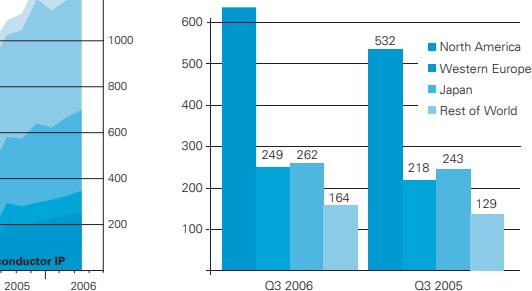

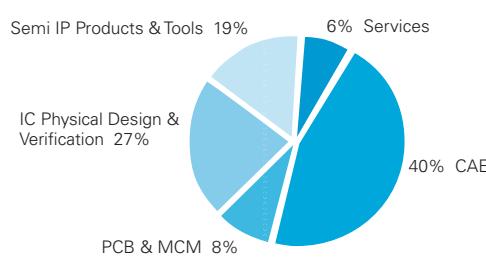

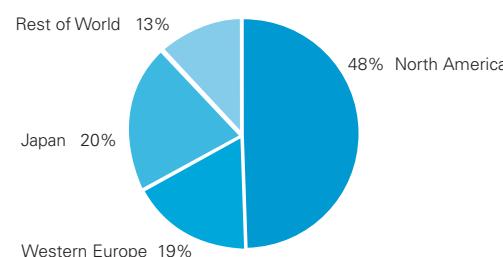

### **EDA Consortium reports continued Growth in 3rd Quarter 2006**

Seite 45

Wie in jeder Ausgabe finden Sie hier die Entwicklung der aktuellen Umsatzzahlen im Bereich EDA.

## Neues von den Mitgliedern

### **Portraits und Neuigkeiten unserer Mitgliedsfirmen**

Seite 46

Mitgliedsfirmen stellen sich und ihre neuen Produkte vor.

## Ausblick

### **Vorschau auf die kommende Ausgabe**

Seite 55

Seite 24

Seite 32

**EDA-Veranstaltung**

**edaWorkshop07 – das Programm steht fest**

Mit dem Abschluss des Begutachtungsprozesses steht das Programm des Workshops nahezu fest. Lesen Sie, wie sich der Inhalt des edaWorkshop im Vergleich zur Vorjahresveranstaltung weiterentwickelt hat und freuen Sie sich auf anregende Gespräche am 19. und 20. Juni 2007 in Hannover.

**EDA-Veranstaltung**

**Besuchen Sie das edacentrum auf der DATE!**

Auch dieses Jahr ist das edacentrum wieder auf Europas größter „EDA-Schau“ der DATE vertreten. Lesen Sie, was Sie dort inhaltlich erwarten und besuchen Sie uns vom 17.-19. April 2007 auf der DATE in Nizza. Wir sind am Stand von Synopsys (Booth M4 in the Méditerranée Hall) für Sie da und freuen uns auf Ihren Besuch!

# 1 Projektspiegel

## Der Ekompass-Förderkomplex

[www.edacentrum.de/ekompass](http://www.edacentrum.de/ekompass)

Die zur Zeit vom edacentrum betreuten Projekte gehören zu dem vom Bundesministerium für Bildung und Forschung (BMBF) zur Stimulation von EDA-Forschungsaktivitäten eingerichteten Förderkomplex namens Ekompass. Ekompass steht für „Entwurfsplattformen für komplexe angewandte Systeme und Schaltungen der Mikroelektronik“. Mit diesem Förderkomplex will das BMBF in erster Linie dazu beitragen, die einer starken internationalen Konkurrenz ausgesetzten Arbeitsplätze in der Systemindustrie und im EDA-Umfeld zu erhalten und auszubauen.

Ziel ist es, durch ein gemeinsames Vorgehen von Industrie, Forschung und öffentlicher Hand, in den für Deutschland (und für Europa) wichtigen Bereichen neue Entwurfsmethoden zu entwickeln, um die Komplexität zukünftiger Chipsysteme qualitätsgerecht und

effektiv beherrschen zu können. Dabei wird der Fokus auf solche Themen gelegt, denen für die Wettbewerbsfähigkeit der deutschen Industrie die größte Bedeutung zukommt.

Der Förderkomplex Ekompass ist allerdings nicht nur von nationaler Bedeutung. Die meisten Forschungsvorhaben haben ein internationales Umfeld, insbesondere auf europäischer Ebene, wo Synergien aus gemeinsamen Stärken entstehen. Die für Ekompass sehr wichtige europäische Zusammenarbeit wird auch dadurch transparent, dass einige der Ekompass-Projekte in MEDEA+ Projekte eingebettet sind.

Der Newsletter des edacentrum berichtet in loser Folge über die Projekte des Ekompass-Förderkomplexes.

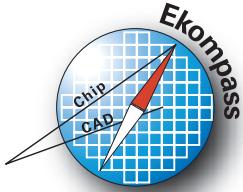

**Abbildung 1.01:**

Übersicht über die aktuellen Ekompass-Projekte.

| Projekt    | FKZ     | Laufzeit                | Projektkoordination                                      |

|------------|---------|-------------------------|----------------------------------------------------------|

| AIS        | 01M3083 | 01.12.2006 - 30.11.2009 | Dr. Volker Schöber, schoeber@edacentrum.de               |

| DETAILS    | 01M3071 | 01.04.2004 - 31.03.2007 | Reimund Wittmann, reimund.wittmann@nokia.com             |

| FEST       | 01M3072 | 01.07.2004 - 30.06.2007 | Dr. Volker Schöber, schoeber@edacentrum.de               |

| HERKULES   | 01M3082 | 01.12.2006 - 30.11.2009 | Dr. Hans-Werner Sahm, hsahm@alcatel-lucent.com           |

| MAYA       | 01M3172 | 01.06.2006 - 31.05.2009 | Dr. Sebastian Sattler, sebastian.sattler@infineon.com    |

| Parachute  | 01M3169 | 01.04.2006 - 31.03.2009 | Thomas Steinecke, thomas.steinecke@infineon.com          |

| PRODUKTIV+ | 01M3077 | 01.10.2005 - 30.09.2008 | Dr. Jürgen Alt, juergen.alt@infineon.com                 |

| Sigma65    | 01M3080 | 01.10.2006 - 30.09.2009 | Dr. Manfred W. Dietrich, manfred.dietrich@eas.iis.fhg.de |

| URANOS     | 01M3075 | 01.07.2005 - 30.06.2008 | Dr. Hans-Jürgen Brand, hans-juergen.brand@amd.com        |

| VeronA     | 01M3079 | 01.06.2006 - 31.05.2009 | Peter Jores, peter.jores@de.bosch.com                    |

| VISION     | 01M3078 | 01.05.2006 - 30.04.2009 | Dr. Joachim Gerlach, joachim.gerlach@de.bosch.com        |

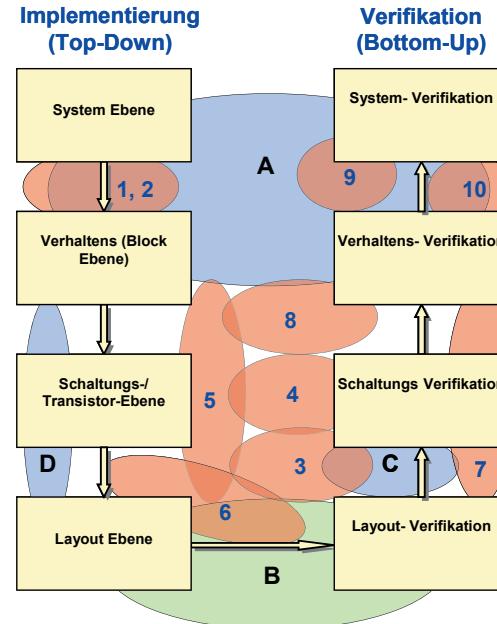

**Abbildung 1.02:**

Das Bild zeigt verschiedene Entwurfsvorgänge des Schaltungsentwurfs. Dabei sind die Schwerpunkte des Projektes DETAILS hervorgehoben, weil sich das Projekt DETAILS in dieser Ausgabe des Newsletters präsentiert.

# DETAILS

## DETAILS: Neue Möglichkeiten für die Konzipierung und den Entwurf von höchstintegrierten Endgeräten mit besonderer Berücksichtigung von eingebetteten HF-IP Baugruppen

R. Wittmann<sup>1</sup>, R. Kakerow<sup>1</sup>, Ch. Münker<sup>2</sup>, W. Schneider<sup>3</sup> and P. Birrer<sup>4</sup>

<sup>1</sup>Nokia GmbH, <sup>2</sup>Infineon Technologies AG, <sup>3</sup>Atmel Germany GmbH, <sup>4</sup>Cadence Design Systems GmbH

### Einleitung

Der weltweit steigende Bedarf an mobilen Kommunikationsdienstleistungen erfordert einen immer schnelleren Austausch von Informationen über bandbegrenzte Übertragungswege (terrestrisch, drahtgebunden, optisch). Anwendungsgebiete liegen beispielsweise in der Telekommunikation, dem Entertainment, der Gebäudeautomation und in zunehmendem Maße auch in der Medizintechnik. Zur Ausnutzung der zur Verfügung stehenden Übertragungsbandbreite bedarf es hochkomplexer Modulationsverfahren und Systemarchitekturen. Gleichzeitig sind die hohe Zuverlässigkeit, niedrige Kosten und ein geringer Energiebedarf (Batteriebetrieb) dieser Architekturen von besonderer Bedeutung. Daraus entstehen neue Herausforderungen an den Systementwurf und besondere Anforderungen an die Entwurfswerzeuge.

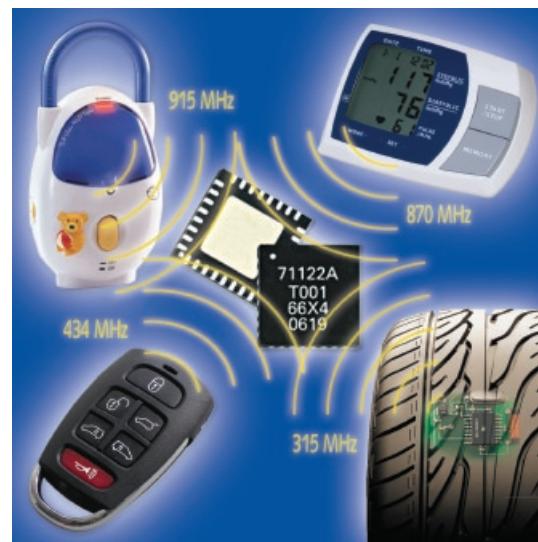

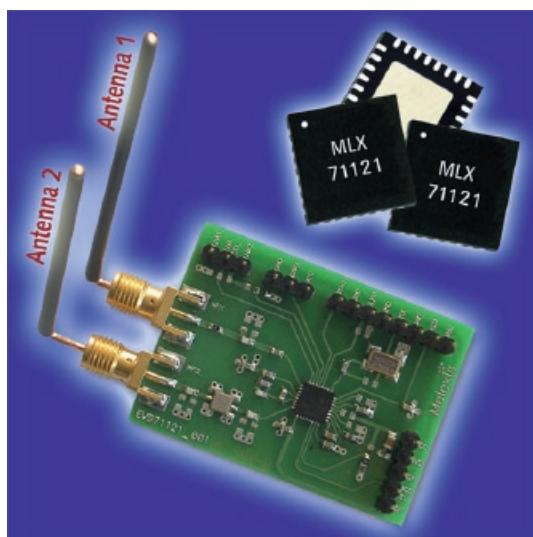

Das Projekt DETAILS (01M3071) konzentriert sich auf den Aufbau einer effizienten Entwurfstechnologie für wieder verwendbare, hochintegrierte Hochfrequenz-Schlüsselkomponenten in zukünftigen mobilen Kommunikationssystemen hoher Komplexität für Trägerfrequenzen bis 60 GHz. Die hier betrachtete HF-Entwurfstechnologie umfasst die Bereiche EDA-Entwurfsumgebungen und -Werkzeuge, Entwurfsmethodik, Modellierungsverfahren und die Schnittstelle zum Fertigungsprozess.

Der Anwender erwartet zuverlässige und kostengünstige Multi-Standard-Endgeräte und Dienste mit hohem Gebrauchswert für Anwendungen wie z. B. das zukünf-

tige mobile Internet. Mit den bisher verfügbaren Entwurfsverfahren können diese noch nicht bereitgestellt werden. Wichtig ist die Verkürzung der Entwicklungszeit bei gleichzeitiger Erhöhung der Planungssicherheit. Dazu gehören neue Entwurfsabläufe und Modellierungsverfahren zur sicheren Systemkonzipierung.

Aus dieser entscheidenden Bedeutung des Design-Flows leitet sich die Zuordnung der Arbeiten des Projekts in die vier Hauptbereiche HF-Systemmodellierung, HF-IP Entwurf, Prozessanbindung für HF-Systeme und HF-Entwurfsplattform ab. Der HF-Design-Flow ist hierbei das zentrale Bindeglied der durchgeführten Arbeiten zur Bereitstellung einer geeigneten Entwurfstechnologie. Im „newsletter edacentrum 02 2005“ wurden die Arbeitsbereiche mit den Forschungszielen bereits vorgestellt. Deshalb fasst dieser Bericht eine Auswahl wichtiger Forschungsergebnisse aus den unterschiedlichen Bereichen zusammen und verdeutlicht den erzielten technischen Fortschritt.

### Gigabit-Radio-Technologie für Funksysteme im Mikrowellen-Bereich

Zukünftige Telekommunikationssysteme werden durch ihre Komplexität und multidisziplinäre Ansätze die Leistungsfähigkeit konventioneller Entwicklungsumgebungen und Entwurfsmethoden in Frage stellen. Um auf die zu erwartenden Herausforderungen reagieren zu können, müssen schon jetzt beispielhaft Systeme mit extremen technischen Anforderungen wie hohen Datenraten, Signalbandbreiten, Rechenleistungen

**Zusammensetzung des Projektkonsortiums:**

**Projektpartner:**

- » Atmel Germany GmbH

- » Cadence Design Systems GmbH

- » Infineon Technologies AG

- » Melexis GmbH

- » Nokia GmbH

**Unterauftragnehmer:**

- » TU Cottbus

- » Fraunhofer-IIS EA

- » IMMS gmbH

- » TU Dresden

- » Universität Ulm

**Förderkennzeichnen:**

01 M 3071

**Laufzeit:**

01.04.2004–31.03.2007

**Homepage:**

[www.edacentrum.de/ekompass/projekte/details/](http://www.edacentrum.de/ekompass/projekte/details/)

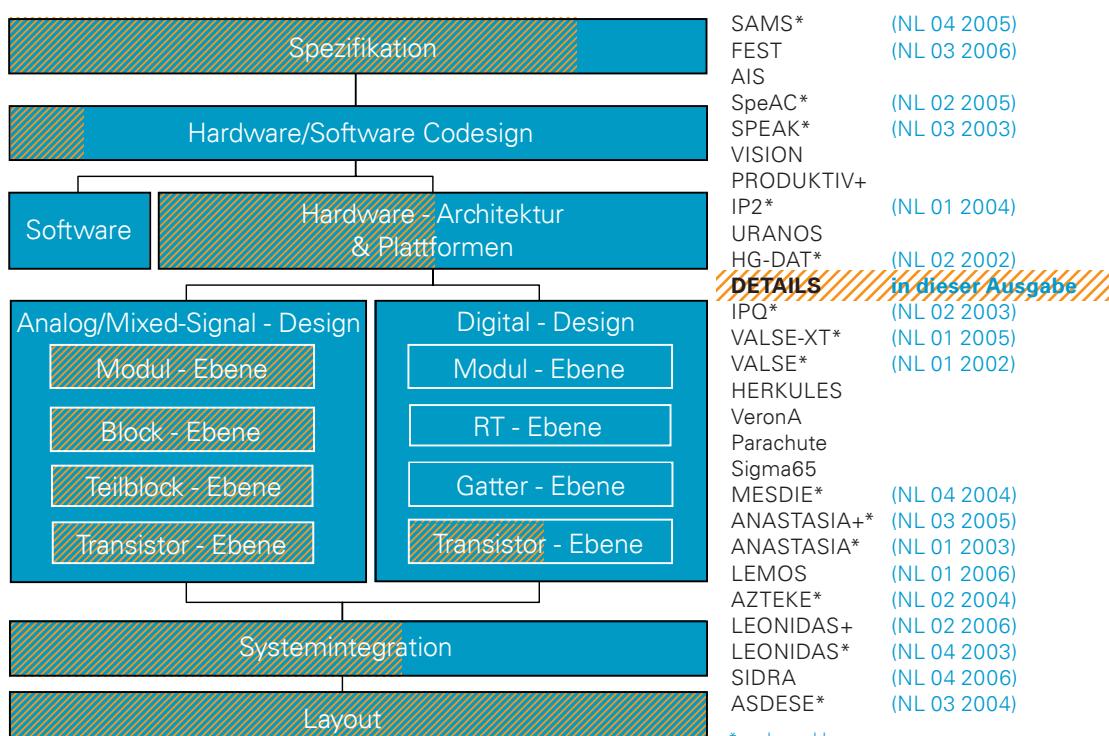

Abbildung 1.03: Konzeptdiagramm des Gigabit-Radio-Demonstrators

und Trägerfrequenzen betrachtet werden. Die daraus resultierenden Anforderungen an Designumgebung, Modellierung und Simulation müssen entsprechend analysiert und auf ihr Verbesserungspotential hinsichtlich Genauigkeit, Geschwindigkeit und Unterstützung für den Designer untersucht werden.

Die Gigabit-Radio-Technologie eignet sich auf Grund ihrer multidisziplinären Komplexität (Ethernet, digitale Signalverarbeitung, HF, Mikrowellentechnik) und ihrer technischen Herausforderungen (Trägerfrequenz, Signalbandbreite, Genauigkeit) hervorragend als Systembeispiel [1]. Hinzu kommt, dass bereits Messergebnisse von ersten Prototypen vorliegen, mit denen die erarbeiteten Modellansätze abgeglichen werden können.

Abbildung 1.03 zeigt das Blockdiagramm des im Projekt DETAILS betrachteten Gigabit-Radios. Eingehende Gigabit-Ethernet-Daten werden mit einer Datenrate von 1,25 GHz in den Sender eingespeist. Im Basisbandbereich werden die Daten mit einer  $\pi/4$  D-QPSK digital moduliert und gefiltert. Die Umsetzung in die analoge Domäne mit Hochsetzung auf eine Zwischenfrequenz (ZF) von 3 GHz findet im nachgeschalteten ZF-Front-End statt. Eine Mikrowelleneinheit mischt das Signal in den Mikrowellenbereich, wo es über Cassegrain-Antennen übertragen wird. Der Empfang erfolgt entsprechend, mit den erforderlichen Algorithmen zur Signalkorrektur, Taktrückerkennung, Filterung und Demodulation, im digitalen Basisband.

Die wesentlichen Entwurfsschritte und die Implementierung des Gigabit-Radios wurden bei Nokia als interne Entwicklung durchgeführt. Forschungsschritte im Entwurfsprozess, die als kritisch identifiziert wurden, konnten an die Förderprojekte DETAILS und SAMS zur Erarbeitung neuer Modellierungsansätze übergeben werden. Im Rahmen dieser Zusammenarbeit wurden Modelle erstellt, die eine Betrachtung des gesamten Übertragungssystems unter Einbeziehung relevanter physikalischer Parameter erlauben [2]. Die Verwendung von Hochsprachenmodellierung in Kombination mit analogen Beschreibungen, zum Bei-

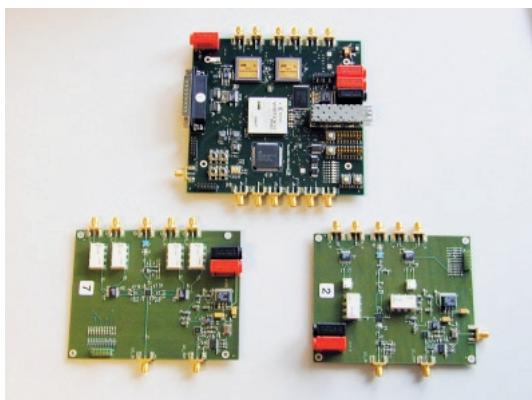

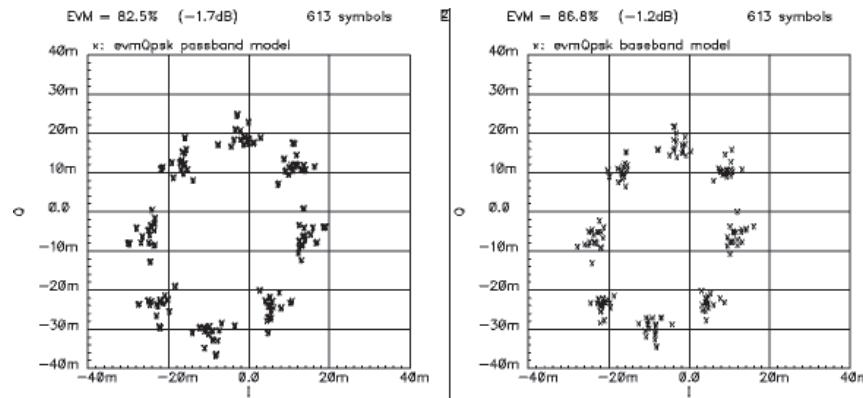

**Abbildung 1.04:** Gigabit-Radio-Modulator-Implementierung: Basisband (oben), HF/ZF Sender (links unten), HF/ZF Empfänger (rechts unten)

spiel basierend auf SystemC-AMS, ermöglichte eine Erfassung des Gesamtsystems mit den zur Verfügung stehenden Rechenressourcen. Anhand dieser Modelle konnte eine Evaluierung unterschiedlicher Entwurfsparameter durchgeführt werden.

Die Kernkomponenten der Referenzimplementierung des Gigabit-Radio-Modulators sind in Abbildung 1.04 zu sehen. Die Basisband-Signalverarbeitung wurde in einem FPGA implementiert, welches sich zusammen mit dem Gigabit-Ethernet-Interface, der Taktzeugung und den A/D- bzw. D/A-Umsetzern des Signalfades auf dem Basisband-Board befindet. Der Hochfrequenzteil des Modulators mit einer Zwischenfrequenz von 3 GHz wurde für Sender und Empfänger auf zwei Boards verteilt. Nicht abgebildet ist der Mikrowellen- teil, der das Signal auf die Trägerfrequenz im E-Band (74/84/94 GHz) hochsetzt.

Erste Tests mit dem erstellten Demonstrator ergaben eine gemessene Roh-Bitfehlerrate der Funkstrecke bei 84 GHz zwischen 10-7 und 10-4. Dieser Wert wurde ohne Kanalkodierung erreicht, die nun im Rahmen der Weiterentwicklung des Systems implementiert wird. Die im Rahmen von DETAILS und der Kooperation mit SAMS erarbeiteten Ergebnisse erlauben eine gezielte Optimierung der kritischen Parameter wie Linearität oder Jitter, indem geeignete Modellierungsansätze zur Verfügung gestellt werden.

### **Built-In Self-Test und Self-Calibration (BIST/BISC) für Hochfrequenzblöcke**

Aktuelle CMOS-Technologien mit ihren hohen Integrationsdichten ermöglichen hochintegrierte Systemlösungen, die HF-Transceiver und digitale Signalverarbeitung auf einem Chip vereinen. Allerdings sind diese Technologien mit Hinblick auf digitale Schaltungen optimiert und weisen zum Beispiel deutlich stärkere Parameterschwankungen und einen geringeren Dynamikbereich als spezielle analoge Technologien auf. Daher müssen Transceiverarchitekturen mit hohem Digitalanteil, wie Delta-Sigma-modulierte PLLs verwendet werden, um die benötigte Performance zu erzielen.

Diese komplexen Architekturen stellen, aufgrund der Funktionsvielfalt und der engen Wechselwirkung zwischen HF- und digitalen Komponenten, große Anforderungen an die Prüftechnik. Die resultierenden Testkosten machen mit steigendem Trend bis zu 25% der gesamten Produktionskosten aus [3] und müssen reduziert werden, um aufgrund des hohen Wettbewerbsdruck in der Halbleiterindustrie konkurrenzfähig zu bleiben.

Auf der anderen Seite eröffnet die hohe Integrationsdichte neuartige Möglichkeiten für kombinierte, effiziente Selbstabgleich- und Selbsttestalgorithmen: Built-In Self Calibration (BISC) / Built-In Self Test (BIST), die trotz komplexer digitaler Signalverarbeitungsalgorithmen nur wenig zusätzliche Chipfläche benötigen.

Die dadurch erzielten Ausbeuteverbesserungen und Testzeitverkürzungen gleichen die zusätzliche Fläche mehr als aus.

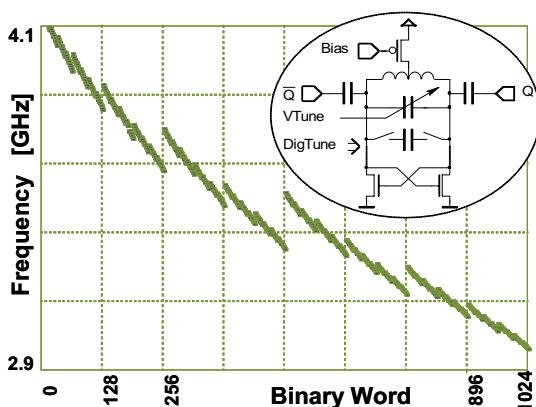

Abbildung 1.05: VCO mit 1024 Subbändern

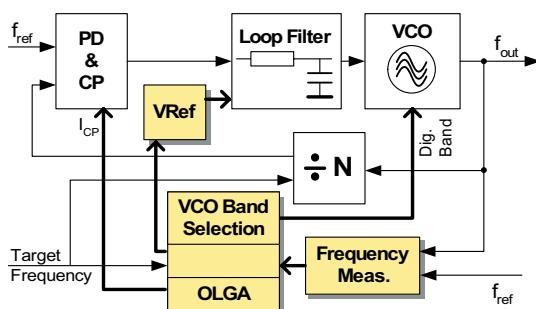

Im Rahmen von DETAILS wurden unter anderem Test- und Abgleichskonzepte für PLLs und VCOs untersucht. VCOs sind besonders problematische Komponenten in CMOS-Technologien, da die Streuungen von MOS-Varaktoren wesentlich höher sind als die von dedizierten Varaktoren in BiCMOS-Technologien. Die konventionelle Lösung, einen VCO mit großer Steilheit zu verwenden, um den geforderten Frequenzbereich unter allen Randbedingungen und Prozessecken abzudecken, macht das System sehr störanfällig und verschlechtert die Performance. Daher wurde der Tuningbereich in 1024 Sub-Bänder aufgeteilt, so dass eine niedrige Steilheit von 60 MHz/V genügt, um insgesamt 1.2 GHz abzudecken (Abbildung 1.05). Die Auswahl des geeigneten Bands geschieht innerhalb weniger  $\mu$ s mittels eines Successive-Approximation-Algorithmus (Abbildung 1.06).

Abbildung 1.06: Automatische VCO Kalibrierung und Test

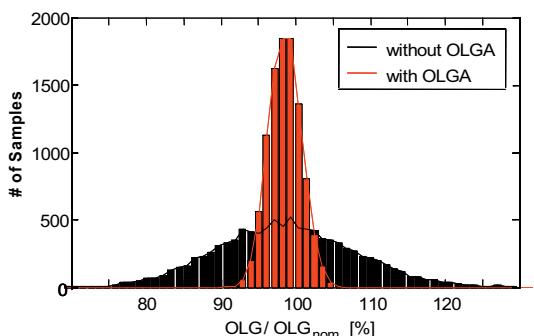

Darüber hinaus zeigt Abbildung 1.06 eine BISC-Methode, um Schleifenverstärkung und -bandbreite trotz schwankender Parameter (Open Loop Gain Automatic Adjustment, OLGA) konstant zu halten. Die entsprechende Reduktion der Streuung durch Open Loop Gain Automatic Adjustment, OLGA [4] ist in Abbildung 1.07 dargestellt.

Abbildung 1.07: Reduktion der Open-Loop-Gain Streuung durch BISC

Die schlechte Testbarkeit von HF-Blöcken, die in ein komplexes System-On-Chip eingebettet sind, macht digitale BISC-Konzepte besonders attraktiv: Indem man die BISC-Regelgrößen gegen Testlimits abprüft, erhält man eine effiziente BIST-Lösung, die langsame HF-Tests auf teuren HF-Testern ersetzen kann. Mit der Anordnung in Abbildung 1.4 ist es beispielsweise möglich, eine große Zahl relevanter VCO-Tests chipintern ohne externes Testequipment durchzuführen; auf Testchips konnte so die Testzeit um mehrere 100 ms verkürzt werden.

### Effiziente Methoden für den HF-IP-Schaltungsentwurf

Eine systemkonforme Modellierung für HF-IP's ist die Voraussetzung für eine höchstmögliche Flexibilität auf Systemebene, in der der bereitgestellte IP-Block und das dazugehörige Multilevel-Funktionalmodell keine starre Funktionalität besitzen, sondern auf spezielle Systemanforderungen hin formbar bleiben (parametrisierbar, konfigurierbar). Unter HF-IP werden hier in einer Hochsprache vorliegende, ausführbare Entwurfsbeschreibungen für die Bereiche Symbol, Modell, Schaltung und Layout verstanden.

Die möglichst automatische Erstellung von schnellen Verhaltensmodellen für RF-Blöcke stellt eine besondere Herausforderung dar, da es hier auf eine besonders hohe Modellierungsgenauigkeit ankommt. Die neue Methodik zur Generierung von Linearen-Transfer-Funktionen- (LTF-) Modellen ist als wichtiger Schritt in Richtung eines automatisierten Design-Flows zu sehen. Mit dieser Methodik können relevante Schaltungseigenschaften von der Transistorebene automatisch in Modelle für die Systemebene „übersetzt“ werden. Der zu modellierende Schaltungsblock wird hierbei als „Black-Box N-Port“ über S-Parameter charakterisiert. Aus diesen S-Parametern werden mit Hilfe der Vector-Fitting-Approximation alle Transferfunktionen einer beliebigen Übertragungsmatrix modelliert. Da bei diesem Verfahren die Modelleigenschaften automatisch aus den Eigenschaften von beliebigen Analogschaltungen abgeleitet werden können, ist diese Methode besonders wertvoll für die automatische Bottom-Up-Verifikation von komplexen Systemen. Die Schaltungstopologie spielt bei diesen

**Abbildung 1.08:**

Laufzeitintensives Modell in

Trägerfrequenzbereich (links)

und LTF-Modell für analoges

Front-End

Black-Box-Modellen keine Rolle; somit lassen sich hier die parasitären Effekte aus der Hochintegration besonders einfach berücksichtigen. Bei Funktionalmodellen, die sich aus der Schaltungstopologie ableiten, ist dies nicht so einfach möglich, da besonders im HF-Bereich zusätzliche parasitäre Elemente die Schaltungstopologie verändern können. Ein Vergleich der Genauigkeit zwischen der LTF-Modellierung und dem wesentlich aufwändigeren Modell im Trägerfrequenzbereich ist in Abbildung 1.08 gezeigt.

Durch die Verbesserung der Eigenschaften der Simulationsmodelle (Genauigkeit, Laufzeit) kann das Verhalten der Schaltungen und Systeme noch vor der Fertigung analysiert und optimiert werden. Dadurch lassen sich Ausbeuteverluste oder sogar Totalausfälle von kritischen HF-Komponenten vermeiden.

Neben der Verbesserung der Modellierung werden im Projekt DETAILS neue rechnergestützte Möglichkeiten untersucht, Qualität und Ausbeute von Analog- und HF-Schaltungen durch die gezielte Ausnutzung spezieller, für den HF-Entwurf bisher brach liegender Eigenschaften der Sub-100 nm Prozesse zu verbessern. Durch eine zuverlässige Integration von HF-Komponenten in Standardprozesse lassen sich für Produkte für den Massenmarkt Fertigungskosten einsparen. Da die komplette Signalverarbeitung auf nur einem Chip stattfinden kann, ergibt sich gleichzeitig die Möglichkeit einen erheblichen Teil der bisher benötigten Verlustleistung einzusparen und ein Potential für einen Gewinn an Datenrate und Rechenleistung.

Durch die Verkleinerung der Strukturgrößen und dem damit einhergehenden anwachsenden Integrationsgrad werden aufwändige Verfahren der statistischen Mittelung und der Selbstkalibrierung besonders interessant. Auch können nun Schaltungstopologien zum Einsatz kommen, die in der Vergangenheit aufgrund ihrer hohen Komplexität nicht berücksichtigt werden konnten. In der Projektarbeit wurden einige viel versprechende Ansätze untersucht, den störenden Auswirkungen von anwachsenden Einflüssen von Parameterschwankungen wirksam zu begegnen. Da sich diese Verfahren größtenteils nicht mehr durch den traditionellen Handentwurf adressieren lassen, galt es,

die durchzuführenden Entwurfsschritte auf geeignete Weise zu automatisieren.

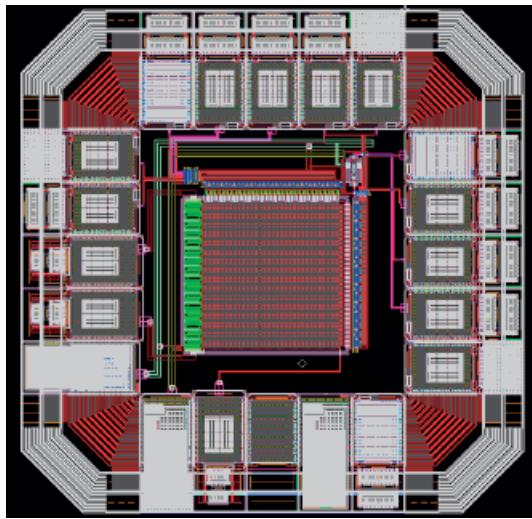

Mit dem Erreichen des 65 nm-Technologieknotens werden neue schaltungstechnische Möglichkeiten anwendbar, um den störenden Auswirkungen von Parameterschwankungen in Analogschaltungen zu begegnen. Anhand des in Abbildung 1.09 gezeigten Beispiels eines digitalen 1024-Stufen-Potentiometers wurde ein Bereich der Schaltungsoptimierung in den Vordergrund gerückt, der in der Vergangenheit oft nur am Rande betrachtet wurde, den einer varianz-freundlichen analogen Schaltungstechnik, die sich die hervorragenden Mittelungseigenschaften statistisch verteilter Einheitselemente gezielt zu Nutze macht. Dass zunehmende relative Parametertoleranzen der Bauelemente nicht notwendigerweise schlechtere Schaltungs- oder Systemeigenschaften nach sich ziehen müssen, konnte eindrucksvoll an diesem Beispiel demonstriert werden. Entgegen der üblichen Praxis, die Flächen von kritischen Bauelementen zu vergrößern, um den Einfluß statistischer Streuungen einzudämmen und die Matching-Eigenschaften zu verbessern, wurden hier die Flächen der Bauelemente (hier Widerstände) so weit wie möglich verringert. Die Matching-Genauigkeit der einzelnen Widerstände verschlechterte sich so auf etwa 5%. Solche Genauigkeitswerte sind für Präzisionsschaltungen wie zum Beispiel ein 10 Bit R-2R DAC völlig unbrauchbar. Der Widerstand für das MSB benötigt hier eine Genauigkeit von 0,1% für eine Linearität von 10 Bit, da der Spannungsabfall über diesem Widerstand 512 LSB Schritte entspricht (erlaubter Fehler 0,5 LSB). Verwendet man diesen Widerstand jedoch in einer potentiometrischen Topologie (10 Bit Umsetzer, Reihenschaltung aus 1024 Widerständen) bedeutet ein lokaler Fehler von 5% lediglich eine differentielle Nichtlinearität von nur 0,05 LSB, da der Spannungsabfall über jedem Widerstand etwa einem LSB entspricht. Man könnte für die integrale Nichtlinearität dieses Umsetzers nichts Gutes vermuten: Wenn die 1024 Einzelwiderstände jeweils einen Matching-Fehler von bis zu 5% haben können, so sollte der Gesamtwiderstand auch nur eine relative Genauigkeit von 5% haben (INL  $\leq 50$  LSB). Durch das Prinzip der statistischen Mittelung, bei der die Verteilungsfunktion der Parametersreuungen mit berücksichtigt wird, ist die tatsächlich

erzielte integrale Linearität jedoch mindestens um den Faktor 100 besser. Hierbei wird mittels Simulationen unter Berücksichtigung statistischer Schwankungen von vielen gleich dimensionierten Bauelementen, die an einem System beteiligt sind, eine bezüglich Spezifikation und damit Ausbeute optimierte Architektur ermittelt und erstellt. Gleichzeitig werden diese aus vielen Komponenten bestehenden Strukturen durch geeignete Layoutgeneratoren unterstützt. Dadurch kann das Gesamtsystem Einfluss auf die Gestaltung optimaler Einheitselemente nehmen. Für das Design wurde eine ausführbare Entwurfsablaufbeschreibung erstellt (GEM-Ansatz [5]). Es konnte festgestellt werden, dass die statistische Mittelung mindestens um den Faktor 4 genauer als die traditionellen Verfahren der Flächenvergrößerung sein kann, deren Grenze bei etwa 10 Bit Gesamtlinearität liegt und die einen wesentlichen höheren Flächenbedarf aufweisen.

Abbildung 1.09: Layout des digitalen Potentiometers in 65 nm CMOS

Mit Hilfe statistischer Verfahren erzielt die ausgewählte Schaltung eine Linearität von 10 Bit mit exzellentem Temperaturverhalten. Es wird kein spezielles Widerstandsmaterial verwendet, die Architektur kommt mit einfachem Gate-Poly aus und kann somit in reinen Digitalprozessen gefertigt werden. Eine mögliche Erweiterung in Richtung 12-Bit Grundgenauigkeit (4096 Stufen) wurde aus den aktuellen Messergebnissen hergeleitet.

Der hier gewählte Ansatz, die Ausbeute durch Mittelwertbildung aus vielen gleichen Referenzelementen zu erhöhen, ist auch für andere Anwendungen Erfolg versprechend. Er fördert die Robustheit gegenüber Störeinflüssen und ermöglicht intrinsische Qualitätsverbesserungen, die vielleicht noch über das hinausgehen, was durch eine alternative Kalibrierung der Schaltung von der Systemebene aus möglich ist. In Richtung zukünftiger Prozesstechnologien (< 65 nm) bedeutet Regularität im Analogdesign einen erheblichen Gewinn an Genauigkeit. In der Vergangenheit verhinderten die

Mindeststrukturgrößen mit einhergehenden Gradienteneffekten bei ausgedehnten Strukturen eine sinnvolle Anwendung dieses Prinzips. Der Flächengewinn vergrößert sich jeweils mit Übergang zum nächsten Technologieknoten und ermöglicht damit wie beim Digitaldesign eine Skalierung der benötigten Fläche in Abhängigkeit von den Prozessgeometrien.

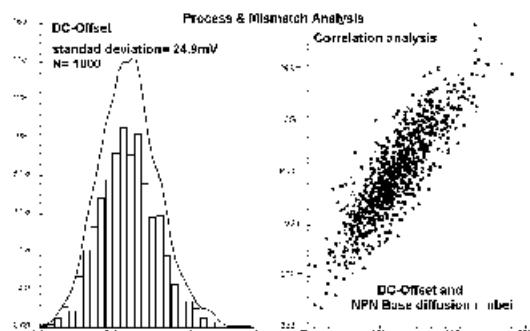

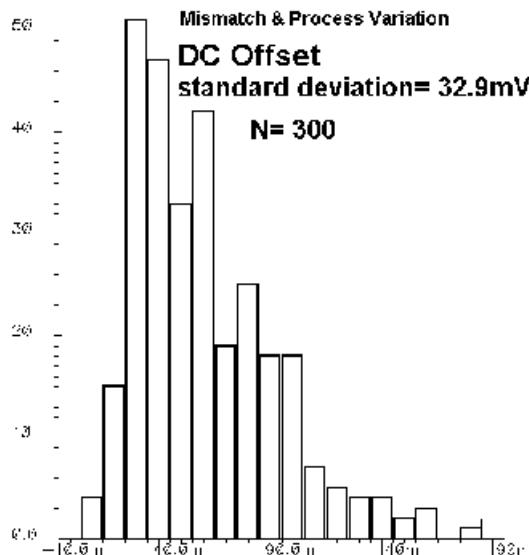

### Monte-Carlo-Simulation mit neuartigem statistischen Design-Kit

Eine optimale Korrelation mit der Statistik des technologischen Prozesses und durchgängig statistische Modelle sind erstmals in einem neuen Design-Kit implementiert. Damit werden für die Optimierung der Ausbeute und Zentrierung des Designs bereits in der frühen IC-Entwicklungsphase erweiterte Möglichkeiten eröffnet. Generiert wurden die Modellparameter dabei mit TRADICA, das neben den Geometriedaten direkt die Prozessparameter und die Prozessstatistik zur Parameter-Extraktion nutzt [6]. Das Design-Kit wurde im Rahmen des DETAILS Förderprojektes bereits praktisch vorgeführt.

#### Monte-Carlo- und Corner-Simulation

Um bereits in einer frühen Phase des IC-Design-Flows eine hohe Fertigungsausbeute zu garantieren und Redesigns zu vermeiden, werden schon seit längerer Zeit in der Schaltungsentwicklung Simulationswerkzeuge eingesetzt, welche die Auswirkungen der unvermeidlichen Parameterschwankungen des Fertigungsprozesses nachbilden. So wird für die Simulation von Grenzzuständen des verwendeten Prozesses die Corner-Simulation mit definierten Worst-Case-Zuständen eingesetzt. Für die Nachbildung der gesamten Prozessstatistik kommt die Monte-Carlo-Simulation zur Anwendung.

Bei digitalen CMOS-Schaltungen sind Slow/Fast-Kombinationen gängige Corner-Fälle. Bei Analogschaltungen spiegeln sich Streuungen der verschiedenen Prozessparameter jedoch ganz unterschiedlich im Verhalten der jeweiligen Schaltung wider. Beim hier vorgestellten Design-Kit wurden daher für die Modellierung der statistischen Prozessgrößen neue Wege beschritten: Ohne Umweg über elektrische Kenngrößen (Beta, Early-Spannung ...) werden skalierbare Modelle mit Hilfe des Expertensystems TRADICA direkt aus der geometrischen Beschreibung und den Prozessdaten bzw. der Prozess-Statistik generiert. Bauelemente und elektrische Kenngrößen, die von denselben Technologieparametern abhängen, behalten bei der Modellierung ihre Korrelationen bei. Ohne zusätzlichen Aufwand werden damit auch die statistischen Eigenschaften dieser Parameter im Modell abgebildet.

Voraussetzung dafür ist allerdings eine ausreichend große Datenbasis. Hierzu wurden die PCM- (Process-Control-Monitor) Strukturen ausgewertet, die mehrfach auf jedem produzierten Wafer platziert sind.

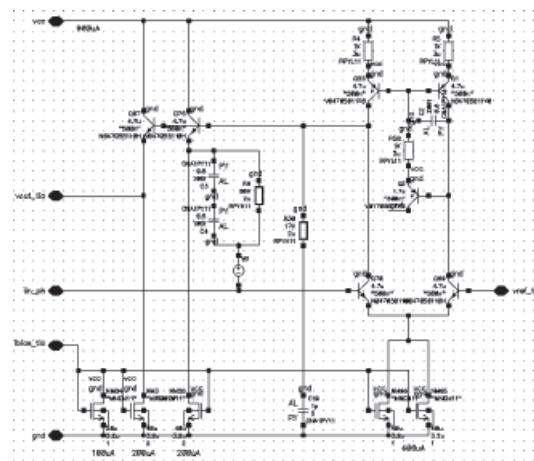

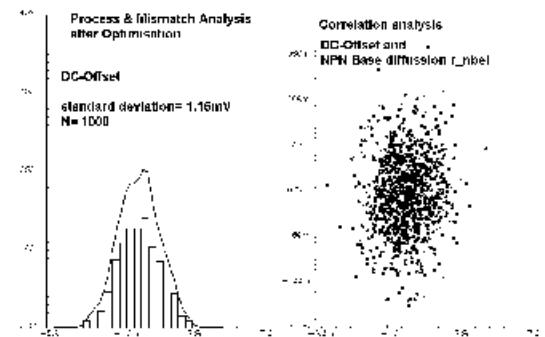

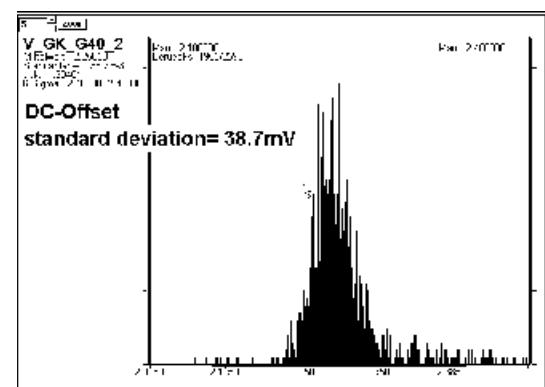

**Abbildung 1.10:** Schaltungsbeispiel

Das statistische Design-Kit in der praktischen Anwendung

Betrachtet wird die Analyse und Minimierung des DC-Offsets des in Abbildung 1.10 gezeigten Operationsverstärkers. Prozessparameter und Mismatch von Bauelementen können dabei separat oder gemeinsam statistisch simuliert werden. Das Ergebnis der kombinierten Analyse lässt direkt auf die zu erwartende Parameterstreuung nach dem technologischen Durchlauf schließen.

Die statistische Simulation der Prozessschwankungen ermöglicht Korrelationsbetrachtungen zwischen Prozessparametern (zum Beispiel Schichtwiderstände, Basisdiffusion, usw.) und den interessierenden Ausgangskenngrößen der Schaltung. Über die Auswertung der Korrelationskoeffizienten können diejenigen Prozessparameter identifiziert werden, welche die Schaltung maßgeblich beeinflussen. Es wird nun möglich, Corner-Fälle zu definieren, die auf die betrachtete Schaltung zugeschnitten sind. Auch die Wirkung einzelner Prozessparameter ist analysierbar, beispielsweise in einem Sweep von Prozessparametern.

**Abbildung 1.11:** Als Ergebnis der Monte-Carlo-Analyse erhält man die Streuung des DC-Offsets und die deutliche Korrelation mit NPN-base doping r\_nhei

Die Mismatch-Analyse bildet die Streuung benachbarter Bauelemente nach. Dabei werden die geometrischen Abmessungen mit ihrer charakteristischen Streuung hinterlegt, die aus besonderen PCM-Mismatch-Strukturen ermittelt wird. Da an jedem Bauele-

ment die Mismatch-Eigenschaft wählbar ist, können alle Bauelemente zusammen oder nur ausgesuchte Bauelemente allein statistisch simuliert werden. Das Ergebnis der Mismatch-Analyse gibt Hinweise auf kritische Abmessungen von Bauelementen. In Kombination mit einem sorgfältig ausgeführten IC-Layout können nun die Ergebnisse aus der statistischen Analyse erfolgreich umgesetzt werden.

In dem vorliegenden Beispiel wird die Schaltung sukzessive optimiert:

- » durch Einfügen einer Basisstrom-Kompensation

- » Bufferstufen sorgen für bessere Entkopplung

- » eine Kaskodestufe erhöht das Open-Loop-Gain.

Abbildung 1.11 zeigt die Analyse des DC-Offsets vor und Abbildung 1.12 nach der Optimierung durch die Mismatch-Analyse. Es ist klar zu erkennen, dass die Streuung des DC-Offsets durch die Betrachtung von technologiebedingten Korrelationen direkt bei der Modellierung im Design-Kit erfolgreich reduziert werden konnte.

**Abbildung 1.12:** Nach der Optimierung ist die Streuung des DC-Offsets minimiert und seine Abhangigkeit von NPN base doping  $r_{nbe}$  verschwunden.

## Praktische Erfahrungen

Das vorgestellte Verfahren hat sich bereits mehrfach an komplexen Schaltungen bewährt und ist auf alle Simulationsarten anwendbar (AC, Transient, PSS ...). Abbildung 1.13 zeigt eine gemessene Verteilung des DC-Offsets, die gut mit dem in Abbildung 1.14 gezeigten Modell übereinstimmt.

**Abbildung 1.13:** Gemessene Offsetverteilung einer komplexen Verstärkerstufe

| Nr. | Ergebnis                             | Partner                           |

|-----|--------------------------------------|-----------------------------------|

| 1   | SystemC-/AMS, Import Flow            | Cadence, Nokia, FhG               |

| 2   | Simulink-AMSD Cosimulation           | Atmel, Cadence, FhG               |

| 3   | Statistische Modellierung/TRADICA    | Atmel, TUD, Cadence               |

| 4   | Technologie Portierung BiCMOS - CMOS | Atmel, Infineon                   |

| 5   | GEM IP Generator                     | Nokia                             |

| 6   | Spulen Generierung & Design          | Cadence, Infineon, Nokia, Uni Ulm |

| 7   | Modellierung von 3D-Effekten         | Atmel, Cadence, CST, Nokia        |

| 8   | Block-Level RF BIST/BISC             | Infineon, Melexis/IMMS, TUD       |

| 9   | PLL-Verifikation mit SystemC         | Infineon                          |

| 10  | Basisband Modellierung/VCME          | Cadence, FhG, Infineon            |

**Tabelle 1.01:** Bereits in den Gesamtflow eingeflossene Knergebnisse aus DETAILS

**Abbildung 1.14:** Ergebnis der zugehörigen Mismatch- und Prozess-Simulation

**Abbildung 1.15:** Aus den Arbeitspaketen erzielte, flow-relevante Ergebnisse (1-10) im DETAILS-Gesamtflow – Demonstratoren: (A) Gigabit-Radio, (B) Hardware & Teststrukturen, (C) Demonstrator zur statistischen Modellierung, (D) Demonstrator zur Bus-Modellierung

## Einbettung der Ergebnisse in den Design-Flow

Abbildung 1.15 illustriert diejenigen in Tabelle 1.01 aufgeführten Forschungsergebnisse, die beispielhaft in einen DETAILS-Gesamtflow eingebunden und auf ihre Eignung im Entwurf überprüft wurden. Durch die Anwendung der Ergebnisse sind bisher insgesamt drei Demonstratoren sowie weitere Hardware und Teststrukturen entstanden.

### SystemC Import Flow

Trotz der wachsenden Komplexität moderner Kommunikationssysteme muss eine hohe Zuverlässigkeit bei gleichbleibend niedrigen Kosten und kurzen Produktzyklen erreicht werden. Nicht nur der Schaltungsentwurf, sondern auch die Verifikation muss deshalb auf höheren Abstraktionsebenen und über die Grenzen des Analog/HF- bzw. Digitalbereichs hinweg betrachtet werden. Dieses Ziel lässt sich durch neue, im Entwurf flexibel einsetzbare Schnittstellen zwischen der Systemebene und der Schaltungsimplementierung erreichen. Für die Analog/Mixed-Signal-Entwurfsumgebung von Cadence konnte exemplarisch eine SystemC-Modell-Importfunktion erstellt werden. Damit ist der Analog/RF-Designer nun in der Lage, komplette System-Testbenches bei der Entwicklung und Verifikation von eingebetteten Analog- und HF-Baugruppen

auf Transistorebene zu berücksichtigen. Die SystemC-Modelle sind nach dem Import ein Bestandteil der Analog/HF-Simulationsplattform. Dadurch werden Simulationen mit unterschiedlichen Verhaltensmodellen und Sprachen auf verschiedenen Abstraktionsebenen ermöglicht.

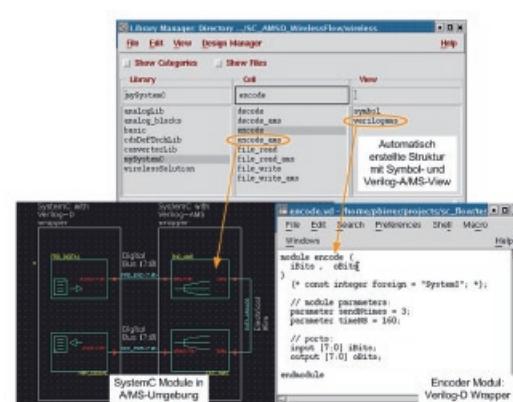

**Abbildung 1.16:** SystemC-Modell-Importfunktion implementiert in Cadence AMS-Designer.

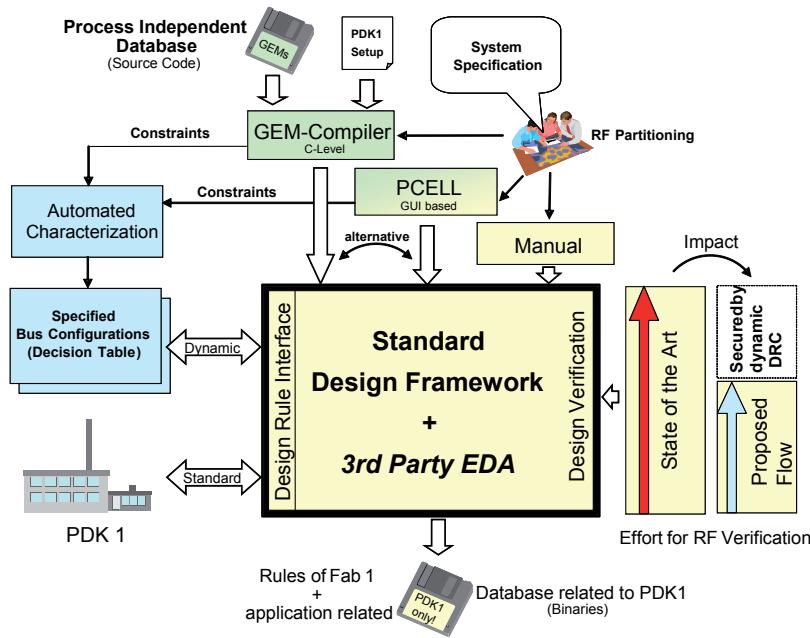

**Abbildung 1.17:** Die Kombination des GEM-Ansatzes mit dem partiellen Layout-Flow im DETAILS-Gesamtflow ermöglicht die automatisierte Generierung dynamischer Entwurfsregeln für planare Bussysteme.

Die SystemC-Modell-Importfunktion generiert automatisch Verilog-A/MS-Wrapper und Symbole. Die SystemC-Module werden, wie in einem Analogentwurf üblich, in einer Bibliotheksstruktur abgelegt (Abbildung 1.16, oben). Die Verbindung der importierten SystemC-Module zum Gesamtsystem ist durch die Verdrahtung der entsprechenden Verilog-Wrapper im Schematic gegeben (Abbildung 1.16, unten links). Ein Wrapper – beispielsweise Verilog-D für das SystemC Encounter-Modul – ist in Abbildung 1.16, unten rechts, dargestellt. Durch die Verwendung von Wrappern wird eine Kombination der so gekapselten SystemC-Module mit anderen Blöcken (Verilog-A/AMS, VHDL-AMS, Transistor-Level, etc.) ermöglicht.

Die in den heutigen Standard-Einwurfsprozessen übliche Top-Down-Übergabe von Zielspezifikationen für Systemkomponenten führt immer wieder zu Missverständnissen, Informationsverlusten und folglich zu Verzögerungen. Durch die SystemC-Modell-Importfunktion wird die Lücke zwischen der Systemebene und der Schaltungsimplementierung überbrückt, d.h., die Fehleranfälligkeit ist somit reduziert und die Effizienz wird stark verbessert.

#### Auswahltabellen für Bussysteme im Gesamtflow

Bedingt durch die wachsende Komplexität, die fortlaufende Miniaturisierung und Arbeitsfrequenzen im Gigahertzbereich gewinnt die optimale Gestaltung der On-Chip-Bussysteme immer mehr an Bedeutung. Der leitbahnzentrierte partielle Layout-Flow, der innerhalb des BMBF-Förderprojektes Leonidas+ (01M3074) entstanden ist, wurde in Kooperation mit dem Projekt DETAILS weiterentwickelt, so dass sich beliebige planare Buskonfigurationen automatisch im in Abbildung 1.17 dargestellten Gesamtflow nach Chipfläche, Datenrate, Übersprechen, Signalverzögerung und Verlustleistung charakterisieren lassen. Die so gemessenen

Werte werden in einer Tabelle abgespeichert und dienen als Basis zur automatisierten Generierung der dynamischen Entwurfsregeln [8] [9].

Dynamische Entwurfsregeln basieren auf der Schaltungsspezifikation und ergänzen die prozessspezifischen Entwurfsregeln, zum Beispiel die minimale Polysilizium-Breite. Dynamische Entwurfsregeln in Bussystemen sind beispielsweise das maximal erlaubte Übersprechen von der Störleitung zur Nachbarleitung, die maximale Leitbahn-Breite oder die minimale Datenübertragungsrate. Einige Bussysteme (zum Beispiel Coplanar-Busse mit GND/Signal/GND-Konfigurationen und Abschirmung) werden diese Regeln erfüllen können, andere Systeme nicht. Falls sichergestellt werden kann, dass die dynamischen Entwurfsregeln während des Entwurfs durchgängig berücksichtigt wurden, vereinfacht sich der Verifikationsaufwand erheblich. Falls beispielsweise die Entwurfsregel „erlaubtes Übersprechen kleiner als 40 dB“ erfüllt ist, muss das Übersprechverhalten nicht mehr zusätzlich verifiziert werden.

#### Zusammenfassung

Das Verbundprojekt DETAILS hat sich zum Ziel gesetzt, eine geeignete HF-Entwurfstechnologie zu erarbeiten, die es ermöglicht, Kommunikationssysteme mit wachsenden Anforderungen an Sicherheit, Qualität, Komplexität und Leistungsfähigkeit effizient, d.h. mit weniger Aufwand und in kürzerer Zeit zu entwickeln (bezogen auf heute eingesetzte Standardverfahren in verfügbaren Entwurfsumgebungen). Durch die Zusammenarbeit von System- und Chipherstellern, CAD-Firmen und Forschungseinrichtungen in diesem Projekt ist eine übergreifende Betrachtung der Problemkreise möglich. Die hier kurz vor Ende der Projektlaufzeit ausgewählten und vorgestellten Ergebnisse zeigen exemplarisch herausragende Möglichkeiten auf, bei

wachsenden Systemanforderungen und schwierigeren Rahmenbedingungen (Prozesstechnologien) effizient und schnell zu zuverlässigen, hochwertigen Systemlösungen zu gelangen. Hierbei wurden alle Schnittstellen zwischen den einzelnen Entwurfsebenen von der Systemspezifikation bis tief hinein in die Prozesstechnologie hinterfragt und Verbesserungsmöglichkeiten erarbeitet. Durch die direkte Zusammenarbeit mit den Projekten LEONIDAS+ und SAMS war es möglich, zusätzliche, gemeinsame komplexe Anwendungsbeispiele zu berücksichtigen, die sonst den Projektrahmen gesprengt hätten. Besonders hervorzuheben sind hier das Gigabit-Radio mit 94 GHz Trägerfrequenz und das Szenario planarer Bussysteme. Neben neuen Simulations- und Modellierungsverfahren spielt die Automatisierung von komplexen Entwurfsschritten eine Schlüsselrolle in der erarbeiteten Entwurfstechnologie. Erst die Einbindung aller Lösungen in einen gemeinsamen Design-Flow garantiert deren Anwendbarkeit.

Hervorzuheben sind auch einige „Überraschungen“ bei den Ergebnissen, die die Bedeutung von Automatisierungs- und Modellierungstechniken für die Zukunft für den HF- und Analogbereich noch stärker betonen und auch Impulse für neue Forschungsprojekte geben. Traditionell wird Automatisierung und Modellierung dazu verwendet, schnell und sicher ein vorgegebenes Entwurfsziel zu erreichen. Im Projekt konnte gezeigt werden, dass durch Automatisierung auch Innovationen im Bereich Schaltungsentwicklung angestoßen werden können, die manuell aus Kosten- und Zeitgründen nicht mehr realisierbar wären. Modellierung ist nicht nur im Bereich der Verhaltensmodellierung für die Verifikation sinnvoll, sondern auch im besonderen Bereich der Entwurfsablaufbeschreibungen (GEM-Ansatz) zur Generierung der unterschiedlichen Design-Views (Layout, Schaltbild, Verhaltensmodell und Testbench). Eine weitere wichtige Erkenntnis ist, dass qualitativ hochwertige Systeme nicht notwendigerweise aus qualitativ hochwertigen Bauelementen aufgebaut werden müssen. Teilweise lassen sich Nichtidealitäten der Bauelemente durch geeignete Architekturauswahl, automatische Kalibrierung oder spezielle Designtechniken auf Architekturebene wieder auffangen. Von

besonderer Bedeutung ist dies für die HF- und Analogschaltungstechnik ab 65 nm-CMOS und darunter.

## Literatur

- [1] R. Kakerow, "Gigabit Radio Technology for directive wireless microwave point-to-point links". Kooperationsworkshop "System Planning", edacentrum, 30 Nov 2006, Hannover

- [2] U. Knöchel, R. Kakerow, W. Hartong, R. Frevert, E. Hemming, P. Birrer, "Analyse eines Gigabit-Funksystems mit AMS Designer". Analog 2006, 27–29 Sep 2006, Dresden, Germany.

- [3] International Technology Roadmap for Semiconductors, 2005 Edition, Test and Test Equipment.

- [4] Christian Münker, "Reduction of PLL Loop Gain Variations by Digital Calibration", Präsentation auf dem edacentrum Kooperations- und Fachworkshop "Modellierung & Simulation unter Berücksichtigung von Prozessschwankungen", Hannover, Deutschland, Nov. 2005

- [5] R. Wittmann, W. Schardein, R. Kakerow, J. Bahr, "Robuster analoger Schaltungsentwurf für Sub-100nm Prozesstechnologien mittels statistischer Methoden", GMM Fachbericht "Analog '06 – Entwicklung von Analogschaltungen mit CAE Methoden", Band 196, VDE Verlag, September

- [6] Kraus, W. : PCM- and Physics-Based Statistical BJT Modeling Using HICUM and TRADICA, 6th HICUM Workshop, 2006

- [7] Schröter, M., Wittkopf, H., Kraus, W.: Statistical modeling of high-frequency bipolar transistors, Proc. BCTM, pp 54 - 61, 2005

- [8] A. K. Momin, R. Wittmann, M. Bücker, W. Schardein, "Planar transmission line structures as possible on-chip interconnects in deep sub-micron processes", 10th IEEE International Workshop on Signal Propagation on Interconnects, SPI 2006, 9–12 May 2006, Berlin

- [9] P. Birrer, S. J. Chandrasekaran, R. Wittmann, „Partieller Layout Flow zur Generierung von Auswahltabellen für Bussysteme“, akzeptiert für 1. GMM/GI/ITG – Fachtagung „Zuverlässigkeit und Entwurf“, 27–28. März 2007

## Kont@kt (DETAILS):

Reimund Wittmann

Projektkordinator

Nokia GmbH

Meesmannstr. 103

44807 Bochum

fon: (02 34) 9 84-34 80

fax: (02 34) 9 84-34 91

reimund.wittmann@nokia.com

# HERKULES: Hardwareentwurfstechnik für Null-Fehler-Designs

**Ziel von HERKULES ist es, einen Großteil der bei der Verifikation der Kommunikationsstruktur anfallenden Aufgaben formal durchzuführen, höchste Qualität mit überlegener Produktivität zu koppeln und diese Qualität zu einem Produktvorteil zu machen. Für die Verifikation des Gesamtsystemkonzepts wird die simulationsbasierte Verifikation weiterhin benötigt werden. Sie wird aber durch HERKULES-Techniken von einer Fülle von Aufgaben der Codeverifikation entlastet, die so weit besser bewältigt werden können.**

## Ein verdecktes Problem – Folgekosten von Hardwarefehlern

Die Gesellschaft hat sich daran gewöhnt: Hardware- und Softwaresysteme sind so komplex geworden, dass Fehlfunktionen unvermeidlich sind. Immer wieder wird diese Zwangsläufigkeit anhand schwerer Unfälle oder wirtschaftlicher Schäden in großer Höhe medienwirksam in Szene gesetzt. So schwerwiegend solche Fehlfunktionen sind, und so wichtig es ist, die Fehlerfolgen zu diskutieren, geht es im industriellen Alltag vielmehr um die Auswirkungen von Fehlern im Allgemeinen.

Je nach Branche muss die Industrie extrem viel Zeit und Geld investieren, um das Restfehlerrisiko zu minimieren. Dennoch, Fehler werden gemacht, und daher sind die Entwicklungsprozesse für IT-Produkte so angelegt, dass Fehler auch dann noch durch „Patchen“ (Nachbessern) behoben werden können, wenn sie – oft lange nach ihrer Entstehung – gefunden werden. Ganze Abteilungen und Firmen leben von solchen „Patchworks“, die allerdings über die Zeit ein ursprünglich wohlstrukturiertes System in ein nicht mehr beherrschbares „digitales Monster“ verwandeln können. Man verwaltet Fehler eher, als diese gleich nach ihrer Entstehung zu eliminieren – da korrekter Code nach dem Stand der Kunst nicht möglich ist. Diese eingefahrene Praxis hat ihren Preis. Die „Veredelungskette“ einer Hardwaresteuerung, eines sogenannten Mikrocontrollers, soll dies verdeutlichen:

### Zusammensetzung des Projektkonsortiums:

#### Partner:

Concept Engineering GmbH

Infineon Technologies AG

Alcatel-Lucent

Melexis GmbH

OneSpin Solutions GmbH

Robert Bosch GmbH

#### Unterauftragnehmer:

IMMS Ilmenau

Technische Universität Chemnitz

Technische Universität Kaiserslautern

Universität Bremen

Universität Duisburg-Essen

Universität Karlsruhe

Zeilen Code des zugehörigen Designs. Diese Fehler – dokumentierte wie undokumentierte – verursachen zusätzlichen Aufwand und Risiken in den nachfolgenden Wertschöpfungsstufen, denn der Programmierer des Controllers muss neben dem normalen auch noch das „außerplanmäßige“ Verhalten der Hardware verstehen und bei der Programmierung berücksichtigen. Der Maschinenbauer, der danach diese Steuerung in seine Maschine einbaut, stößt bei der Integration auf unerwartetes – manchmal unerwünschtes – Verhalten, das nachzubessern ist. Schlimmstenfalls wird ein Anlagenbauer, in dessen Anlage diese Maschine arbeitet, mit teuren Produktionsausfällen beim Einsatz seiner Anlage konfrontiert.

Der Preis eines Standard-Mikrocontrollers rangiert zwischen Cents und wenigen Euro. Die oben ange deuteten Folgekosten von Fehlern dieser Controller liegen dagegen um viele Größenordnungen über diesem Preis. Aufgrund der millionenfachen Verbreitung solcher Hardwarebausteine liegt daher in der Verfügbarkeit korrekter Controller (s. u.) ein enormes volkswirtschaftliches Einsparpotential. Im Übrigen deuten erste Umfragen bei Nutzern solcher Bausteine darauf hin, dass der Markt die Hersteller korrekter Mikrocontroller mit verstärkter Nachfrage und höheren Preisen „belohnen“ würde, wenn es sie denn gäbe. Diese Hersteller würden sogar in doppelter Weise profitieren, denn mittlerweile müssen sie einen wachsenden „software content“ mit ihren Hardwareprodukten liefern und wären daher selbst Nutznießer des o. g. Einsparpotenzials an Fehlerfolgekosten.

## Durchbruch in der Entwurfstechnik

Im Rahmen des Projekts VALSE „Hochautomatisierte, zertifizierende und skalierende Validierung von System-on-Chip-Entwürfen“ wurde innerhalb von 4 Jahren eine Entwurfstechnik geschaffen (formale Modulverifikation), die das Gros der Fehler (sog. funktionale Fehler im Gegensatz etwa zu Produktionsfehlern) in Mikrocontrollern und vielen anderen Hardwarebausteinen zu eliminieren vermag. Während bei VALSE noch die Aufbereitung der formalen Basistechnik für die Anwendung auf industrielle Schaltungen im Vordergrund stand, verschob sich der Schwerpunkt der Arbeiten im

Nachfolge-Projekt VALSE-XT auf die systematische Beschaffung und Analyse einer verlässlichen formalen Spezifikation, die dann als Eingabe für formale Prüfverfahren diente. Im BMBF-Projekt VERISOFT wird diese Technik – ergänzt um weitere Beweisverfahren – eingesetzt, um in einem weit vorangeschrittenen, weltweit einmaligen Großversuch nachzuweisen, dass die Entwicklung eines modernen eingebetteten 32-bit-Mikrocontrollers ohne funktionale Fehler technisch machbar und wirtschaftlich ist.

Die neuen Verfahren zur Entwicklung korrekter Hardwarebausteine ermöglichen aber nicht nur die oben diskutierten Produktvorteile. Messdaten aus den VALSE-Projekten und VERISOFT zeigen, dass sich darüber hinaus höchste Qualität mit hoher Produktivität der neuen Verifikationstechnik paart.

#### **Umsetzung – technische und mentale Hürden**

Produktvorteile sowie massive Qualitäts- und Produktivitätsgewinne sind starke Argumente für eine neue Entwurfstechnik. Dennoch sind bei der Umstellung von der heutigen auf Simulation beruhenden Verifikationspraxis auf die neuen Verfahren erhebliche Hürden zu überwinden:

Ausbildung, Werkzeuge, Methodik und Designsysteme müssen aktualisiert werden. Hinter diesen Verfahren muss ein verlässliches kommerzielles Angebot mit ausreichenden Schulungskapazitäten stehen. Vor allem aber muss sich die Herangehensweise ändern. Diese ist in der Mikroelektronikindustrie auf die Funktion eines Chips, seine Herstellungskosten und das Zeitfenster mit den größten Marktchancen fixiert. Qualität wird nur vereinzelt als differenzierendes Produktmerkmal gesehen. Dass solche Einstellungen schnell ins Wanken kommen und dann hohe Kosten verursachen können, zeigt das Beispiel des Dieselfilters. Dieser hat nichts mit der hochoptimierten Funktion deutscher Dieselaggregate zu tun. Dennoch entsteht plötzlich durch mehr oder weniger berechtigte öffentliche Meinung und Gesetzesvorlagen massiver Druck auf die Automobilhersteller, ihre Emissionswerte für Dieselschadstoffe zu verbessern. Ansonsten drohen Marktpositionen und Image beeinträchtigt zu werden. Den Feinstaubpartikeln entsprechen bei den Hardwarebausteinen „schwer zu findende“ Fehler, die von den neuen Verfahren systematisch „herausgefiltert“ werden. Veränderungsdruck könnte hier von der Produkthaftung oder – besser – von Nachfrage und Marktchancen ausgehen.

#### **Der nächste Durchbruch – von korrekten Hardwarebausteinen zu korrekten Hardwaresystemen**

Früher wurden Hardwaresysteme ausschließlich durch Verdrahtung von Chips auf einer Leiterplatte gebaut. Mit heutiger Fertigungstechnologie kann die Funktionalität kompletter Leiterplatten auf einem einzigen Chip, einem so genannten System-on-Chip (SoC), integriert werden. So werden Verbesserungen bezüglich Fläche,

Stromverbrauch und Robustheit möglich, die Produktinnovationen quer durch alle Branchen treiben.

Die Charakterisierung dieser SoC ist eine Ansammlung von Superlativen: Ein solcher Chip enthält bis zu einige Hundert Millionen Transistoren und wird von Hunderten von Entwicklern in ca. 18 Monaten entwickelt. Die Umsatzerwartungen liegen jenseits von 500 Millionen Euro. Auch die Fehlerrisiken sind spektakulär: Die Suche nach Designfehlern verschlingt über 60 % des FuE-Budgets. Schwere Fehler, die nur beim Test erster Chips gefunden werden, erfordern oft mehrere „Respins“, die jeweils schon bald über 1 Million Euro kosten werden. Unterschätzte Verifikationsaufwände, die die Markteinführung um 3 Monate verzögern, können bis zu 25 % des erwarteten Umsatzes vernichten.

Selbst große Firmen können sich daher nur wenige solcher aufwändigen Entwicklungen zeitgleich leisten. Ihr Schicksal und erst recht das kleinerer Firmen hängt davon ab, die Risiken bezüglich Marketing, Entwicklung und gegebenenfalls der Produktion weniger großer Chips zu meistern. An die Stelle einer Risikoverteilung über viele kleine Chips tritt eine Auslese nach dem Prinzip „Alles oder Nichts“.

Zeit ist bei der Entwicklung eines SoC die knappste Ressource. Daher kann ein solcher Chip nicht vollständig neu entwickelt werden. Ein Großteil seiner Funktionalität muss aus vorgefertigten Designs häufig benötigter Bausteine – so genanntem Intellectual Property (IP), d. h. Designs von Prozessoren, Peripheriebausteinen, Speichern usw. – „zusammengesteckt“ werden. Das Zusammenwirken dieser IP gemäß einer hoch komplexen Kommunikationsstruktur erbringt dann die geforderte Systemfunktionalität. Die Anpassung des SoC an Besonderheiten von Kunden erfolgt über Software.

Abgesehen von der Beherrschung der weiteren Miniaturisierung sind Mängel in der Designqualität (s. o.) das größte Risiko bei der Entwicklung eines SoC. Die Antwort der EDA-Industrie auf diese Probleme heißt vereinfacht „mehr Simulation, mehr Rechner und mehr Personal“. Dies ist nach Einschätzung der Projektpartner keine zukunftsfähige Lösung. Denn die prinzipiellen Grenzen der Simulation und die damit verbundenen Bedrohungsszenarien werden von der Fachwelt einstimmig anerkannt.

Vereinfacht gesagt, besteht ein SoC aus IP und einer hoch komplexen Kommunikationsstruktur. Technisches Ziel von HERKULES ist es, einen Großteil der bei der Verifikation der Kommunikationsstruktur anfallenden Aufgaben formal durchzuführen. Dabei wird auch hier wieder unter maximaler Nutzung der VALSE- und VALSE-XT-Ergebnisse versucht, höchste Qualität mit überlegener Produktivität zu koppeln und diese Qualität zu einem Produktvorteil zu machen. Sicherheitshalber sei betont: Für die Verifikation des Gesamtsystemkonzepts wird die simulationsbasierte Verifikation

weiterhin benötigt. Sie wird aber durch die VALSE- und HERKULES-Techniken von einer Fülle von Aufgaben der Codeverifikation entlastet.

In **HERKULES-1, „Basistechniken“**, werden die algorithmischen Grundlagen für das Vorhaben geschaffen: Diese Algorithmen automatisieren die in HERKULES-2 und -3 beschriebenen Verifikationsaufgaben zu großen Teilen.

In **HERKULES-2, „2-Punkt-Kommunikation“**, werden formale Verifikationslösungen für die Kommunikation von zwei Modulen entwickelt. Bedarf an solcher Integrationsverifikation besteht prinzipiell bei jedem Schaltungsentwurf und insbesondere in der Kommunikationstechnik mit ihren vielen aufeinander folgenden Blöcken zur Bearbeitung der Kommunikationsdaten. Die zu erforschenden Verfahren erleichtern die Fehlerlokalisierung, verlagern die Integrationsverifikation auf einen früheren Zeitpunkt und finden letztlich alle funktionalen Integrationsfehler. Der Austausch von Chips im Feld, die aufgrund solcher Fehler nicht funktionieren, wird damit komplett vermieden.

In diesem Arbeitspaket sind auch die Leitanwendung der HERKULES-Technik auf Kommunikationsbausteine für Datenübertragungsnetze und die Verifikation eines LIN-Knotens platziert:

Die SDH-Protokolle (Synchrone Digitale Hierarchie) wenden statisches (leitungsorientiertes) Routing an, um die Wege der Rahmen im optischen Netz festzulegen. Die neuesten Systeme verbinden die statische Wegwahl des SDH-Standards mit der dynamischen, paketorientierten Wegwahl wie beispielsweise im Internet Protokoll (IP). Diese Verbindung von dynamischen und statischen Routing-Protokollen hat einen erhöhten Maintenance- und Monitoring-Aufwand seitens der Netzbetreiber zur Folge. Es müssen z. B. komplizierte Quality-of-Service- (QoS) Abfragen in ASICs implementiert werden, die in den zugrunde liegenden Standards nicht bis in jede Einzelheit definiert wurden. Angesichts dieser „weichen“ Standards simulativ die nötige Verifikationssicherheit zu erlangen, ist mit immensem Zeitaufwand verbunden.

Daher werden die o. g. dynamischen Routingprotokolle einschließlich ihrer QoS-Abfragen häufig mit FPGAs implementiert, um so aufwandsarm im System nachbessern zu können. FPGAs sind jedoch in ihrem Durchsatz und in ihrer Größe limitiert und auch das Nachbessern „im Feld“ ist dem Image des Systemherstellers abträglich. Die formale Aufarbeitung der Standards und die Bereitstellung von Bibliotheken von formalen Verifikationskomponenten (FVC) für die neuen Datenübertragungsprotokolle steigern die Verifikationssicherheit um Größenordnungen und verkürzen die Entwicklungszeit.

In **HERKULES-3, „Mehrpunktkommunikation“**, wird die Korrektheit von Bussystemen adressiert. Solche Systeme sind das Rückgrat von SoCs, und Fehlfunktionen in diesem Bereich haben oft gravierende Auswirkungen. Die geplante Aktivität soll fehlerfreie Kommunikation sichern und die Fehlerfindung auf die Phase der Modulverifikation vorverlegen, wo die Fehlerlokalisierung vergleichsweise einfach und die Fehlerkorrekturen kostengünstig sind. Zusätzlich soll der Aufwand in der Systemsimulation deutlich sinken, weil anders als in der heutigen Praxis keine Kommunikationsfehler mehr zu identifizieren und zu beheben sind.

In **HERKULES-4, „Methodik“**, sollen die in VALSE-XT und HERKULES entwickelten technischen Verfahren methodisch so aufbereitet werden, dass sie sowohl für Anbieter von integrierten Schaltungen als auch deren Anwender bzw. Integratoren insbesondere unter dem hohen Qualitätserfordernis „Null-Fehler-Design“ einsetzbar werden. Dabei sollen verschiedene Sichtweisen auf die Verifikationsaufgabe berücksichtigt werden. Neben der rein technischen Betrachtung wird beschrieben werden, wie Verifikationsprojekte unter Einbeziehung von HERKULES-/VALSE-XT-Technologie zu planen und zu überwachen sind. Für die administrative Ebene technischer Überwachung insbesondere sicherheitskritischer Anwendungen soll am Beispiel der Automobilelektronik eine geeignete Zertifizierungsmethodik entwickelt werden, die mit Hilfe der HERKULES-Technologie geltende Qualitätsstandards bzw. Normen erfüllt.

#### Kont@kt (HERKULES):

Hans Sahm

Alcatel Lucent Deutschland AG

O-TH14 Optical Networking

Thurn- und Taxisstr. 10

90411 Nürnberg

fon: (09 11) 5 26-26 38

hsahm@alcatel-lucent.com

Weitere Informationen sind unter <http://www.edacentrum.de/herkules/> zu finden.

# SAMS: Struktursynthese von analogen Schaltungen

Schlussbericht von Volker Schöber, Christoph Grimm, Roland Jancke, Lars Hedrich, Sorin Huss und Helmut Gräb

Digitale Schaltungen werden heute in weiten Teilen automatisiert entworfen. Möglich ist das durch den Syntheseprozess, der eine Spezifikation stark automatisiert in ein Layout umsetzt. Ein vergleichbarer Syntheseprozess existierte für analoge Schaltungen bislang nicht. Die im Rahmen des Clusterforschungsprojekts SAMS entwickelten Methoden und Verfahren demonstrieren einen nachweislich gangbaren Weg zur Synthese analoger Schaltungen. Dabei wird eine Spezifikation zunächst interaktiv zu einer Struktur aus grundlegenden Schaltungsprimitiven (z.B. Operationsverstärker, etc.) verfeinert. Für diese grundlegenden Schaltungsprimitive werden dann mögliche Topologien erzeugt und automatisch verglichen. Die Machbarkeit wurde im Projekt mit zwei Industriebeispielen erprobt. Weitere Forschung und Entwicklung ist aber notwendig, um die Vielzahl der analogen Schaltungsarten zu erfassen, damit der eingeschlagene Weg zur analogen Schaltungssynthese ein industriell einsetzbarer Entwurfsprozess wird.

## Problembeschreibung

Der Entwurf analoger Schaltungen kann in die Aufgaben Architekturesynthese, Topologiesynthese und Dimensionierung sowie Layoutsynthese strukturiert werden. Für Architektur- und Topologiesynthese gibt es bislang nur punktuelle Ansätze. Bei der Architekturesynthese wird ein Blockdiagramm optimiert und auf Grundschaltungen abgebildet. Dabei müssen insbesondere die Ressourcen des Gesamtsystems auf die Komponenten verteilt werden. Bei der Topologiesynthese, auch Schaltungssynthese genannt, wird für die Komponenten eine Schaltungsstruktur aus elektronischen Bauelementen erzeugt. Die Dimensionierung bestimmt konkrete Größen elektrischer Parameter aus einem immer noch sehr großen Raum an Möglichkeiten. Erst nach der Dimensionierung und gegebenenfalls erst nach dem Layout lassen sich die elektrischen Eigenschaften von Schaltungen genau bestimmen. Die häufig schwer vorhersagbare Abhängigkeit der Architektur- und Schaltungssynthese von Dimensionierung und Layout machen die Strukturwahl anscheinend zur „schwarzen Magie“, die nur mit jahrelanger Erfahrung zu beherrschen und kaum zu automatisieren ist.

## Lösungsansatz von SAMS

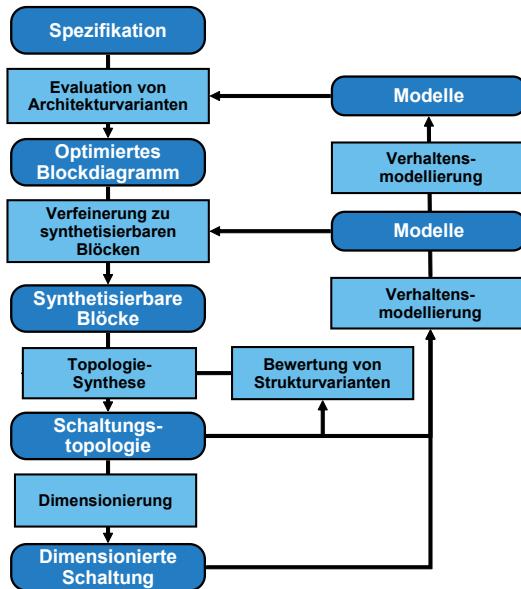

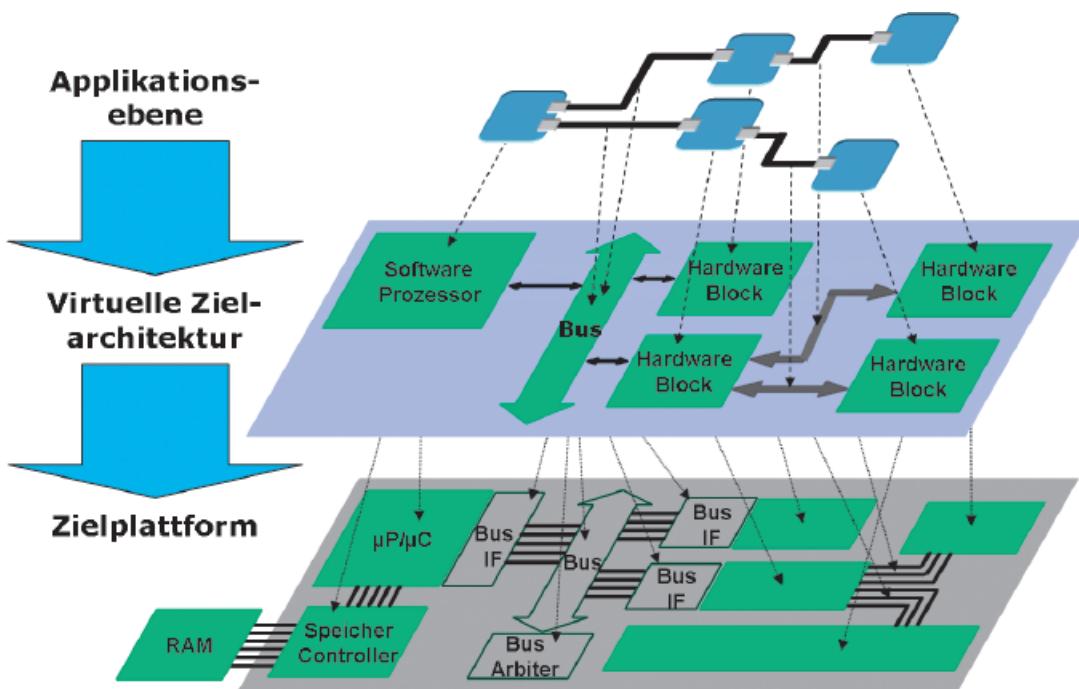

Bislang existierten keine Werkzeuge oder Entwurfsprozesse, die Architekturesynthese und Schaltungssynthese in einem Flow durchgängig unterstützen. Einen durchgängigen Entwurfsprozess zu demonstrieren war Ziel des Clusterforschungsprojekts SAMS (Abbildung 1.18). Als Ergebnis wird deutlich, dass die durchgän-

gige und automatische Synthese von komplexen Mixed-Signal-Schaltungen und -Systemen heute kein unlösbares Problem mehr darstellt.

Das SAMS Projekt ist nach drei Jahren Laufzeit zum 31.10.2006 erfolgreich abgeschlossen worden. Dieser Bericht gibt einen Überblick über die in der Projektlaufzeit erreichten Ergebnisse.

Abbildung 1.18 Überblick des Syntheseprozesses für analoge Schaltungen

## Architektur-, Schaltungssynthese und synthesege- rechte Modellierung in SAMS

Ausgangspunkt der Synthese in SAMS ist eine ausführbare Spezifikation einer zu synthetisierenden Applikation. Diese kann sowohl analoge als auch digitale Teile enthalten. Aufgabe der Architekturesynthese ist es, die ausführbare Spezifikation auf eine möglichst optimale Architektur elementarer Grundschaltungen abzubilden und die Komponenten der Architektur mit Constraints zu versehen, die in der Schaltungssynthese zur Auswahl der besten Schaltungsstruktur benötigt werden. Ein Schwerpunkt wurde auf die Automatisierung der Modellerstellung und die Mixed-Level-Simulation gelegt. Die Teilaufgaben bei der Architekturesynthese werden dabei interaktiv in zwei Teilschritten durchgeführt: Im ersten Schritt wird die Architektur auf Blockebene verfeinert. Im zweiten Schritt werden analog zu realisierende Blöcke weiter zerlegt, bis analoge Teilschaltungen entstehen, die dann Ausgangspunkt für die Schaltungssynthese sind.

Die Aufgabe der Schaltungssynthese in SAMS ist die Erzeugung von nominal-dimensionierten, bewerteten Schaltungsstrukturen für von der Architekturesynthese vorgegebene Spezifikationen. Schnittstelle sind VHDL-AMS-Beschreibungen, die überwiegend in generi-

schen Variablen beschriebene Spezifikationsgrößen übergeben. Im Projekt wurden die Methodik und die Algorithmen an den Schaltungsklassen Operationsverstärker, Komparator, Endstufe und zum Teil am Mischer erforscht.

Beim Entwurf analoger Schaltungen spielen viele Nebeneffekte und Nichtidealitäten eine Rolle, da sie zum Teil erheblich die Funktion bestimmen. Deshalb ist gerade hier der Vergleich des Entwurfsergebnisses mit der Spezifikation von großer Bedeutung. Während für kleinere Schaltungen direkt anhand der Transistorimulation das Schaltungsverhalten überprüft werden kann, ist für größere Schaltungen und komplexe Systemzusammenhänge eine Erzeugung von hinreichend genauen Verhaltensmodellen erforderlich. Dadurch lassen sich auch Eigenschaften auf der Systemebene prüfen, deren Simulation auf der Transistorebene kaum möglich ist (z.B. Bitfehlerraten).

Im Folgenden werden die einzelnen Komponenten des Entwurfsprozesses für analoge Schaltungen erläutert.

### **Analyse von Architekturvarianten**

Zu Beginn der Synthese müssen unterschiedliche Architekturvarianten evaluiert und verglichen werden. Dies umfasst die Aufgaben der Systempartitionierung, die Auswahl einer optimierten Struktur auf Blockdiagrammebene und die Spezifikation von Genauigkeiten einzelner Blöcke. Der Schaltungsentwickler wird bei dem interaktiven Prozess der Evaluierung von Architekturvarianten durch den Einsatz von „polymorphen Signalen“ unterstützt. Mit Hilfe von polymorphen Signalen kann ein Designer verschiedene Modellierungsformen (z.B. Bitvektoren, Signalfluss, el. Netz) und Simulatoren (SystemC-AMS, Matlab/Simulink, Dolphin/Smash mit SPICE und VHDL-AMS) miteinander verbinden. Eventuell notwendige Anpassungen (Bitbreiten, Abtastraten, physikalische Größen etc.) werden automatisch mit Hilfe einer polymorphen Darstellung der Schnittstellen zwischen den Blöcken konvertiert.

### **Verfeinerung von Architekturmodulen zu synthetisierbaren Schaltungen**

Architekturvarianten, die auf Blockebene vorliegen, werden im weiteren Entwurfsablauf so verfeinert, dass die resultierenden Teilblöcke von der anschließend durchzuführenden Schaltungssynthese in ein Netzwerk von elektrischen Komponenten abgebildet werden können. Die Verfeinerung der Architekturblöcke, die in Form von Verhaltensmodellen vorliegen, erfolgt mittels einer wiederholten Refaktorierung der Modellcodes. Dabei sind sowohl die Schnittstellenbeschreibung als auch der funktionale Inhalt eines jeden Blockmodells zu behandeln. An dieser Stelle erfolgt der Übergang von SystemC-AMS-Modellnotationen zu VHDL-AMS-Beschreibungsformen.

Zunächst erfolgt eine Abbildung der abstrakten, nicht-konservativen Schnittstellensignale auf konservative,

d.h. auf elektrische Größen in Kirchhoff-Netzwerken. Der zweite Schritt bei der Verfeinerung der Architekturbeschreibung behandelt die Transformation des funktionalen Inhalts eines Blockmodells unter Berücksichtigung von zusätzlichen Vorgaben, die jeder Funktionsblock erfüllen muss. Es erfolgt eine Architekturverfeinerung mittels Code-Refactoring von analogen Teilblöcken, die wiederum in Form von Verhaltensmodellen in VHDL-AMS vorliegen. Die Architekturbeschreibungen werden dabei mittels Modellcodetransformation soweit verkleinert, dass die resultierenden Einheiten von der Struktursynthese verarbeitet werden können.

### **Analyse und Verfeinerung von Architekturvarianten**

Grundstrukturen wie Differenzpaar, Stromspiegel usw. werden genutzt, um neue Schaltungsvarianten in VHDL-AMS zu erstellen. Diese Basisbausteine werden durch einen signalflussorientierten Algorithmus zu allen möglichen Topologien unter Berücksichtigung von Schaltungsvorgaben zusammengesetzt und bewertet. Die Constraints sind unter anderem Größe der Schaltung, Biasing, Symmetrie, Signaltyp (Strom/Spannung), Impedanzen. Der dem Entwickler in der Regel bekannte Struktur-Designraum, in unseren Beispielen zwischen 4.000 und 40.000 Schaltungen groß, wird durch dieses Verfahren vollständig automatisch exploriert. Die entstandenen Topologien werden nach einer ersten Überprüfung auf Eignung durch symbolische Verfahren schließlich einer vollautomatischen Dimensionierung und Bewertung zugeführt.

### **Symbolische Bewertung**

Der erste Schritt der Bewertung aller entstandener Topologien ist eine Bewertung mit der symbolischen Analyse, die vor allem für eine gegebene Schaltung die linearen Eigenschaften wie Verstärkung, Bandbreite usw. sehr schnell ermitteln kann. Durch eine gut eingestellte symbolische Analyse können 80 % - 90 % der ursprünglichen, undimensionierten Topologien aussortiert werden.

### **Schnelle Bewertung von Strukturvarianten analoger Schaltungen**

Bei der Synthese einer analogen Schaltung bzw. einer analogen Komponente eines Systems kommt zwischen der Synthese der Schaltungsstruktur auf Transistorebene und der Synthese des Layouts für die Fertigung ein Entwurfsschritt hinzu: die Dimensionierung von einstellbaren Parametern wie z.B. CMOS-Transistorweiten. Bei der Synthese einer Schaltungsstruktur müssen üblicherweise sehr viele, manchmal Tausende von Strukturvarianten verglichen werden, bevor eine geeignete Schaltungsstruktur gefunden ist. Eine ausführliche Dimensionierung ist extrem simulationsintensiv und zeitaufwändig und kommt daher für die Struktursynthese nicht in Frage. Die Leistungsfähigkeit einer Schaltungsstruktur wird durch die Menge der Eigenschaftswerte beschrieben, die sich durch gültige, d.h. technisch sinnvolle Dimensionierungen einstellen lassen. Diese Menge wird

**Abbildung 1.19:** Während der drei Jahre Projektaufzeit gab es mehrere Treffen und viele Kontakte zwischen den Industrie- und Forschungspartnern.

realisierbarer Eigenschaftsraum genannt. Es wurde eine neue simulationsbasierte Methode erforscht, die dank eines linearen Ansatzes eine hohe Anzahl von Eigenschaften gleichzeitig behandeln kann. Als Resultat ergibt sich eine formale Approximation und Visualisierung des realisierbaren Eigenschaftsraums in Form eines Polytops. Auf diese Weise wird erst ermöglicht, eine sehr große Zahl von Strukturvarianten zu betrachten und so zu Varianten zu gelangen, die aus Aufwandsgründen nicht verglichen und ausgewählt worden wären.

### Modellierung

Im Rahmen des Projekts wurden verschiedene Methoden der Verhaltensmodellierung untersucht und eingesetzt. Dabei spielte für die Integration in den gesamten Designflow ihre Automatisierbarkeit eine wichtige Rolle. Symbolische Verfahren lassen sich zur weitgehend automatischen Modellgenerierung einsetzen. Die Möglichkeit, gezielt Designparameter im Modell zu belassen, ist besonders von Vorteil. Die Erzeugung numerischer Modelle (auch Tabellenmodelle genannt) ist ebenfalls gut automatisierbar. Allerdings sind diese Modelle schlecht parametrisierbar und für komplexe, mehrdimensionale Zusammenhänge ebenfalls sehr zeitaufwändig in der Abarbeitung. Verhaltensmodelle auf Basis vorgefertigter Templates für bestimmte wiederkehrende Schaltungsklassen erwiesen sich als sehr flexibel und effizient. Nach dem einmaligen Aufwand zur Erstellung eines Templates kann die Parametrierung mithilfe einer Charakterisierungsumgebung automatisch erfolgen. Ein modularer Modellaufbau ermöglicht die gezielte Anpassung an die geforderte Genauigkeit.

### Nutzung von Industriebeispielen und Ausblick

Für den Test der entwickelten Methoden und deren Vorstellung standen dem Projekt zwei industrielle Beispiele aus dem Industriekonsortium zur Verfügung, die erfolgreich zur Validierung der Verfahren eingesetzt wurden. Neben der Validierung der einzelnen Methoden durch SW-Prototypen wurden auch der Entwurfsprozess und damit das Zusammenwirken der Schnittstellen zwischen den Werkzeugen gezeigt.

Der skizzierte Designflow des SAMS-Projekts und die erfolgreiche Anwendung an komplexen Industriebeispielen machen deutlich, dass die Synthese auch komplexer Mixed-Signal-Systeme methodisch beherrschbar ist. Jedoch lassen sich nicht alle Teilschritte sinnvoll in sehr hohem Maße automatisieren. Insbesondere bei der Architektursynthese hat sich gezeigt, dass bereits die Unterstützung des Designers beim interaktiven Schaltungsentwurf und bei der Modellerstellung und -verfeinerung die Arbeitsproduktivität deutlich steigert. Ein hoher Automatisierungsgrad ist jedoch hier in naher Zukunft noch nicht absehbar. Die Schaltungssynthese dagegen lässt sich mit den im SAMS-Projekt erforschten Methoden weitgehend automatisieren und liefert gute Ergebnisse, die jedoch stark von den zu wählenden Constraints abhängig sind. Die SAMS-Ergebnisse bezüglich einer durchgängigen Synthese zeigen, dass eine kommerzielle Umsetzung der Entwurfsautomatisierung bereits in vielen Entwurfsschritten denkbar ist. Hier werden die nächsten Jahre zeigen, ob die erzielten Erfolge beispielgebend sind und damit die Produktivitätslücke zwischen der analogen und der digitalen Welt verringert werden kann.

Eine Liste der Publikationen des Clusterforschungsprojekts SAMS befindet sich im edaAtlas ([www.edacentrum.de/edaatlas](http://www.edacentrum.de/edaatlas)) in der Rubrik „Projekt“ unter dem Stichwort „SAMS“. Hier finden sich auch Informationen zu Software-Prototypen. Im Tagungsband des edaWorkshop07 in Hannover wird ein detaillierter Artikel zum Clusterforschungsprojekt SAMS erscheinen.

**Kontakt (SAMS):**

Dr. Volker Schöber

fon: (05 11) 7 62-1 96 88

schoeber@edacentrum.de

# Nachrichten von den Projekten

[www.edacentrum.de/projekte](http://www.edacentrum.de/projekte)

**Trotz der vergleichsweise kurzen Zeitspanne seit dem Erscheinen des letzten newsletter edacentrum gibt es schon wieder Neuigkeiten von den Ekompass-Verbundprojekten. So weisen PRODUKTIV+ und auch VISION deutliche Erfolge bei der Veröffentlichung von Ergebnissen vor. VeronA erfreut die interessierte Öffentlichkeit mit der Organisation eines öffentlichen Tutorials und SIDRA kommt zum Projektende nochmal so richtig in Fahrt ...**

Aktuelle Informationen zu der Veranstaltung finden Sie unter

[www.edacentrum.de/veranstaltungen/](http://www.edacentrum.de/veranstaltungen/)

## Fach- und Kooperationsworkshop „Technologie und deren Auswirkung“

Am 11. Mai 2007 findet in Dresden ein vom edacentrum in Zusammenarbeit mit den Projekten: AIS, DETAILS, LEMOS, SIDRA, Sigma65 und URANOS organisierter Fach- & Kooperationsworkshop zum Thema „Technologie und deren Auswirkung“ statt. Die Veranstaltung schließt an den am 10. Mai ebenfalls in Dresden durchgeführten „IC-Design-Workshop“ an (siehe Seite 34), der vom IC Arbeitskreis des Silicon Saxony e.V. zum Thema „Entwurf von integrierten Analog-/Mixed-Signal-/HF-Schaltungen“ organisiert wird. Das genaue Programm des Fach- und Kooperationsworkshops stand bei Redaktionsschluss noch nicht fest – aber es wird darum gehen, wie EDA- und Technologieexperten voneinander lernen und ihre jeweiligen Probleme nicht nur besser verstehen, sondern auch lösen können. Themen werden u.a. die Evolution der Fertigungsprozesse und deren Auswirkungen auf den Schaltungsentwurf sowie Einflüsse der fortschreitenden CMOS-Skalierung auf den heutigen Schaltungs- und Systementwurf sein. Zudem werden die Ergebnisse aus der Veranstaltung der Silicon Saxony e.V. in den Fach- & Kooperationsworkshop mit einfließen. (CH)

**Termin:**

11. Mai 2007

9:00-17:00 Uhr

**Ort:** FhG-Dresden

**Kont@kt:**

Dr. Cordula Hansen

fon: (07 11) 28 07-9 56

hansen@edacentrum.de

## Veröffentlichungspflicht der Ekompass-Projekte im Rahmen der Projekt-Nebenbestimmungen