# newsletter edacentrum 02 2006

10,- Euro ISSN 1862 2283

electronic design automation centrum

[www.edacentrum.de/newsletter](http://www.edacentrum.de/newsletter)

## Projektspiegel

LEONIDAS+: Leitbahnorientiertes Design

**Erste Diskussionsrunde um die Forschungsthemen der Zukunft erfolgreich**

Das Forschungsthemenpapier eDesign 2006 geht in die nächste Runde

**Fachkonferenzen und Auftritte des edacentrum im ersten Halbjahr 2006**

Rückblick auf DATE, Ekompass-Workshop, CeBIT und ISCAS

# Editorial

Liebe Leserinnen und Leser,

es ist passiert. Die Fußballweltmeisterschaft hat es auf die Seite eins geschafft. Aber seien Sie beruhigt, dieses Heft wird davon nicht beherrscht! Für die EDA-Gemeinde wird dieses Thema sicher privat eine Rolle spielen. Darüber hinaus ist die Fußball-WM natürlich auch über die Stimulation von Technologie (Chip im Ball) wichtig. In jedem Fall, jetzt ist es „die Zeit“, in der „sich was dreht“.

Auch für den newsletter edacentrum hat sich einiges gedreht. Er hat es zum öffentlichen Periodikum mit einer ISSN gebracht! Und zum ersten Mal hat die Redaktion die Beiträge auswählen können, denn mehr als 52 Seiten wollten wir den Postboten dann doch nicht zumuten. An dieser Stelle danken wir allen, die zu diesem Heft beigetragen haben, insbesondere den freien Autoren Grabinski und Grimm. Wenn Sie, liebe Leserinnen und Leser, auch etwas aus EDA-Forschung und Entwicklung zu berichten haben, dann denken Sie an uns!

\*\*: „Teamgeist“ heißt der offizielle Fußball der FIFA-WM.

\* Wenn Ihnen diese Worte bekannt vorkommen, dann lesen Sie „Die Zeit“ in deren Ausgabe 20 ein auch für Nicht-Fußballfans sehr lesenswerter Artikel rund um DAS Ereignis dieser Tage zu finden war. ([www.zeit.de/2006/20/WM\\_Essay](http://www.zeit.de/2006/20/WM_Essay)).

Und sonst? Es gilt noch immer: „Die Welt zu Gast bei Freunden“, wo sogar der „Teamgeist“ \*\* mit Füßen getreten werden darf. Wie auch immer die Gruppenphase ausgehen wird, der Rummel um Tickets, Teams und Tore wird bleiben, egal ob Foxtrott oder „Samba auf Bismarckstraßen und Von-Moltke-Plätzen“\* getanzt wird. Aber wenn schon! – Spiel verderben gilt nicht, sondern nur der olympische Gedanke. Wie auch immer Sie zum Fußball stehen, machen Sie mit, wer weiß, wann wir so etwas wieder hier im Land erleben dürfen.

Wir wünschen Ihnen viel Freude an der WM und – beim Lesen!

Ralf Popp für das edacentrum

## Geschehenes:

### Abbildung 0.1:

Die Bildungsministerin zu Besuch auf dem CeBIT Stand (S. 33)

### Abbildung 0.2:

Die DATE06 in München (S. 27)

### Abbildung 0.3:

Der Ekompas-Workshop 2006 in Hannover (S. 18)

### Abbildung 0.4:

Ergänzende und ausführliche Informationen finden Sie im Internet unter [www.edacentrum.de/newsletter/](http://www.edacentrum.de/newsletter/)

Abbildung 0.1

Abbildung 0.2

# Inhaltsverzeichnis

## 1 Projektspiegel

|                               |    |

|-------------------------------|----|

| Projektbericht LEONIDAS+      | 04 |

| On-Chip Verbindungsstrukturen | 10 |

| Nachrichten von den Projekten | 13 |

| Aus der EDA-Clusterforschung  | 16 |

## 2 Neues aus dem edacentrum

|           |    |

|-----------|----|

| Meldungen | 14 |

|-----------|----|

### Ekompas-Workshop 2006

|           |    |

|-----------|----|

| Rückblick | 18 |

|-----------|----|

### DATE 06 – Eine Rückschau

|                                 |    |

|---------------------------------|----|

| Ausschnitt aus dem Trendbericht | 27 |

|---------------------------------|----|

### ISCAS 2006

|                 |    |

|-----------------|----|

| Ein Kurzbericht | 30 |

|-----------------|----|

### 18. ITG/GI/IMM Test-Workshop

|                             |    |

|-----------------------------|----|

| Bericht aus dem Schwarzwald | 31 |

|-----------------------------|----|

### 43th DAC 2006

|         |    |

|---------|----|

| Preview | 32 |

|---------|----|

### CeBIT 2006

|                                    |    |

|------------------------------------|----|

| Bundesministerin trifft edacentrum | 33 |

|------------------------------------|----|

### Projektmanagement

|                         |    |

|-------------------------|----|

| Neues von Alex und Bill | 34 |

|-------------------------|----|

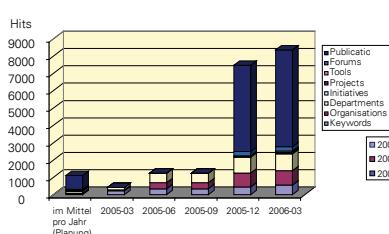

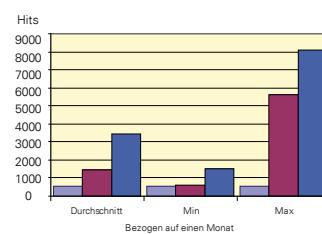

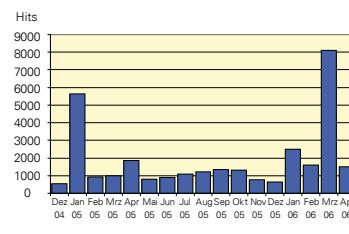

### edaAtlas

|                            |    |

|----------------------------|----|

| was war, was ist, was wird | 37 |

|----------------------------|----|

## 3 Panorama

|                             |    |

|-----------------------------|----|

| Meldungen der Online-Medien | 38 |

|-----------------------------|----|

|                           |    |

|---------------------------|----|

| Meldungen aus dem Ausland | 39 |

|---------------------------|----|

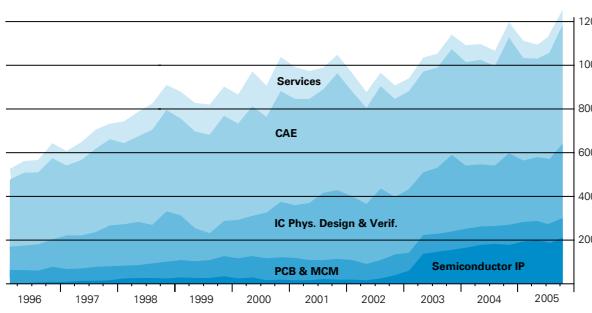

## 4 Marktbeobachtung

|                 |    |

|-----------------|----|

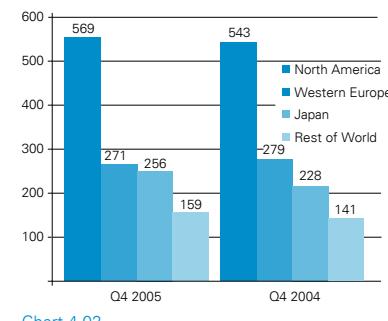

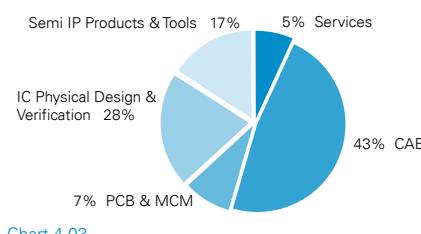

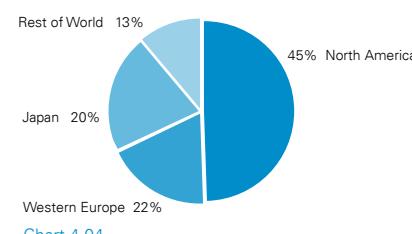

| 4. Quartal 2005 | 41 |

|-----------------|----|

## 5 Mitglieder

|                 |    |

|-----------------|----|

| Buchankündigung | 43 |

|-----------------|----|

|                         |    |

|-------------------------|----|

| Fraunhofer Gesellschaft | 44 |

|-------------------------|----|

|                                 |    |

|---------------------------------|----|

| Nachrichten von den Mitgliedern | 45 |

|---------------------------------|----|

|                                |    |

|--------------------------------|----|

| Firmenmitglieder im edacentrum | 47 |

|--------------------------------|----|

### Impressum

|                            |    |

|----------------------------|----|

| Mitarbeiter des edacentrum | 52 |

|----------------------------|----|

## Einhefter (perforiert und zum Rausnehmen)

|                                        |

|----------------------------------------|

| Auszug aus dem edaKalender 2006 / 2007 |

|----------------------------------------|

|                                    |

|------------------------------------|

| A4 Wand-Jahreskalender 2006 / 2007 |

|------------------------------------|

|                     |

|---------------------|

| Fußball-Bastelbogen |

|---------------------|

|                              |

|------------------------------|

| Einladung zum CLEAN Workshop |

|------------------------------|

## In den Ausgaben der Mitglieder

|                                        |

|----------------------------------------|

| Mitgliederverzeichnis zum Herausnehmen |

|----------------------------------------|

|             |

|-------------|

| Anschriften |

|-------------|

Abbildung 0.3

Abbildung 0.4

# 1 Projektspiegel

## Der Ekompass-Förderkomplex

[www.edacentrum.de/ekompass/](http://www.edacentrum.de/ekompass/)

Die zur Zeit vom edacentrum betreuten Projekte gehören zu dem vom Bundesministerium für Bildung und Forschung (BMBF) zur Stimulation von EDA-Forschungsaktivitäten eingerichteten Förderkomplex namens Ekompass. Ekompass steht für „Entwurfsplattformen für komplexe angewandte Systeme und Schaltungen der Mikroelektronik“.

Mit diesem Förderkomplex will das BMBF in erster Linie dazu beitragen, die einer starken internationalen Konkurrenz ausgesetzten Arbeitsplätze in der Systemindustrie und im EDA-Umfeld zu erhalten und auszubauen. Ziel ist es, durch ein gemeinsames Vorgehen von Industrie, Forschung und öffentlicher Hand, in den für Deutschland (und für Europa) wichtigen Bereichen neue Entwurfsmethoden zu entwickeln, um die Komplexität zukünftiger Chipsysteme qualitätsgerecht und

effektiv beherrschen zu können. Dabei wird der Fokus auf solche Themen gelegt, denen für die Wettbewerbsfähigkeit der deutschen Industrie die größte Bedeutung zukommt.

Der Förderkomplex Ekompass ist allerdings nicht nur von nationaler Bedeutung. Die meisten Forschungsvorhaben haben ein internationales Umfeld, insbesondere auf europäischer Ebene, wo Synergien aus gemeinsamen Stärken entstehen. Die für Ekompass sehr wichtige europäische Zusammenarbeit wird auch dadurch transparent, dass einige der Ekompass-Projekte in MEDEA+ Projekte eingebettet sind.

Der Newsletter des edacentrum berichtet in loser Folge über die Projekte des Ekompass-Förderkomplexes.

| Projekt    | FKZ     | Laufzeit           | Projektkoordinator/in                                     |

|------------|---------|--------------------|-----------------------------------------------------------|

| DETAILS    | 01M3071 | 1.4.04 - 31.3.07   | Reimund Wittmann, reimund.wittmann@nokia.com              |

| FEST       | 01M3072 | 1.7.04 - 30.6.07   | Dr. Volker Schöber, schoeber@edacentrum.de                |

| LEMOS      | 01M3155 | 1.11.03 - 31.10.06 | Ralf Pferdmenges, ralf.pferdmenges@infineon.com           |

| LEONIDAS+  | 01M3074 | 1.3.05 - 28.2.07   | Irmtraud Rügen-Herzig, irmtraud.rügen-herzig@infineon.com |

| PRODUKTIV+ | 01M3077 | 1.10.05 - 30.9.08  | Dr. Jürgen Alt, juergen.alt@infineon.com                  |

| SAMS       | 01M3070 | 1.11.03 - 31.10.06 | Dr. Volker Schöber, schoeber@edacentrum.de                |

| SIDRA      | 01M3159 | 1.8.04 - 31.7.06   | Dr. Petra Rose, perta.rose@de.bosch.com                   |

| URANOS     | 01M3075 | 1.7.05 - 30.6.08   | Dr. Hans-Jürgen Brand, hans-juergen.brand@amd.com         |

Abbildung 1.01

**Abbildung 1.01:**

Übersicht über die aktuellen Ekompass-Projekte.

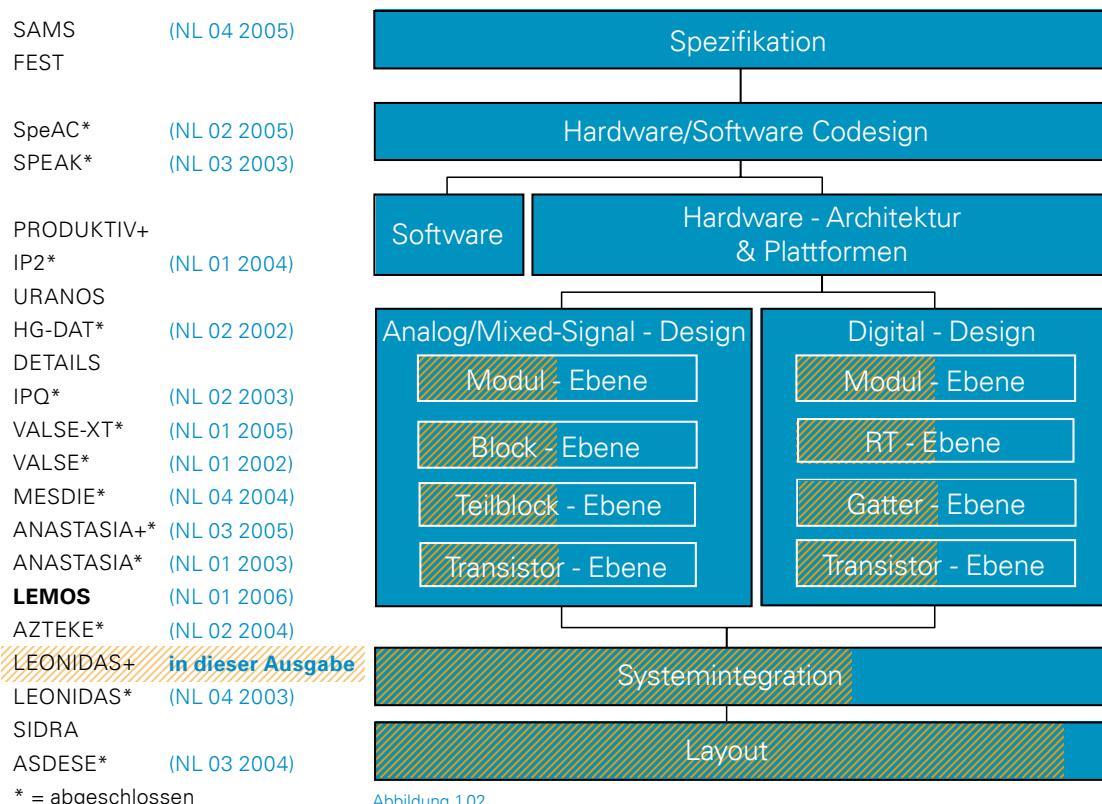

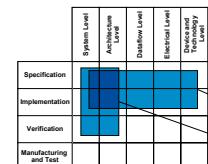

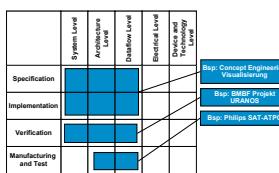

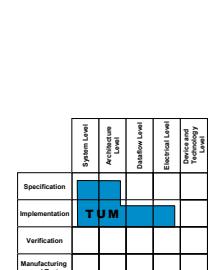

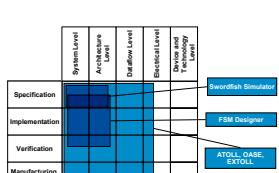

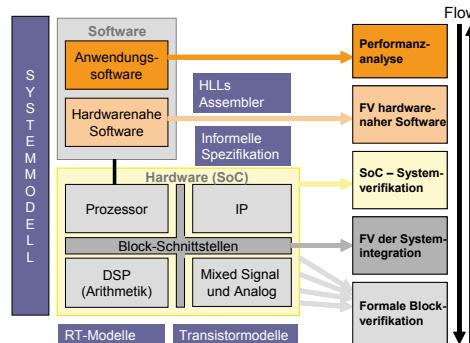

**Abbildung 1.02:**

Das Bild zeigt verschiedene Entwurfsvorgänge des Schaltungsentwurfs. Dabei sind die Schwerpunkte des Projektes LEONIDAS+ hervorgehoben, weil sich das Projekt LEONIDAS+ in dieser Ausgabe des Newsletters präsentiert.

Abbildung 1.02

\* = abgeschlossen

# LEONIDAS+: Leitbahnorientiertes Design

[www.edacentrum.de/projekte](http://www.edacentrum.de/projekte)

Dieser Projektbericht von Markus Olbrich entstand gestützt auf die Mitarbeit von Patrick Birrer, Martin Frerichs, Manfred Henning, Harald Kinzelbach, Klaus Koch, Jürgen Köhne, Eduard Konradi, Irmtraud Rugen-Herzig, Jürgen Schäffel, Thomas Jambor, Göran Jerke und Patrick Wernicke

**Förderkennzeichen:**

01 M 3074

**Laufzeit des Vorhabens:**

01.03.2005 - 28.02.2007

**Zusammensetzung**

des Projektkonsortiums

**Partner:**

Atmel Germany GmbH <

Cadence Design Systems

GmbH <

Infineon Technologies AG <

Philips Semiconductors GmbH <

Robert Bosch GmbH <

Universität Hannover - Institut

für Mikroelektronische Systeme

(IMS) <

**Unterauftragnehmer:**

Redemund & Thiede

Datentechnik GmbH <

TU Darmstadt - Fachgebiet

Mikroelektronische Systeme <

Qimonda AG (Unterauftrag in

Vorbereitung) <

TU Dresden - IFTE <

Universität Siegen - IMT <

Universität Ulm - AEM <

Die Entwicklung von nanoelektronischen Systemen führt zu neuen Herausforderungen: Noch vor ein paar Jahren konnten parasitäre Eigenschaften von Leitungen vernachlässigt werden, weil die Schaltzeiten von Transistoren überwogen. Heute hingegen dominieren die Leitungseigenschaften die Verzögerungszeit einer Schaltung. Dies gilt sowohl im ASIC- als auch RAM-Bereich. Im Automotive-Bereich erzwingen die gestiegenen Anforderungen an die Zuverlässigkeit der Steuerungselektronik einen verifizierbaren robusten Entwurf der Verbindungsleitungen. In der Mobilkommunikation stellen HF-Schaltungen in integrierten Mixed-Signal-Systemen erhöhte Anforderungen an die Eigenschaften der Verbindungsleitungen.

In den genannten Bereichen fehlt es zurzeit an vielen Stellen an geeigneten Entwurfssystemen und Entwurfsmethoden. Das kann so weit führen, dass nach bestehenden Regeln korrekt entworfene Schaltungen nicht funktionsfähig sind. So werden Re-Designs nötig, die erhebliche Kosten verursachen und das Erreichen der angestrebten technischen Ziele erschweren. Diese Problematik wird sich in Zukunft weiter verschärfen, so dass die Kompetenz zur Beherrschung der Leitbahneigenschaften eine Schlüsselkomponente beim Entwurf ist.

Allgemeine Lösungen „von der Stange“, wie sie von vielen amerikanischen EDA-Firmen zum Teil entwickelt werden, sind allein keine Lösung für eine leitbahnzentrierte Entwurfsmethodik. Da sich die Anwendungsschwerpunkte in Deutschland von den US-amerikanischen unterscheiden, müssen für deutsche Anwendungen spezifische Tools und Methoden entwickelt werden. Das Konsortium von LEONIDAS+ greift die Herausforderungen auf, die die Verbindungsleitungen stellen.

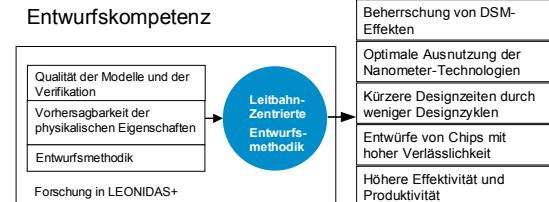

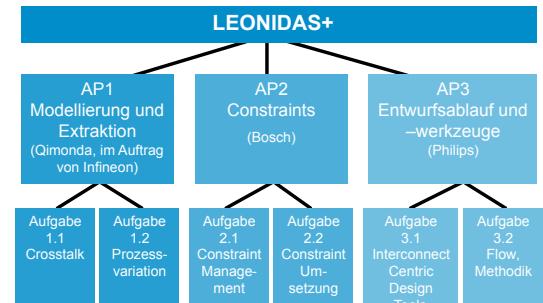

**Abbildung 1.03:**

Projektziele von LEONIDAS+

**Abbildung 1.04:**

Übersicht der Projektstruktur

von LEONIDAS+

**Ziele**

Ziel des Projekts LEONIDAS+ ist es, einen leitbahnzentrierten Entwurf zu ermöglichen. Der große Umfang dieser Problematik erforderte eine Schwerpunktbildung im Projekt. LEONIDAS+ liefert Basisarbeiten, die für andere Ekompass-Projekte eine wichtige Grundlage darstellen. Abbildung 1.03 zeigt die Projektziele im Überblick.

Es werden Forschungsarbeiten durchgeführt, um neue Lösungen für die Extraktion, die Analyse und Modellierung der Leitbahneigenschaften zu finden. Die Vorhersagbarkeit der physikalischen Eigenschaften eines Entwurfs wird damit bereits in einem sehr frühen

**Entwurfskompetenz**

Abbildung 1.03

Stadium mit hoher Genauigkeit gewährleistet werden. Bisher sequentielle Entwurfsschritte sollen mit neuartigen Algorithmen simultan ablaufen, so dass ein fehlerfreier Erstentwurf ermöglicht wird. Durch diese Maßnahmen wird die Qualität der Verifikation und des Entwurfs wesentlich verbessert, es entstehen weniger Zyklen im Designflow und die Anzahl der Re-Designs wird reduziert.

**Projektstruktur**

Das Projekt ist in 3 Arbeitspakete und diese sind in jeweils zwei Aufgaben gegliedert. Die Aufgaben werden in verschiedenen Beiträgen einzelner Partner in thematisch enger Kooperation bearbeitet. Die Projektstruktur zeigt Abbildung 1.04:

Abbildung 1.04

Anhand einiger ausgewählter Arbeitsfelder werden im Folgenden einige Themen und bisherige Ergebnisse vorgestellt.

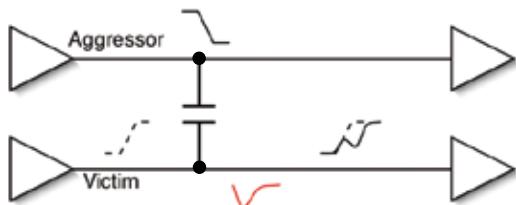

**Crosstalk**

Eines der größten Probleme in der Timingverifikation moderner Chips liegt in der Vorhersage des möglichen Crosstalks, d.h. der unbeabsichtigten kapazitiven oder induktiven Interaktion von benachbarten Leitungen. Diese wird verursacht durch die starke Kopplungen zwischen Leitungen. Problematisch ist, dass heutige Algorithmen sehr pessimistische Ansätze bei der Abschätzung von Crosstalk verwenden. Crosstalk gefährdet die Funktion von Schaltungen, da die Signallaufzeit bei gleichzeitigem Schalten von Signalen verkürzt (Gleichtaktschalten) oder verlängert (Gegentaktschalten) werden kann. Die Folge ist ein fehler-

haftes Zeitverhalten (timing). Die Beeinflussung der Leitungen (s. Abbildung 1.05) untereinander kann zu fehlerhaften Logikzuständen führen, so dass die korrekte Funktion des Systems nicht mehr gewährleistet ist.

Abbildung 1.05: Aggressor / Victim Line

In zukünftigen Technologien werden Leitungsabstände weiter abnehmen und Leitungshöhen zunehmen. Dadurch werden die Möglichkeiten zur Kopplung zwischen Leitungen erhöht. Weiter werden die digitalen Zellen mit abnehmenden Betriebsspannungen empfindlicher gegenüber Crosstalk. Der Pessimismus heutiger Algorithmen röhrt daher, dass diese immer den sogenannten Worst-Case annehmen. Dieser ist so festgelegt, dass alle Kopplungen koordiniert zum gleichen Zeitpunkt ihren maximalen Crosstalk einbringen — selbst wenn dies real gar nicht möglich ist. Diese Annahme röhrt daher, dass kein Crosstalk größer als im Worst-Case auftreten kann. Schon heute werden dabei aber zu viele Aggressoren in zu pessimistischer Weise berücksichtigt.

Alle tatsächlich möglichen Schaltkombinationen aller Aggressoren und Victims in angemessener Zeit zu erfassen und zu analysieren ist jedoch schon bei mehr als 20 Einkopplungen auf nur ein Netz nahezu unmöglich. Für Pfade mit mehreren Netzen in Reihe oder gar für alle Netze und Pfade in einem gesamten Chip ist dies mit derzeitigen Möglichkeiten nicht lösbar.

Diese sogenannte NP-Komplexität des Problems verhindert nicht nur eine akkurate Analyse auf dem relativ abstrakten Niveau der digitalen Timing-Analyse, sondern auch in der Analogsimulation. Bereits bei nur einem Aggressor gibt es zahlreiche Möglichkeiten, dass dessen Signal mit dem des gestörten Victims korreliert. Bei zwei und mehr Aggressoren steigt die Anzahl der Kombinationen exponentiell an. Deshalb gibt es bis heute keine automatisierten Verfahren, um Referenzsimulations für Crosstalk durchzuführen. Gerade dies ist aber nötig, um neue analytische Crosstalkmodelle zu entwickeln und die Ungenauigkeit in diesen Modellen zu verringern.

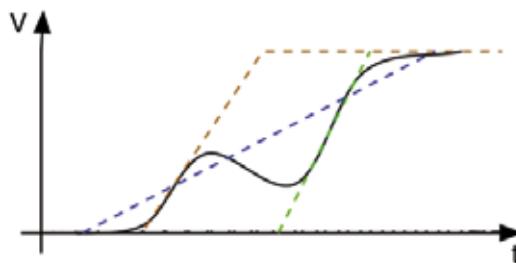

Hinzu kommt, dass heute Signale üblicherweise als lineare Rampe modelliert werden. Es ist aber nahezu unmöglich, analytisch eine äquivalente lineare Rampe für durch Crosstalk gestörte Signale herzuleiten (s. Abbildung 1.06). Neue, näher an der Physik orientierte Modelle, sind hier vonnöten. Da es sehr unwahrscheinlich ist, dass wirklich alle Aggressoren koordiniert zur gleichen Zeit auf ein Victim einwirken, sind stochas-

tische Modelle gefragt. Diese sollen zum einen dem Designer angeben, welche Netze mehr gefährdet sind als andere (also optimiert werden müssen) und wie groß die mittlere Ausfallzeit ist, bis zu der zum ersten Mal ein relevanter Crosstalk-Störungsfall auftritt.

Abbildung 1.06: gestörtes Signal

**Abbildung 1.05:**

Ein Aggressor stört einen Victim. Ein Bump (rot) ist die Folge oder das Victim-Signal wird gestört (gestrichelt vs. durchgezogene Linie).

**Abbildung 1.06:**

Ein gestörtes Signal (durchgezogene Linie) wird durch verschiedene lineare Rampen angenähert. Aber welche ist „richtig“?

In LEONIDAS+ entwickelt Infineon neue Methoden um Crosstalk zu erkennen, der keine Verzögerung bewirken kann. Wenngleich es hierfür schon prinzipielle Lösungen gibt, sind diese aufgrund der NP-Komplexität nicht breit einsetzbar. Analysen, durchgeführt im Rahmen von LEONIDAS+, zeigen, dass im Durchschnitt je nach Design 30 oder gar 50 Prozent der Aggressoren nicht „echt“ sind. Selbst wenn Crosstalk möglich ist, ist er nicht immer gleich wahrscheinlich. Um diese Wahrscheinlichkeiten, z.B. in Form von Mean Time Between Failure (MTBF)-Modellen vorherzusagen, werden neue stochastische Crosstalkmodelle entwickelt.

Um sicherzustellen, dass die entwickelten Modelle und Algorithmen auch mit der Wirklichkeit übereinstimmen, werden Test- und Messschaltkreise in Zusammenarbeit mit dem MES Darmstadt entwickelt. Die Testschaltungen werden so abgestimmt, dass sie mit großer Wahrscheinlichkeit Crosstalk in einem definierten Zeitraum und in einem definierten Stärkebereich erzeugen. Messschaltungen werden entwickelt, um eben diesen Crosstalk auszumessen. Dies geschieht einerseits indirekt, d.h. die Auswirkungen des Crosstalk (zusätzliches Delay oder falscher logischer Zustand) werden detektiert, andererseits direkt, indem die gestörten Signale oder Crosstalk Bumps hochgenau ausgemessen werden.

Durch die neuen Modelle und Methoden wird eine Reduzierung des Designaufwands um mehrere Wochen erwartet. Weiter wird es möglich, Schaltungen mit höheren Taktraten zu entwickeln. Die hochgenauen Messschaltungen werden es ermöglichen, die alten und neu entwickelten Modelle mit der Wirklichkeit abzugleichen.

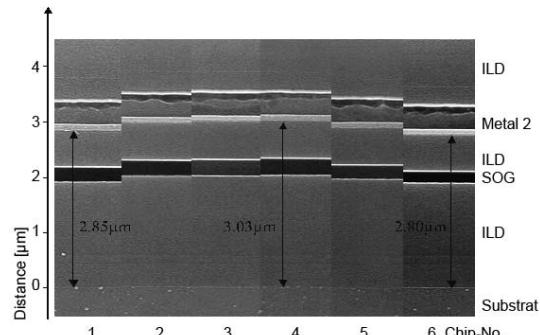

### Prozessvariationen

Mit immer kleineren Strukturgrößen und immer komplexeren Schaltungsentwürfen gewinnen die Auswirkungen unvermeidlicher, zufälliger Fertigungsschwankungen immer mehr an Bedeutung. Um die technologischen Vorteile der kommenden Technologien zu nutzen, wird es daher

in zunehmenden Maße wichtig, Methoden zur Verfügung zu haben, die es erlauben, Einfluss und Folgen solcher Prozessvariationen schon in einer möglichst frühen Entwurfsphase angemessen berücksichtigen zu können.

Aufgrund der Schwankungen im Herstellungsprozess variieren einerseits Größen wie die Oxid-Dicken, Gate-Längen, Dotierungskonzentrationen etc., die die Charakteristika der einzelnen Transistor-Bauelemente bestimmen. Aber auch die Dicken der Metall-Lagen und Isolator-Schichten und die Weiten und Abstände der Metallbahnen, die die einzelnen Bauelemente elektrisch verbinden, sind fertigungsbedingten Schwankungen unterworfen (s. Abbildung 1.07). Diese führen dazu, dass auch die parasitären Eigenschaften der Leitbahnen (also beispielsweise ihre Widerstände und Kapazitäten) zu variierenden Größen werden.

**Abbildung 1.07:**

Querschnitt durch Teststrukturen: Schwankungen der Metall- und Isolatordicken auf einem Wafer.

Abbildung 1.07: Querschnitt

Mit der steigenden Bedeutung der parasitären Leitbahneigenschaften auf das Gesamtverhalten der Schaltung zeigt sich verstärkt die Notwendigkeit, auch diese Variationen im Schaltungsentwurf zu berücksichtigen. Sie sind allerdings von etwas anderer Natur als die der Bauelemente selbst, da sie sehr kontext-abhängige Größen sind: Die Kapazitäten beispielsweise werden nicht nur von den lokalen technologischen Parametern bestimmt, sondern auch von der jeweiligen Netzwerkumgebung der betrachteten Bahn. Aufgrund dieses besonderen Charakters des Problems finden sich daher derzeit kaum geeignete Analysemethoden im Angebot der EDA-Industrie.

In LEONIDAS+ entwickelt Infineon neue Methoden um diese Lücke zu schließen. Aufbauend auf Resultaten der ersten LEONIDAS-Projektphase (04/2002-03/2004), in der der Einfluss solcher Schwankungen auf repräsentative zweidimensionale Leitbahnmuster untersucht wurde, entsteht hier ein neuartiger Variations-Extraktions-Flow zur Extraktion von Interconnect-Schwankungen aus einem gegebenen „realen“ Layout.

Das Verfahren kombiniert einen geeignet gewählten Satz von Standard-RC-Extraktionen mit einem in der ersten Projektphase entwickelten semi-analytischen Linearisierungsansatz. Dadurch wird eine erweiterte Form von Netzlisten erzeugt, die alle Informationen enthalten, die notwendig sind, den Einfluss der Inter-

connect-Variationen auf das Verhalten der betrachteten Schaltung anhand von Analog-Monte-Carlo-Simulationen zu ermitteln.

Gleichzeitig entstehen in zwei anderen Projektbeiträgen (IMS Hannover und Qimonda) neue Verfahren, die Wege eröffnen, solche Monte-Carlo-Simulationen effizienter durchzuführen zu können. Zur Beschleunigung der Simulation wird im IMS-Beitrag ein Verfahren entwickelt, das „Importance Sampling“ verwendet. Die Anwendung dieses Verfahrens auf eine zweidimensionale Busstruktur zeigt ein zweistelliges „Speedup“. Der Qimonda-Beitrag wird es ermöglichen, die kritischen Leitbahnpasiten, auf deren Schwankungen die Schaltung besonders empfindlich reagiert, schon vorab zu identifizieren und die unter Umständen recht aufwendige Analyse von vornherein auf diese einzuschränken.

### Constraint-Umsetzung im Analoglayout

Beim Entwurf von integrierten Schaltungen wird die Qualität des Entwurfsergebnisses maßgeblich dadurch bestimmt, inwieweit das Ergebnis die angestrebten Optimierungsziele erreicht und alle gegebenen Entwurfsrandbedingungen (Constraints) eingehalten werden. Die Vielzahl, Komplexität und Mannigfaltigkeit möglicher Constraints, insbesondere bei analogen Schaltungen, machen deren möglichst automatische Analyse, Verarbeitung und Verifikation zunehmend wichtiger.

Im Rahmen der ersten LEONIDAS-Projektphase wurde von den Projektpartnern Atmel, Bosch und Infineon die Constraintdarstellung als Constraint-Typen für EDA-Tools definiert und für die Verwaltung in einem Constraint-Management-System vorbereitet. Diese Constraint-Typen werden im Rahmen von LEONIDAS+ kritisch untersucht, aktualisiert, erweitert und geeignet strukturiert.

Zur Analyse und Verarbeitung von beliebigen abstrahierten Constraints wird ein sog. Constraint-Engineering-System (CES) entwickelt. Das CES dient dabei nicht der Verwaltung der Constraintdaten im Sinne eines Constraint-Management-Systems, sondern ausschließlich als Fundament für eine flexible Verifikation von nahezu beliebigen Constraints (Constraint-Verifikation) und zur Bestimmung des Entwurfslösungsraumes. Die Analyse des Lösungsraumes ermöglicht neuartige Ansätze für den automatisierbaren constraint-geführten Entwurf von analogen integrierten Schaltungen. Das CES ist in der Lage, explizit oder per Regel definierte Constraints aus einer oder mehreren externen Datenquellen, wie z.B. verschiedenen Constraint-Management-Systemen von EDA-Tools, zu berücksichtigen.

Zur Darstellung dieses Konzeptes wird derzeit ein CES-Demonstrator realisiert. Mit Hilfe der genannten Entwicklungen wird eine signifikante Steigerung der

Entwurfssicherheit bei minimierter Chipfläche und der Wiederverwendbarkeit von analogen integrierten Schaltungen erwartet.

### Dynamische IR-Drop-Analysemethode

Durch die moderne mobile Telekommunikationstechnik werden die Leistungsaufnahme und die für den Betrieb benötigten Versorgungsspannungen integrierter Bausteine immer weiter reduziert. Dies bedeutet neue technische Anforderungen bereits im Entwicklungsstadium des Halbleiterdesigns. Bei immer weiter sinkenden Versorgungsspannungen, die bei einer 90 nm Technologie mittlerweile im Bereich von 0,8 V liegen, werden die tolerablen Bereiche für derartige Pegelschwankungen immer kleiner und der Spannungsabfall kann zum unbeabsichtigten Schalten von Transistoren führen. Bei der Power-Versorgung kann ein unerwünschter, aber in realen Schaltkreisen nicht völlig vermeidbarer Spannungsabfall (im folgenden IR-drop genannt) auftreten. Der äquivalente Effekt auf der Ground-Versorgungsleitung zeigt sich als Spannungsspitze (Ground Bounce). Beim IR-drop muss man grundsätzlich zwischen zwei Arten unterscheiden. Da ist zum Einen der statische IR-drop, welcher im eingeschwungenen Zustand der Schaltung im Mittel über die Zeit eine Variation in der Versorgungsspannung bezeichnet. Zum Anderen gibt es den dynamischen IR-drop, welcher meist sehr lokal an bestimmten Schaltungspunkten auftritt und im Normalfall um ein Vielfaches höher ist als der statische Wert, dabei aber sehr oft nur kurzzeitig auftritt. Leider können diese kurzen aber sehr hohen Spannungsspitzen bereits zum logischen Fehlverhalten der Schaltung führen und müssen besonders beachtet werden. Ein Ziel des Schaltungsentwurfs ist die Vermeidung hoher auftretender IR-drop-Werte. Um dieses Ziel zu erreichen, sind verschiedene Ansätze denkbar, wie das Einbringen geeigneter kapazitiver Zellen, um Spannungsschwankungen abfangen zu können. Diese so bezeichneten Decap-Zellen werden als „Fillerzellen“ benutzt und können elektrisch zwischen die Versorgungsspannungen angeschlossen werden. Dadurch wird die Ladung aus dem Schaltkreis bei einer auftretenden Spannungsspitze aufgenommen, bzw. bei einem Spannungseinbruch vorher aufgenommene Ladung wieder an den Schaltkreis abgegeben, um so den dynamischen IR-drop zu minimieren. Aus diesem Grund ist es eine technisch und wirtschaftlich interessante Fragestellung, den IR-drop bei platzierten „Fillerzellen“ mit Hilfe einer Simulation zu bestimmen, um so die optimale Anzahl und ebenfalls die optimale Platzierung zu bestimmen. Ziel ist es, den dynamischen IR-drop soweit kontrollieren zu können, dass er als Ursache für den Ausfall der Chips ausscheidet, gleichzeitig aber die Ausbeute nicht wieder durch „Fillerzellen“-Durchschlag begrenzt wird.

Die Grundlage dieser Entwicklung und einer späteren Platzierungsmethodik ist ein den technischen Anforderungen entsprechendes dynamisches IR-drop Tool. Somit bestand die erste Aufgabe dieses Beitrags von

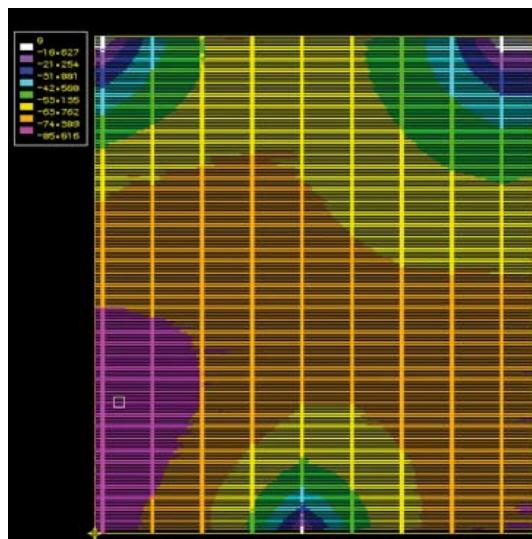

Infineon darin, anhand der benötigten Funktionalität eine geeignete Software auszuwählen. Basierend auf dieser Auswahl wurden zunächst Untersuchungen auf vorhandenen realen Schaltungen gestartet, um die Größe und Stärke des auftretenden lokalen dynamischen IR-drops feststellen zu können. Die Abbildung 1.08 zeigt den dynamischen IR-drop-Verlauf des Powernetzes und den Hot-Spot innerhalb einer Schaltung bei vorgegebener Einspeisung.

Abbildung 1.08: Hot-Spots

Anschließend wurden in einem kleinen Beispiel an dem Punkt mit maximalen IR-drop (hot spot) zusätzlich verschiedene hohe Kapazitätsbeläge in die Schaltung eingebracht, um die Wirkungsweise der Decap-Zellen zu belegen. Die Ergebnisse zeigen, dass durch gezieltes Einbringen eines zusätzlichen Kapazitätsterms der lokal auftretende hohe dynamische IR-drop reduziert werden kann. Weitere Untersuchungen werden zeigen, welche Decap-Zellgrößen praktisch eingesetzt werden können. Außerdem soll eine Methodik zur automatischen Platzierung entwickelt werden.

### Parasitensymmetrisches Routing

Insbesondere bei der Verdrahtung von empfindlichen differentiellen Leitungen analoger integrierter Schaltungen spielt die Verteilung der parasitären Effekte auf den jeweiligen Netzen auf Grund der steigenden Betriebsfrequenzen eine elementare Rolle.

Im Vordergrund steht dabei die parasitensymmetrische Verdrahtung, d.h. die gleichmäßige Verteilung der parasitären Widerstände, Kapazitäten und Induktivitäten innerhalb von Leitungsgruppen. Schaltungsmaßnahmen sorgen dafür, dass der absolute Wert der Leitungsparameter keine Bedeutung hat.

Im Rahmen von LEONIDAS+ werden Forschungsarbeiten an den Verdrahtern GARA und PARSY, die eine Berücksichtigung parasitärer Effekte bereits während der Verdrahtung ermöglichen, unter Einbeziehung hoher Frequenzbereiche weitergeführt.

Abbildung 1.08:

Dynamische IR-drop-Map des Powernetzes innerhalb einer Schaltung bei vorgegebener Einspeisung mit Hot-Spot.

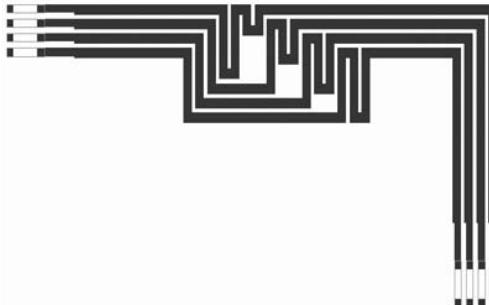

Die Symmetrie wird in PARSY durch gleichzeitige Verdrahtung mehrerer Netze unter Verwendung busähnlicher Leitungsstrukturen erzielt. Zusätzlich wird die Symmetrie bei der Wegesuche optimiert.

Abbildung 1.09 zeigt ein Beispiel mit vier Netzen. Die durch den notwendigen Richtungswechsel des Bündels entstehenden Längenunterschiede werden durch ein Ausgleichsmodul behoben, das überdies für eine identische Anzahl an Leitungsknicken in den einzelnen Leitungen sorgt. Die jeweiligen Leitungsstrukturen werden durch Modulgeneratoren erzeugt, um eine möglichst effiziente Verdrahtung zu gewährleisten.

**Abbildung 1.09:**

PARSY-Verdrahtungsbeispiel

**Abbildung 1.09:** Parsy

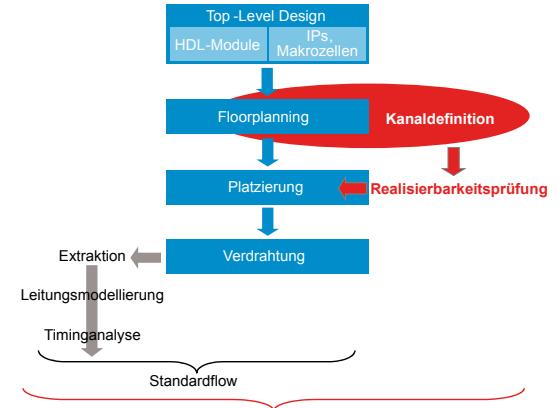

Leitungsbündel sowie dessen beidseitige Abschirmung realisiert. Die Verwendung einer definierten Leitungsstruktur ermöglicht eine parameterbasierte Modellierung des Leitungsverhaltens für parallel verdrahtete Leitungsstrukturen. Eine Anpassung des Modells an den jeweiligen Anwendungsfall geschieht durch eine Anpassung der Modellparameter. So kann bereits beim Floorplanning ein Verdrahtungskanal für die betrachteten Leitungen definiert werden und die Parameter der Leitungsführung können an das Modell übergeben werden. Für die Realisierbarkeitsprüfung werden Digitalsimulationen des Systems mit dem integrierten Simulationsmodell für parallel verdrahtete Leitungsstrukturen durchgeführt. Dieses Vorgehen ermöglicht eine erste Aussage über die Realisierbarkeit der Verdrahtung untersuchter Leitungen innerhalb des betrachteten Designs bereits während des Floorplannings. Eine frühzeitige Identifikation der möglichen Timing-Engpässe oder einer Verletzung der Timing-Anforderungen im Design trägt zusätzlich zur Entwurfssicherheit während der darauf folgenden Designsschritte bei und verspricht eine Reduktion der notwendigen Iterationsschritte und deren Umfang während des Schaltungsdesigns.

**Abbildung 1.10:** Designflow

Die Durchführung der Arbeiten zu diesem Thema findet in einer Zusammenarbeit zwischen Atmel Germany GmbH und der Universität Ulm statt. Zugrunde liegt ein in LEONIDAS entwickelter Ansatz zur Modifikation des Designflows für standardzellenbasierte Systeme. Die aktuellen Arbeiten konzentrieren sich auf die Implementierung der Modellierungsmethoden in ein Simulationsmodell unter Verwendung der Beschreibungssprache SystemC.

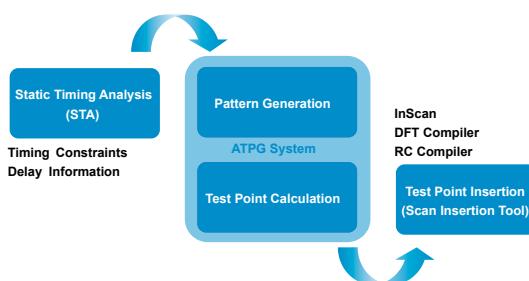

#### **Einfügen von spezifischen Testpunkten in DfT-Verdrahtungen unter Berücksichtigung des Timings**

Moderne Designs bestehen mehr und mehr aus vielen Clocksystemen. Bei solchen Designs mit vielen Schaltungszweigen mit unterschiedlichen Taktabfolgen kommt es häufig zu Skew-Problemen, das heißt zu einer Taktverschiebung auf Grund von Laufzeitunterschieden in den verschiedenen Leitungspfaden. Dies kann dazu führen, dass ein Signal zu „spät“ oder auch zu „früh“ an einem Flipflop in der Schaltung ankommt.

Daher kann dieses Flipflop das Signal nicht mehr - oder fälschlicherweise schon - speichern und es kommt unweigerlich zu einem Informationsverlust.

Daneben werden in DSM-Schaltungen zunehmend sogenannte Testpunkte in das Design eingefügt, die zur Regulierbarkeit und Beobachtbarkeit von Signalzuständen dienen. Durch TPI (Test-Point-Insertion) kann zudem die Anzahl der Testmuster deutlich verringert und gleichzeitig die Testabdeckung erhöht werden. Solche Testpunkte bestehen aus Bauelementen, die in den Verdrahtungspfad eingebaut werden. Dadurch ergeben sich aber wiederum zusätzliche Taktverzögerungen, die zu verstärkten Geschwindigkeitsproblemen führen können.

Ziel der Arbeiten von Philips ist eine constraint-getriebene Verdrahtungsoptimierung, die eine timing-getriebene Testpunktberechnung und Implementierung in die Netzliste unterstützt (s. Abbildung 1.11). Dadurch können mögliche Laufzeitprobleme insbesondere auf sehr langen Verdrahtungsleitungen vermieden werden. Die entsprechenden Constraints sollen von einem DfT-Insertion-Tool und einem STA (Static-Timing-Analysis) Werkzeug geliefert und automatisiert bei der Berechnung der Testpunkte berücksichtigt werden. Insbesondere werden unterschiedliche Clocksysteme zu berücksichtigen sein.

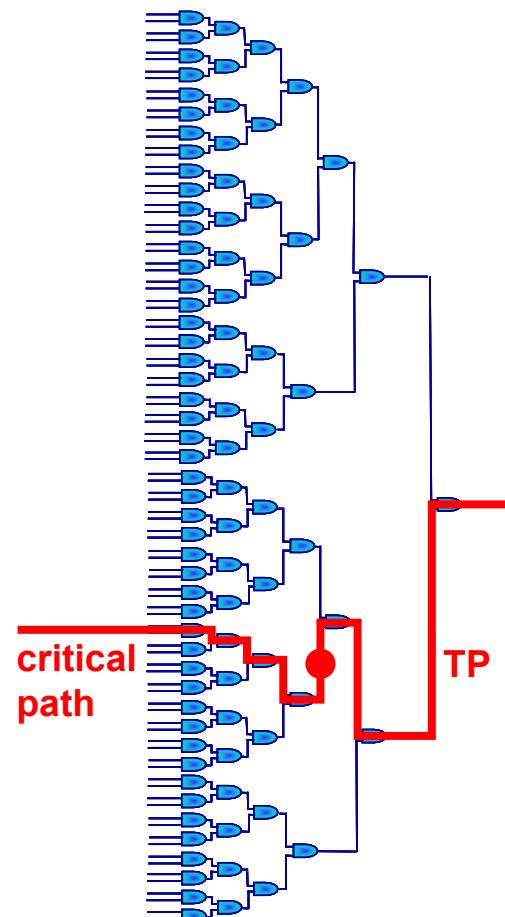

Abbildung 1.11: DFT-Flow

Der Schwerpunkt liegt auf dem Einbau von Testpunkten zur Kontrollierbarkeit und Beobachtbarkeit insbesondere in sogenannten Fan-out-Free-Regions (FFR), das sind Bereiche mit sehr vielen Eingängen und nur einem Ausgang (s. Abbildung 1.12).

Zu berücksichtigen ist, dass Testpunkte nur an den dafür erlaubten und vor allen Dingen sinnvollen Plätzen einzubauen sind. Randbedingung ist, dass solche zusätzlichen Verzögerungsglieder in Timing-kritischen Signalpfaden, z.B. sehr langen Verdrahtungsleitungen, nur unter Berücksichtigung des Gesamt-Delays der Leitungen eingebaut werden dürfen.

#### Konzept zur erweiterten RLC- Leitbahnextraktion

Durch die wachsende Komplexität, Miniaturisierung und Arbeitsfrequenzen im Gigahertz-Bereich stehen die Leitbahn- und Busstrukturen in nanoelektronischen Systemen immer mehr im Vordergrund des Entwurfsprozesses. In solchen Systemen werden die Verbindungsleitbahnen zum limitierenden Faktor für

die Schaltungs-Performance. Daher genügt es nicht mehr, die elektrischen Eigenschaften der Verbindungsleitbahnen nur als zusätzliche parasitäre Widerstände, Kapazitäten und Selbst-Induktivitäten anzusehen, sondern das Modell muss auch die Gegeninduktivitäten (Übersprechen) und ggf. Skin-, Proximity- und Substrat-Effekte mit berücksichtigen. Das Substrat lässt sich beispielsweise als RC-Gitter modellieren und kapazitiv an die Leitbahnen ankoppeln. Außerdem ist es wichtig, dass kritische Verbindungsleitbahnen oder Bussysteme bereits frühzeitig im Entwurf berücksichtigt und verifiziert werden können, um lange Iterationszyklen und Re-Designs zu vermeiden.

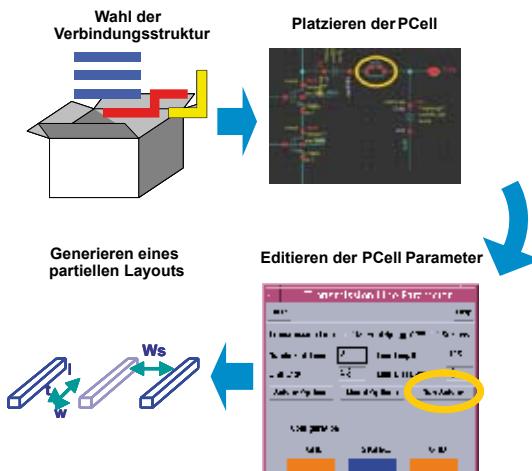

Abbildung 1.12: Gatter-Baum

In LEONIDAS+ wurde von Cadence ein leitbahnzentrierter, auf parametrisierbaren Zellen (PCells) basierender Entwurf, vorgeschlagen (s. Abbildung 1.13). Dieser erfüllt die oben genannten Anforderungen, wie die Berücksichtigung von Leitbahn- und Busstrukturen im Schematic, die Berücksichtigung von parasitären Leitbahn-Elementen, die Berücksichtigung von Skin- und Proximity-Effekt sowie Leitungsverluste durch das Substrat. Zur Validierung des Flows wurde ein einfaches Beispiel auf einem generischen Cadence-Prozess-Design-Kit (GPKD) aufgesetzt. Das PDK beinhaltet alle relevanten Daten einer generischen Technologie. Erste Simulationsergebnisse sind vielversprechend.

Abbildung 1.11:

Design-for-Test- (DFT)- Flow

Abbildung 1.12:

Fanout Free Region -

Gatter-Baum mit kritischem Pfad

**Abbildung 1.13:**

Leitbahnzentrierter Flow mit

Cadence-Prozess-Design-Kit

(GPKD)

Abbildung 1.13: leitbahnzentrierter Flow

Weitere Informationen zum Projekt finden Sie unter <http://leonidas-plus.ims.uni-hannover.de>.

**Projektkoordination:**

Infineon Technologies AG

Irmtraud Rügen-Herzig

fon +49 89 234-21046

**Projektmanagement:**

Universität Hannover

Dr. Markus Olbrich

fon +49 511 762-19661

Der Flow basiert auf einer partiellen Generierung des Layouts. Kritische Leiterbahn- oder Busstrukturen (z. B. Coplanar-Struktur) stehen für den Designer in einer Bibliothek als parametrisierbare Master-Zellen zur Verfügung. Die Instanzen dieser Master-Zellen lassen sich direkt im Schematic als Symbole einfügen und beliebig mit Hilfe der GUI parametrisieren. Im Hintergrund wird jede Instanz extrahiert und die parasitären RLCK-Werte sowie HF- und Substrat-Effekte werden berechnet. Das Schematic kann dann mit den als PCells eingefügten Leiterbahnstrukturen simuliert werden.

Der Flow wurde anhand eines Low-Noise-Amplifier-(LNA)-Beispiels getestet und qualifiziert. Vier kritische Leiterbahnen wurden hierfür als PCells modelliert und im Schematic eingefügt. Mit dem Beispiel wurden typische LNA-Charakteristiken simuliert (z. B. Verstärkung, PSS, NF). Als Referenz ist das vollständig extrahierte Layout simuliert worden. Es konnte gezeigt werden, dass alleine durch die Verwendung der genaueren Modelle für die vier kritischsten Verbindungsstrukturen erheblich genauere Resultate erzielt werden können, ohne dass sich die Simulationszeiten stark erhöhen. Zudem können damit Leiterbahnstrukturen frühzeitig im Flow berücksichtigt werden.

### Zusammenfassung

LEONIDAS+ zeigt bereits nach einem Jahr Projektlaufzeit eine Reihe wesentlicher Ergebnisse, die für eine leitbahnzentrierte Entwurfsmethodik erforderlich sind. Erfreulich ist dabei, dass die Partner nicht nur ihre jeweiligen Einzelinteressen verfolgen, sondern mit anderen an gemeinsamen Zielen arbeiten. Der Austausch über Firmengrenzen hinweg stärkt die beteiligten Partner und damit den Standort Deutschland.

Ohne die Ergebnisse von LEONIDAS+ wären schon jetzt einige Produkt-Entwicklungen nicht möglich gewesen. LEONIDAS+ ermöglicht den deutschen Firmen den Weg in die „Leiterbahn-Ära“.

## On-Chip Verbindungsstrukturen – Engpaß und Herausforderung beim Schaltungsentwurf

von Prof. Dr.-Ing. habil. Hartmut Grabinski

„Leitungen? Die sind nicht wichtig!“ Mit diesem Vorurteil haben nicht nur Mitarbeiter im Projekt LEONIDAS zu kämpfen. Warum die Berücksichtigung von Leitungseffekten bei zukünftigen Chipentwürfen enorm wichtig ist, beschreibt dieser Artikel.

Schon zu Beginn der Erfolgsgeschichte integrierter digitaler Schaltungen wurde mit zunehmender Arbeitsgeschwindigkeit mikroelektronischer Systeme schnell deutlich, daß die als Schaltelemente eingesetzten Transistoren keineswegs ideale Schalter repräsentierten. Vielmehr mußte das mehr und mehr dominierende analoge Verhalten von Transistoren schon beim Schaltungsentwurf berücksichtigt werden, wobei die Analysewerkzeuge Programme wie SPICE und deren Derivate eingesetzt wurden und immer noch werden. Der Einfluß der die einzelnen Schaltelemente verbindenden Leitungsstrukturen auf die Schaltungsdynamik konnte lange Zeit vernachlässigt werden. Später, als die Schaltgeschwindigkeiten weiter zunahmen, wurden die Einflüsse von Verbindungsstrukturen z.B. mit Hilfe einzelner oder auch kaskadierter RC-Glieder näherungsweise berücksichtigt. In Ermangelung besserer Verfahren ist dies auch heute noch weitgehend der Fall.

Im Vergleich zu damals hat sich die Situation jedoch dramatisch verändert: Moderne digitale Schaltungen beinhalten mehrere Millionen Transistoren, die internen

Taktraten betragen einige Gigahertz, und die Gesamtlänge der Verbindungsleitungen innerhalb moderner Prozessoren beläuft sich auf jeweils mehrere Kilometer bei bis zu etwa 10 Verdrahtungsebenen. Für die nähere Zukunft werden Gesamtleitungslängen von ca. 30 km/Schaltung bei Taktraten von einigen 10 GHz prognostiziert, aber schon jetzt kämpfen Halbleiterhersteller massiv mit den parasitären Einflüssen von Verbindungsstrukturen. Letztere haben sich inzwischen als limitierender Faktor hinsichtlich der Arbeitsgeschwindigkeit moderner Schaltungen erwiesen und dominieren deren dynamisches Verhalten. Entsprechend besteht hier dringender Handlungsbedarf beim Entwurf moderner Schaltungen.

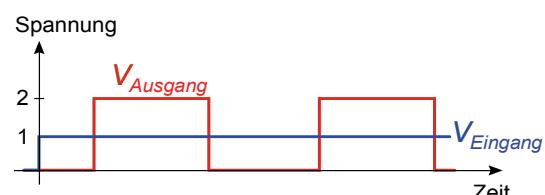

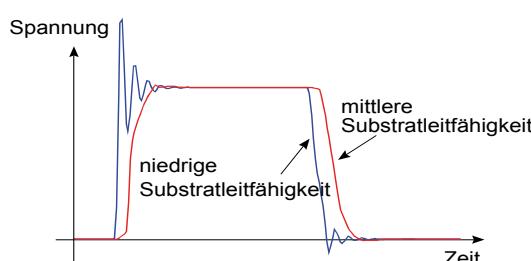

Abbildung 1.14

**Abbildung 1.14:**

Leitungen verhalten sich seltsam: Obwohl das Eingangssignal (blaue Kurve) einer idealen Leitung endlicher Länge nach dem Einschalten konstant bleibt (Einheitssprung), ist das Ausgangssignal (rote Kurve) ein Rechtecksignal doppelter Amplitude. Letzteres ist auf Reflexionen sowohl am Leitungsende als auch am Leitungseingang zurückzuführen.

### Problem 1: Wellenausbreitungseffekte

Bei den auf einzelnen Leitbahnen oder Leitbahnsystemen (z.B. Busstrukturen) auftretenden, parasitären Effekten handelt es sich im wesentlichen um Erscheinungen wie

- » endliche Ausbreitungsgeschwindigkeit,

- » Dispersion,

- » Kopplung,

- » Reflexion und

- » Ein- und Abstrahlung

Mit Ausnahme der Kopplung (zumindest bei hinreichend niedrigen Signalfrequenzen) handelt es sich hierbei um typische Wellenausbreitungseffekte (vgl. Abb. 1.14), die mathematisch grundsätzlich anders formuliert werden, als dies bei der Behandlung konzentrierter Bauelemente der Fall ist: Letztere werden mit Hilfe gewöhnlicher Differentialgleichungen, erstere mit Hilfe partieller Differentialgleichungen beschrieben. Werkzeuge wie SPICE sind im wesentlichen Programme zur Lösung großer Systeme gewöhnlicher (auch nichtlinearer) Differentialgleichungen, und es ist recht schwierig, solche Programme mit Algorithmen zur Lösung partieller Differentialgleichungen zu „verheiraten“. Grundsätzlich gibt es bereits Lösungen für dieses Problem, es bedarf hier aber umfangreicher Modifikationen vorhandener Entwurfssoftware, und viele Anwender scheuen (aus durchaus nachvollziehbaren Gründen) hiervor zurück.

Eine weitere Schwierigkeit liegt darin, überhaupt hinreichend leistungsfähige Algorithmen zur Beschreibung obiger Effekte zu finden. Es gibt hier vielversprechende Ansätze, aber das universelle Verfahren schlechthin existiert bis heute nicht.

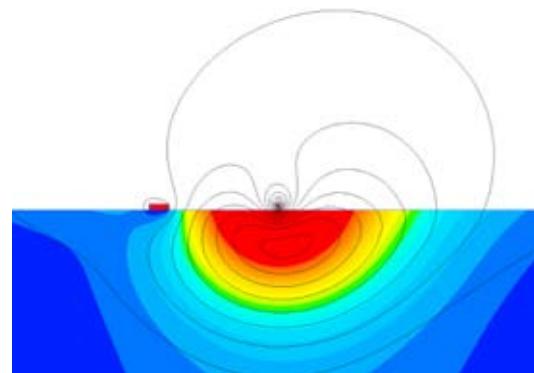

### Problem 2: Substrateffekte

Typisch für die derzeitigen integrierten Schaltungen ist es, daß sowohl aktive als auch passive Elemente über einem mehr oder weniger gut leitenden Substrat angebracht sind. Für Leitbahnen folgt daraus, daß die Verbindungsstrukturen umgebenden elektromagnetischen Felder in das Substrat eindringen können, was zu einer signifikanten Beeinflussung der Signalübertragung führt (Abb. 1.15). Nimmt man etwa an, daß zumindest quer zur Signalausbreitungsrichtung eine quasistationäre Betrachtungsweise noch adäquat ist (was auf Chips eingeschränkt und auf Boards bei höheren Frequenzen gar nicht mehr gilt), man also elek-

trische und magnetische Felder getrennt voneinander betrachten kann, so wirkt ein schwach leitendes Substrat bei höheren Frequenzen als Isolator. Dies führt zu einer signifikanten Abnahme der Eigenkapazität und damit zu einer sehr stark frequenzabhängigen Zunahme kapazitiver Kopplung. Andererseits bewirkt das Eindringen des magnetischen Feldes in das Substrat aufgrund von Skin- und Proximityeffekten eine (durchaus wünschenswerte) Abnahme von Koppel- und Selbstinduktivitäten bei höheren Frequenzen, gleichzeitig aber eine Zunahme ohmscher Verluste aufgrund massiver Ströme im Substrat: Das Substrat wirkt dann als Rückleiter, selbst wenn ein separater Rückleiter vorgesehen ist (Abb. 1.16). Umgekehrt kommt es bei niedrigeren Frequenzen und/oder schwacher Substratleitfähigkeit zu massiver induktiver Kopplung, auch (und im Gegensatz zur elektrischen Kopplung) über weite Distanzen. Es gibt hier bereits Verfahren zur Berechnung, die aber bis heute so gut wie nicht in bestehende Entwurfswerkzeuge integriert sind.

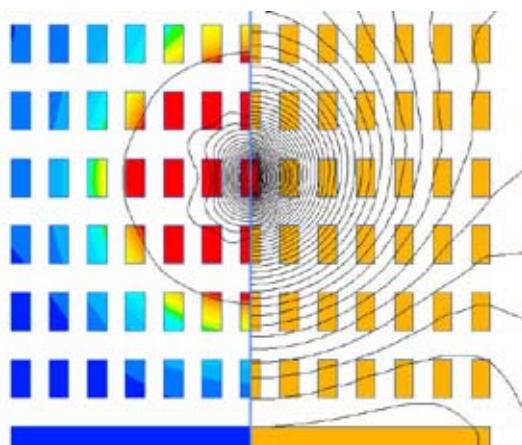

Abbildung 1.16:

Trotz vorhandenen Rückleiters (Rechteck links) fließt der größte Teil des Rückstroms bei hohen Frequenzen im Substrat unterhalb des Signalleiters (rot = hohe Stromdichte) und verursacht massive Verluste. Die schwarzen Linien sind magnetische Feldlinien.

Abbildung 1.16

### Problem 3: Induktivitäten

Auf Boards ist es schon lange notwendig, auch die Einflüsse magnetischer Felder zu berücksichtigen, während dies in der Vergangenheit auf Chip-Level eher von akademischem Interesse war. Inzwischen sind sich aber führende Halbleiterfirmen wie z.B. IBM, Infineon und Intel einig, daß induktive Effekte auch on-Chip zu beachten sind. Dies erweist sich als nicht ganz einfach, was nicht allein auf die mangelnde Erfahrung von Designern mit dieser Materie zurückzuführen ist. Vielmehr ist ein wesentliches Problem darin zu suchen, daß die Strompfade, insbesondere für den Rückstrom eines Signals, aufgrund ihrer Mannigfaltigkeit nur sehr schwer zu bestimmen sind. Letzteres ist aber von zentraler Bedeutung für die Berechnung von Selbst- und Koppelinduktivitäten. Erschwerend kommt hinzu, daß speziell die Rückstrompfade i.a. stark frequenzabhängig sind. Hierauf wurde bereits im Zusammenhang mit der Substratproblematik hingewiesen. Aber auch völlig ohne leitendes Substrat ergibt sich für die Rückstrompfade, allein aufgrund von Proximityeffekten, eine starke Frequenzabhängigkeit (Abb. 1.17). Auch hier existieren schon Verfahren zur Berechnung, aber es fehlt ebenfalls die Integration in die verwendeten Entwurfswerkzeuge.

Abbildung 1.15

Abbildung 1.15:

Ausgangssignale identischer Leitungen bei trapezförmigem Eingangssignal und unterschiedlichen Substratleitfähigkeiten: Allein aufgrund verschiedener Substratleitfähigkeiten unterscheiden sich die Ausgangssignale signifikant voneinander.

**Abbildung 1.17:**

Auch ohne Substrat kommt es aufgrund des Proximity-Effektes zu starker Frequenzabhängigkeit von Induktivität und Widerstand:

Signalleiter (Mitte) umgeben von lauter Rückleitern; rechts Stromverteilung bei 1MHz, links Stromverteilung bei 40 GHz (rot = hohe Stromdichte, blau = niedrige Stromdichte). Die schwarzen Linien sind wieder magnetische Feldlinien.

Abbildung 1.17

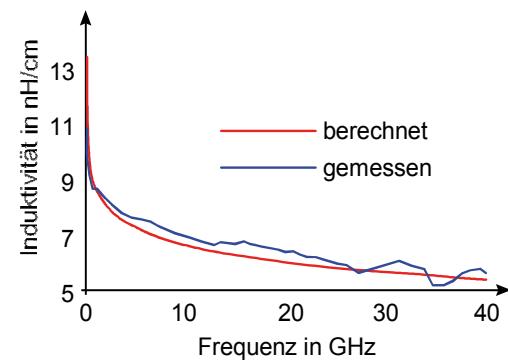

**Abbildung 1.19:**

Vergleich zwischen Messung und Berechnung des Induktivitätsbelages einer Leitung über leitendem Substrat.

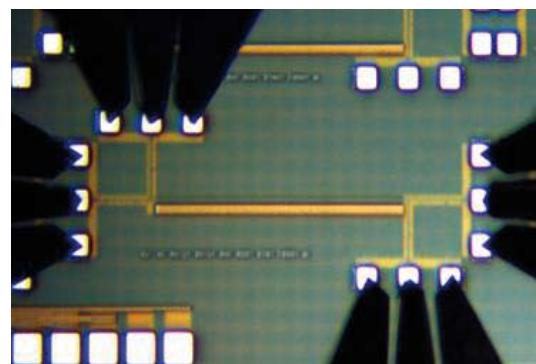

#### Problem 4: Messung

Man kann bekanntlich viele Thesen aufstellen und vieles berechnen. Die Stunde der Wahrheit schlägt aber dann, wenn es um eine meßtechnische Verifikation geht. Letztere gestaltet sich auf dem Chip als äußerst schwierig. Dies liegt zum einen an der Kleinheit der zu messenden Strukturen (Leitbahnbreiten im Subμ-Bereich) im Vergleich zu den Abmessungen der Meßapparatur (Meßspitzen im mm-Bereich und Meßleitungslängen von ca. 1m), zum anderen an den hohen Frequenzen (gegenwärtig bis maximal ca. 100 GHz) und der notwendigen Breitbandigkeit der Messung (vgl. Abb. 1.18).

**Abbildung 1.18:**

On-Wafer Meßtechnik an der Universität Hannover: Messung des Signalverhaltens an einer Doppelleitung; zu sehen sind die vier Hochfrequenzmeßspitzen und die Doppelleitungsstruktur unter dem Mikroskop.

Abbildung 1.18

Besonders schwierig ist auch die Berücksichtigung des leitenden Substrats. Entsprechende Meßtechniken wurden in den letzten Jahren, speziell auch in Hannover, entwickelt, ebenso Berechnungsverfahren (Abb. 1.19). Bei den Berechnungsverfahren handelt es sich i.a. um Feldberechnungen. In Ausnahmefällen lassen sich auch analytische Ausdrücke ermitteln. So wurde zur Berechnung des Induktivitätsbelages in Abb. 1.19 die einfache Gleichung

$$L'(\omega) \approx \frac{\mu_0}{8\pi} + \frac{\mu_0}{12\pi} \left\{ 3 + 4\sqrt{2} |k| (T_{ox} + T_s/2) + \frac{2\sqrt{2}}{\pi} |k| (w + T_s) + 6 \ln \frac{2\pi}{\gamma |k| (w + T_s)} \right\}$$

entwickelt. Hierin sind  $\gamma = 1,781\dots$  ( $\ln \gamma$  = Euler-Mascheroni-Konstante),  $|k| := \sqrt{\omega \mu_0 \sigma_{substr}}$ ,  $T_{ox}$  die Oxiddicke,  $T_s$  die Leitbahnhöhe und  $w$  die Leitbahnbreite.

Abbildung 1.19

#### Schluß

Die oben exemplarisch aufgeführten Punkte können sicherlich noch spezifiziert und erweitert werden. Sie geben aber eine Übersicht und einen ersten Einblick in die Problematik. Während Einzellösungen häufig schon existieren, fehlt deren Einbindung in bestehende Entwurfswerkzeuge nahezu gänzlich. Die Gründe hierfür sind nicht nur rein sachlicher Art. Es zeichnet sich aber ab, daß schon gegenwärtig beim Design komplexer Schaltungen wesentlich mehr parasitäre Effekte zu berücksichtigen sind, als dies in der Vergangenheit notwendig war. Bei sehr schnellen Schaltungen werden Entwurfstechniken erforderlich sein, die die Verbindungsstrukturen ins Zentrum des Entwurfs stellen (sog. „Interconnect Driven Design“). Hierfür sind entsprechende Werkzeuge unerlässlich.

#### Kontakt:

Prof. Dr.-Ing. Hartmut Grabinski

Laboratorium für

Informationstechnologie

Universität Hannover

Schneiderberg 32

30167 Hannover

fon: +49 (511) 762-5030

grabinski@ifi.uni-hannover.de

Weitere Informationen finden Sie unter <http://www.ims.uni-hannover.de/~grabinsk/>

# Nachrichten von den Projekten

[www.edacentrum.de/newsletter/](http://www.edacentrum.de/newsletter/)

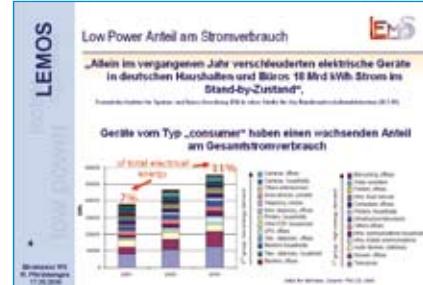

## Projektinterner LEMOS-Workshop schafft Synergien

Abbildung 1.22

Das Projekt LEMOS (Low-Power Entwurfsmethoden für mobile Systeme) veranstaltete im Anschluss an den Ekompass-Workshop am 18. Mai einen projektinternen Workshop. Insgesamt 18 Teilnehmer diskutierten dabei über 7 Vorträge zum Thema Verlustleistungs-Abschätzung und -Optimierung. Besonderes Highlight bildete diesmal der Gast-Vortrag von Kees Veelenturf, der die Arbeiten im MEDEA-Projekt LoMoSA (Low-power platform for Mobile multi-media System Applications) vorstelle. In der anschließenden Diskussion wurde zusätzlich über die möglichen Synergien zwischen den beiden Projekten nachgedacht. (Jens Appell)

## LEONIDAS+ mit 5 Beiträgen auf dem SPI-Workshop

Auf dem IEEE-Workshop „Signal Propagation on Interconnects“ (SPI) in Berlin vom 8. bis 12. Mai 2006 war das Projekt LEONIDAS+ mit insgesamt fünf Beiträgen (davon drei Vorträge) vertreten. Aufgrund der großen Konkurrenz ist dies ein besonderer Erfolg, weil zum 10-jährigen Jubiläum des Workshops überraschend viele Paper eingereicht wurden. Der SPI-Workshop ist im Bereich der Interconnect-Eigenschaften international renommiert. Die Qualität des Workshops liegt auf Konferenz-Niveau. (Markus Olbrich)

## Englisch- und deutschsprachiger Flyer zu den laufenden Ekompass Projekten erschienen

Abbildung 1.23

Ab sofort ist eine Gesamtübersicht über die aktuellen Ekompass-Projekte in englischer bzw. deutscher Sprache verfügbar. Weiterhin erhalten Sie zu den abgeschlossenen Projekten detaillierte Projektflyer, in denen ausführlich über die bisherigen Forschungsergebnissen berichtet wird. Die Flyer sind kostenlos als Download über die Webseite des edacentrum bzw. auf Anfrage in gedruckter Form erhältlich. (NM)

## Kooperationsworkshops in Planung

Im Rahmen des Ekompass-Workshops trafen sich auch in diesem Jahr Mitarbeiter der Projekte, um gemeinsame Kooperationsaktivitäten für das laufende und das kommende Jahr zu besprechen. Auf besonderes Interesse stießen dabei die Themen „System Planning & System Requirement Management“ und „Technologien und ihre Auswirkungen auf den Entwurfsprozess“. Zu beiden Themen sind Kooperationsworkshops geplant. Der Workshop zum Thema „System Planning“ wird Ende dieses Jahres, der Workshop zum Thema „Technologie“ wird Anfang nächsten Jahres stattfinden. Veranstaltungsort wird in beiden Fällen Hannover sein. Wenn Sie Interesse an den Workshops haben, setzen Sie sich ab sofort mit uns in Verbindung. (CH)

## Drei neue Projekte erhalten ein Label

Auf den beiden vergangenen Sitzungen des Steuerungsgremiums erhielten drei weitere Projekte das begehrte Label. Die Partner der Konsortien sind damit aufgefordert, ihre Anträge zusammen mit der Vorhabenbeschreibung beim Projektträger IT einzureichen. (Pp)

**Abbildung 1.22:**

Gruppenbild vom projektinternen LEMOS-Workshop am 18. Mai 2006 in Hannover

**Abbildung 1.23:**

Übersichtsflyer zu den aktuellen Förderprojekten in englischer bzw. deutscher Sprache

**Kont@kt (LEMOS):**

Dr. Jens-E. Appell

fon: 0441-9722-235

jens.appell@offis.de

**Kont@kt (Kooperationsworkshop):**

Dr. Cordula Hansen

fon: 0711-2807 956

hansen@edacentrum.de

**Kont@kt (LEONIDAS+):**

Dr. Markus Olbrich

fon: 0511-762 19661

olbrich@ims.uni-hannover.de

**Kont@kt (Steuerungsgremium):**

Dr. Jürgen Haase

fon 0511 762-19698

haase@edacentrum.de.

# Die Projekte auf dem Ekompass-Workshop 2006

[www.edacentrum.de/newsletter/](http://www.edacentrum.de/newsletter/)

## Ekompass-Projekte präsentierte sich im Mai

Auf dem im Mai abgehaltenen Ekompass-Workshop 2006 präsentierte die Projekte DETAILS, LEMOS, LEONIDAS+, PRODUKTIV+, URANOS und SIDRA ihre jüngsten Ergebnisse in Vorträgen und auf Postern. Um Dopplungen zu verhindern haben wir in dieser Rubrik auf weitere Projektnachrichten verzichtet und nur Bilder als Platzhalter eingefügt. Bitte lesen Sie den ausführlichen Bericht vom Ekompass-Workshop ab Seite 21.

Die kompletten Foliensätze der Projekte sind im Tagungsband des Ekompass-Workshops 2006 abgedruckt. Er ist im edacentrum erhältlich.

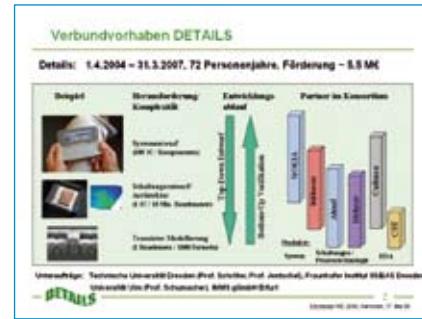

## DETAILS

## 2 Neues aus dem edacentrum

### Publikationen

[www.edacentrum.de/pressespiegel/](http://www.edacentrum.de/pressespiegel/)

In der Zeitschrift „Elektronik“ erschien in Heft 4 vom 21. Februar 2006 ein kurzer Bericht vom edaForum05. Der Beitrag trägt den Titel „EDA - Wirtschaftsfaktor oder Highend-Informatik?“. In der Zeitschrift „it - Information Technology“ erschien in Heft 2 vom April 2006 ein achtseitiger Beitrag über EDA-Forschung und das edacentrum mit dem Titel „EDA - Eine Voraussetzung für die Nanotechnologie“. Außerdem berichtete das BMBF am 10.03.2006 in BMBF Online unter der Schlagzeile: „BMBF veröffentlicht neue Broschüre zum Chipentwurf“ über das Erscheinen der EDA-Broschüre. (Pp)

Ansprechpartner zu Publikationen:

Ralf Popp, 0511 762-19697, [popp@edacentrum.de](mailto:popp@edacentrum.de).

Einen DAC-Preview finden Sie in diesem Heft auf S. 32.

Weitere Informationen unter: <http://www.dac.com>.

unter

[www.edacentrum.de/](http://www.edacentrum.de/)

newsletter/

finden Sie im Internet

weitere Informationen.

### Trendbericht der Design Automation Conference (DAC) 2006

[www.edacentrum.de/mitglieder\\_intern/](http://www.edacentrum.de/mitglieder_intern/)

Auch dieses Jahr werde ich für das edacentrum auf der DAC (24.-28.7.2006 in San Francisco, CA) sein und Augen und Ohren offen halten, was die EDA-Experten – insbesondere in den Panel-Diskussionen – zu sagen haben. Im Laufe des Spätsommers wird dann wieder von Ralf Popp und mir der umfangreiche DAC-Trendbericht in gewohnter Qualität – vielleicht aber mit ein paar Überraschungen – erstellt und an die Mitglieder verteilt werden. Sollten Ihnen im Vorfeld ganz besondere Wünsche unter den Nägeln brennen, z.B. die Aussagen einer ganz bestimmten Session oder der Inhalt eines ganz bestimmten Vortrages – dann werde ich versuchen, dies im Rahmen der zeitlichen Möglichkeiten in mein Besuchs- und Berichtsprogramm einzubinden. Und wenn Sie auch zur DAC fahren? Dann freue ich mich auf persönliche Gespräche mit Ihnen auf der DAC, um Eindrücke und Erfahrungen auszutauschen. Auch auf Ihrem Messestand besuche ich Sie gerne. Für im Vorfeld der DAC geäußerte Anregungen rund um die große EDA-Veranstaltung bin ich ebenfalls dankbar!

Ansprechpartner zum DAC-Bericht:

Dr. Dieter Treytnar, 0511 762-19687, [treytnar@edacentrum.de](mailto:treytnar@edacentrum.de).

**PRODUKTIV+**

**Was ist Produktivität?**

- Mit Produktivität bezeichnet man die Ergiebigkeit eines Wirtschaftsprozesses. Sie bewertet eine Produktionsmenge (Output) in Bezug auf den dazu benötigten Faktoreinsatz (Input).

$P = \frac{\text{Output}}{\text{Input}}$

**LEONIDAS**

**Technische Herausforderungen**

**Keynote DATE 2006**

**DEUS**

**Deep Sub-Micron**

0.9 Nanometer and Beyond

- The wires are now slimmer than the transistors

- Challenging timing, power and synthesis

- The wiring is getting congested

- Not enough power available

- Combinational logic

- Increasing layout density

- Layouts must begin to dominate

- Longer gate delay than existing for performance products

- Very large memory requirements

- Designing memory and IC design more difficult

- Process device variability is increasing

- Assessing predictability and yield

Montage: Prinzipiell ZUR LEONIDAS

**SIDRA**

**Trends in Automotive Semiconductors Today**

**MEDEA+**

**URANOS**

**Verwertungsabsichten**

**AMD**

Reduzierung der Anzahl von Silicon-Spikes zur Stärkung Marktposition

**Infineon**

Erhöhung der Wettbewerbsfähigkeit im Halbleitermarkt für Sicherheitselektronik

**IC-Haushalt**

Verbesserte Qualität, Robustheit, Wiederverwendbarkeit und TTM von IP-Modulen um Marktposition auszubauen

**PZI**

Erschließung neuer Geschäftsfelder durch Übernahme von Entwicklungsabgaben und Beratung von KMUs

## ★ Termine und Formalien für neue Projekte

[www.edacentrum.de/projekttermine](http://www.edacentrum.de/projekttermine)

Die Termine für die Einreichung zur Sitzung des Steuerungsgremiums am 26. September 2006 in Hannover sind

- » Anmeldung einer Einreichung bis: **14.8.2006**

- » Abgabe der ersten Version bis: **28.8.2006**

- » Abgabe der letzten Version bis: **11.9.2006**

Bitte berücksichtigen Sie bei der Einreichung nicht nur die Termine, sondern unbedingt auch die Vorgaben bzgl. des Umfangs. Projektskizzen dürfen maximal einen Umfang von 16 Seiten haben, Vorhabenbeschreibungen einen Umfang von 50 Seiten. Bei beiden Angaben sind Titelseite, Inhaltsverzeichnis und Anhang nicht eingerechnet. (CH)

Ansprechpartner zum Thema:

Dr. Cordula Hansen, 0711 2807956, [hansen@edacentrum.de](mailto:hansen@edacentrum.de)

## Datensicherheit am edacentrum

<https://www.edacentrum.de/>

Ab sofort werden alle passwortgeschützten Webseiten des edacentrum verschlüsselt (https-Protokoll) übertragen. Für Sie ändert sich dadurch nichts, Sie haben aber die Gewissheit, dass sowohl Ihr Passwort als auch die Inhalte der Webseiten verschlüsselt übertragen werden. Hiervon profitieren auch die Nutzer der vom edacentrum administrierten Projektwebseiten. (AV)

Ansprechpartner zur Datensicherheit am edacentrum:

Dr. Andreas Vörg, 0511 762-19686, [voerg@edacentrum.de](mailto:voerg@edacentrum.de).

## Vergünstigungen für Start-ups

[www.edacentrum.de/mitgliedschaft.html](http://www.edacentrum.de/mitgliedschaft.html)

Start-up-Unternehmen, die jetzt einen Mitgliedsantrag stellen, erhalten ab sofort alle Leistungen für Mitglieder, werden allerdings formal erst mit dem Beschluss des Aufsichtsrates im Oktober aufgenommen. Damit brauchen diese Antragsteller zunächst keinen Beitrag zu zahlen, können also kostenlos schnuppern. Falls sie im Jahr 2007 nicht Mitglied bleiben möchten, genügt eine reguläre Kündigung (einen Monat zum Quartalsende). Mitgliedsanträge sind im Internet oder direkt beim edacentrum erhältlich.

Ansprechpartner zur Mitgliedschaft:

Dr. Jürgen Haase, 0511 762-19698, [haase@edacentrum.de](mailto:haase@edacentrum.de).

# Neues aus der EDA-Clusterforschung

[www.edacentrum.de/clusterforschung/](http://www.edacentrum.de/clusterforschung/)

Neuigkeiten von den Projekten SAMS und FEST finden Sie innerhalb des Berichts vom Ekompass-Workshop auf Seite 21. Darüber hinaus freuen wir uns über das im Mai erteilte Label für das dritte Clusterforschungsprojekt und einen erfolgreich vollzogenen Auftritt der Clusterforschung auf der ISCAS, der bereits in der letzten Ausgabe des Newsletters angekündigt wurde.

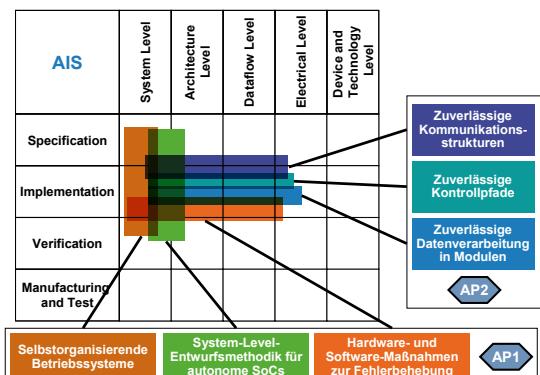

#### Abbildung 1.24:

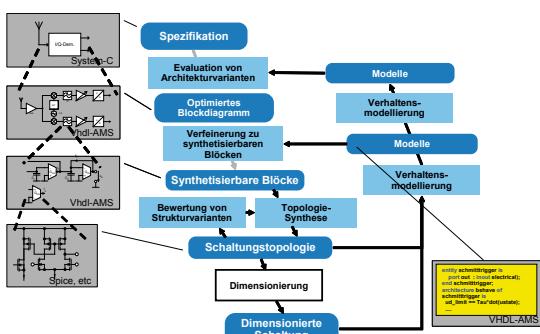

Die Forschungsthemen des AIS-Projekts konzentrieren sich im ersten Schwerpunkt (AP1) auf die Systemebene zur Exploration und Optimierung von Systemen. Der zweite Schwerpunkt (AP2) fokussiert sich auf die Erfassung und Dimensionierung der Komponenten eines Systems.

#### Label für drittes Clusterforschungsprojekt

Der Vorhabenbeschreibung des Projekts „Autonome Integrierte Systeme“ (AIS) wurde im Mai vom Steuerungsgremium das Label erteilt. Das AIS-Konsortium wurde damit aufgefordert, den Projektantrag beim BMBF einzureichen. Geplant ist, dass AIS im Oktober 2006 mit seinen Forschungsarbeiten startet.

Ziel des damit dritten Clusterforschungsprojektes ist die Erforschung neuer Methoden, Werkzeuge, Architekturen und Betriebssysteme für den Entwurf Autonomer Integrierter Systeme, um Zuverlässigkeitsspekte durchgängig auf allen Entwurfsebenen schon in der Planung zu berücksichtigen. Das Projekt AIS wird EDA-Lösungen im Bereich autonomer Hardware und Software erforschen. Hierzu zählen Schaltungskonzepte auf Transistorebene, die Störungen tolerieren können, selbstheilende Speicher- und Prozessorarchitekturen auf Gatter- und Register-Transfer-Ebene sowie selbstorganisierende Hardware- und Software-Plattformen mit redundanten Prozessor- und Kommunikationsressourcen auf Systemebene. Um die dadurch

entstehenden vielfältigen neuen Freiheitsgrade im Entwurf beherrschen zu können, sind neue Entwurfsmethoden zu erforschen, die autonome Architekturen auf unterschiedlichen Technologieebenen hinsichtlich ihrer Eignung für gegebene Applikationen und unter Berücksichtigung vorgegebener Zuverlässigkeitssanforderungen bewerten und damit eine automatisierte, applikationsspezifische Architekturbestimmung

Abb.1.24 edaMatrix

#### Der Jubiläums-Geburtstag naht: 5 Jahre edacentrum

[www.edacentrum.de/5jahre/](http://www.edacentrum.de/5jahre/)

Liebe Leserinnen und Leser, wir rufen Sie auf, uns bei der Auswahl zu unterstützen. Empfehlen Sie uns einen guten Wein, vorzugsweise aus Ihrer Region, den wir zur Mitgliedsammlung verkosten und ggf. kürnen können. Sie sind herzlich eingeladen, bei der „Auslese“ zur Mitgliederversammlung und mit zu entscheiden. Wir freuen uns auf Sie!

Ort, Zeitpunkt und die Modalitäten der Kür des „edaWein06“ werden rechtzeitig im Internet und im kommenden newsletter bekannt gegeben.

Kindergeburtstage sind auch für Eltern besondere Tage, aber Niemand würde nach einer Handvoll Jahren bei dem Geburtstag eines Kindes von einem Jubiläum sprechen. Für das edacentrum sieht das schon anders aus:

Am 3. September 2006 jährt sich die Eröffnung des edacentrum durch die damalige Bundesministerin Frau Edelgard Bulmahn zum fünften Mal. Für das edacentrum ist sein fünfjähriges Bestehen ein Grund zur Freude und Anlass zur Herausgabe eines edlen Tropfens (möglichst gleichen Alters), dem „edaWein06“.

Der „edaWein06“ – Herkunft und Erzeuger bleiben vorerst eine Überraschung – soll zur Mitgliederversammlung am 12. Oktober 2006 (s. nebenstehende Meldung) feierlich gekürt werden. Anschließend geht er – speziell etikettiert – zu einer längeren Weinprobe auf „Reisen“. (Pp)

Ansprechpartner zu Jubiläum und edaWein06:

Ralf Popp, 0511 762-19697, [popp@edacentrum.de](mailto:popp@edacentrum.de)

#### Einladung zur Mitgliederversammlung am 12.10.06

[www.edacentrum.de/](http://www.edacentrum.de/)

Die diesjährige – und inzwischen fünfte – Mitgliederversammlung des edacentrum findet am Donnerstag, den 12.10.2006, nachmittags in den Räumen der Universität Hannover, Laboratorium für Informationstechnologie (LFI), statt. Der Vorstand des edacentrum e.V. und die Geschäftsführung der edacentrum GmbH werden berichten. Zum vorhergehenden Mittagessen wird der „edaWein06“ gekürt.

Weitere Aktionen unter dem Motto „Von Mitgliedern für Mitglieder“ sind gewünscht. Wenn Sie einen Vorschlag machen möchten, sprechen Sie uns an.

Alle Mitglieder sind herzlich zur Teilnahme eingeladen. Eine Einladung mit der Agenda geht Ihnen rechtzeitig auf dem Postweg zu. (Pp)

Ansprechpartnerin zur Mitgliederversammlung:

Maren Sperber, 0511 762-19699, [info@edacentrum.de](mailto:info@edacentrum.de)

**Kont@kt:**

Dr. Volker Schöber

fon: 0511 762 19688

schoeber@edacentrum.de/

**Abbildung 1.25:**

Das SAMS-Projekt war bei der diesjährigen ISCAS 2006 (s. S. 30) mit einer eigenen Session zum Thema „Analog Circuit“

#### Wireless World Research Forum

Das WWRF ist eine Organisation, die sich zum Ziel gesetzt hat, global Forschung und Entwicklung für mobile und drahtlose Systeme voranzutreiben. Hierzu werden strategische Visionen der Ausrichtung der Forschung erstellt und neue technische Vorteile für zukünftige Netzwerke erarbeitet. Es finden regelmäßige Meetings statt, bei denen sich die Teilnehmer über den aktuellen Stand der Entwicklung austauschen. Das nächste Meeting wird in Heidelberg vom 15.-17. November 2006 stattfinden. Weitere Informationen finden Sie unter: <http://www.wireless-world-research.org/>.

ermöglichen. (siehe Abbildung 1.24). Die geplanten Forschungsaktivitäten werden dabei anhand eines plattformbasierten Entwurfs evaluiert, der verschiedene Prinzipien, Abstraktionsebenen und Entwurfsmethoden für Komponenten und Systeme für Autonome Integrierte Systeme zusammenfasst.

In Kooperationstreffen mit der Industrie wurden bereits erste Schritte zur Projektzusammenarbeit in den nächsten Jahren eingeleitet. Das Forschungskonsortium stellte dabei die wissenschaftlichen Ziele des Projektes den interessierten Industriepartnern vor. Auch wurden die Anforderungen der Industrie vorgebracht und abgestimmt, die im Rahmen des Projekts berücksichtigt werden sollen. In einem anderen Treffen wurde diskutiert, in welcher Form das AIS-Projekt Beiträge zu dem Wireless World Research Forum (WWRF) leisten kann. Die Mitarbeit zur Erarbeitung eines White-Papers zum Thema „Reconfigurable Computing“ sowie eine Präsentation der Ziele des Projekts im November beim nächsten Treffen des WWRF in Heidelberg wurden geplant. (VS)

#### SAMS mit einer Session auf der ISCAS 2006 Synthesis: A search for the holy grail?“ mit insgesamt 5 Beiträgen eingeladen

Mit mehr als 40 Zuhörern und intensiven anregenden Diskussionen war das Interesse - trotz der vielen parallelen Veranstaltungen - erfreulich hoch. Mit der Präsentation des Synthesekonzepts, das mit dem SAMS-Projekt verfolgt wird, konnte ein wichtiger Fortschritt im Bereich der Synthese analoger Schaltungen dargestellt werden. Auch fand der innovative transformatorische Ansatz zur Verfeinerung von Modulen eine hohe Beachtung. Während der Konferenz ergaben sich neue Kontakte zu den Universitäten Bristol (Grossbritannien) und Twente (Niederlande), die auch in diesem Themengebiet arbeiten. Mit der Special Session wurde die internationale Sichtbarkeit von SAMS und der Clusterforschungsinitiative erhöht. (VS, Foto: Daniel Müller)

#### EDA-Achievement Award 2006 ausgelobt

[www.edacentrum.de/awards.html](http://www.edacentrum.de/awards.html)

Für besondere Forschungs- oder Entwicklungsleistungen im Bereich EDA (Electronic Design Automation) verleiht das edacentrum e.V. in diesem Jahr erneut den EDA Achievement Award. Damit sollen Leistungen hervorgehoben und prämiert werden, die in Projekten des Förderschwerpunktes Ekompass (Entwurfsplattformen komplexer angewandter Systeme und Schaltungen) erbracht worden sind.

Preiswürdig sind Arbeiten von Einzelpersonen oder Teams, die zur Erreichung der Ekompass-Ziele besonders beigetragen haben. Dabei sind insbesondere solche Beiträge erwünscht, die eine mess- und damit nachweisbare Verbesserung bzw. Beschleunigung des Entwurfsprozesses und damit einen industriellen Nutzen bewirkt haben.

Die Form der Bewerbung für den mit 2000,- Euro dotierten Preis ist freigestellt, muss aber die Dokumentation des Ergebnisses enthalten. Geeignet hierfür sind Veröffentlichungen, Meilensteinberichte, aber auch spezifisch für diesen Zweck erstellte Dokumentationen. Die Bewerbung ist bis zum 31. Juli 2006 an das edacentrum e.V. zu richten. Das Steuerungsgremium des edacentrum wird auf seiner Sitzung am 26. Sep-

tember die eingegangenen Beiträge begutachten und die prämierte Arbeit auswählen. Die Preisverleihung findet im Rahmen des edaForum06 vom 16. bis 17. November in Berlin statt. (Tr)

**Ansprechpartner zum EDA Achievement Award:**

Dr. Jürgen Haase, 0511 762-19698, [haase@edacentrum.de](mailto:haase@edacentrum.de).

#### Abbildung 2.01:

Die Gewinner des EDA-Achievement Awards der vergangenen Jahre:

2003: Prof. Dr.-Ing. Wolfram Büttner

2004: Dr.-Ing. Ralf Sommer (in Vertretung übernahm Frau Irmtraud-Rugen Herzog den Preis)

2005: Dr.-Ing. Sebastian Sattler

## Ekompass-Workshop 2006

Rückblick auf den 16. und 17. Mai 2006 in Hannover

Wie schon in den letzten Jahren kamen die Ekompass-Projekt-Teams im Frühjahr zum Ideen- und Meinungsaustausch nach Hannover in das Courtyard by Marriott Hotel. Im Juni ist dort die „Welt zu Gast bei Freunden“ und wohnt den Pressekonferenzen der hohen Fußballprominenz bei.

Mit über 120 Teilnehmern konnte der Ekompass-Workshop wieder an die Zeiten anknüpfen, in denen Reisen leicht und ohne lange Prüfung genehmigt wurden. Der Workshop bot wie immer einen guten Überblick über die international konkurrenzfähige Leistungsstärke der deutschen EDA-Forschung.

### Übersicht

In acht Übersichtsvorträgen und auf 31 Postern sowie durch einige Demonstrationen wurden die derzeit geförderten Ekompass-Projekte vorgestellt. Eine kurze Zusammenfassung der Vorträge finden Sie im Anschluss an diese Übersicht.

Darüber hinaus bot der Ekompass-Workshop reichlich Gelegenheit zum wissenschaftlich-technischen Austausch. So hatte das edacentrum im Auftrag des BMBF zu einer Diskussion um zukünftige Forschungsthemen aufgerufen (siehe Seite 22.). Außerdem wurde der jährliche Kooperationsmarkt unter dem Motto „Ideen suchen Anwender“ im Rahmen der Posterausstellung mit Rekordbeteiligung durchgeführt (siehe Seite 20).

Weitere Höhepunkte waren die eingeladenen Vorträge von Dr. Reinhard Ploss von Infineon, Prof. Dr. P. Lugli von der TU München und Prof. Dr. Christoph Grimm von der Universität Hannover, deren Vorträge im kommenden newsletter edacentrum 03 2006 besprochen werden.

Der gemeinsame Abend im Gartensaal des nahe gelegenen Neuen Rathaus von Hannover wurde mit der Verleihung der EDA-Medaille eröffnet. Dr. Peter Schwarz von der FhG-EAS in Dresden erhielt die Auszeichnung für sein Lebenswerk in Forschung und Lehre auf dem Gebiet Electronic Design Automation (s. rechts).

Der Ekompass-Workshop wurde auch in diesem Jahr von allen Beteiligten gelobt. Das gute Zusammenspiel der Partner, die tatkräftige Zusammenstellung der Teams, die gute Integration der Neuen, sowie das gute Veranstaltungsmanagement des edacentrum-Teams zeigen, dass eine Gemeinsamkeit erreicht wurde, die für die Zukunft viel erwarten lässt.

Und dass diese Zukunft bereits begonnen hat, zeigen die Planungen für das kommende Jahr, wenn der Ekompass-Workshop ein neues Gesicht und damit auch einen neuen Namen bekommen wird:

Aus dem Ekompass-Workshop wird der edaWorkshop, der sich der wissenschaftlich-industriellen EDA-Gemeinde über die Ekompass-Projekte hinaus öffnen wird und sich damit als zentrale deutsche EDA-Veranstaltung etablieren soll. Dazu wird der Rahmen erweitert, die Qualität durch ein Programmkomitee gesichert und die Veranstaltung zusammen mit dem BMBF, der DLR und der GI/GMM/ITG-Kooperationsgemeinschaft „Rechnergestützter Schaltungs- und Systementwurf“ organisiert. (Tr)

Kont@kt:

Dr. Dieter Treytnar

+49 511 762 - 19687

treytnar@edacentrum.de

## EDA-Medaille 2006 für Dr.-Ing. habil. Peter Schwarz

<http://www.edacentrum.de/awards.html>

Auf dem diesjährigen Ekompass-Workshop wurde Dr.-Ing. habil. Peter Schwarz für sein Lebenswerk in Forschung und Lehre auf dem Gebiet Electronic Design Automation (EDA) mit der EDA-Medaille ausgezeichnet. Damit werden die herausragenden Leistungen und das hohe Engagement von Dr. Schwarz zur Entwicklung von EDA gewürdigt, die er während seiner langjährigen Tätigkeit bei der Robotron Messelektronik Dresden, dem Zentralinstitut für Kybernetik und Informationsprozesse Dresden und dem Fraunhofer Institut IIS-EAS in Dresden gezeigt hat.

Dr. Schwarz hat die Geschichte von EDA seit ihren Anfängen in der DDR maßgeblich mitgestaltet. Zahlreiche wegweisende Beiträge auf vielen Teilgebieten sind mit seinem Namen verknüpft. Vor allem in den Bereichen der Modellierung und Simulation komplexer Systeme aus elektronischen und nichtelektronischen Komponenten hat er sich – auch später im größeren gewordenen Deutschland – ein hohes Renommee verschafft. Aus dieser Pioniertätigkeit entstand der erste Mixed-Signal-Simulator KOSIM in der DDR, der dort einen breiten Einsatz fand.

Dr. Schwarz verstand auch die Weitergabe seines Wissens immer als wesentlichen Teil seiner Aufgabe. So hat er sich neben der Betreuung zahlreicher Studenten und Doktoranden sehr erfolgreich um die Qualifikation und Wiedereingliederung arbeitsloser Ingenieure gekümmert und die Erstellung von multimedialen Lernmodulen betrieben. Er ist Koautor eines 2005 erschienenen Lehrbuchs über die Modellierung und Simulation von HF-Systemen.

Die EDA-Medaille 2006 wurde damit einer Persönlichkeit verliehen, die die EDA-Entwicklung in Deutschland auch unter schwierigen Randbedingungen über mehrere Jahrzehnte wesentlich vorangetrieben hat. (Tr)

Abbildung E.02a

Abbildung E.02b

Abbildung E.01:

360 Grad Panorama des Vortragssaumes auf dem Ekompass-Workshop 2006.

# Ekompass-Workshop 2006

## Kooperationsmarkt 2006

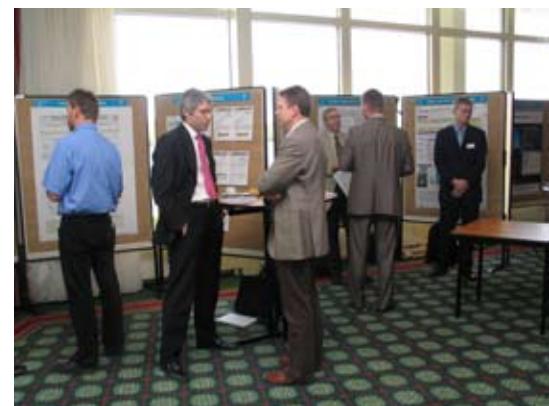

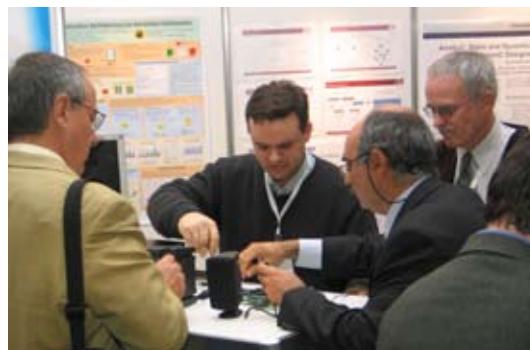

Getreu dem Motto „Ideen suchen Abnehmer – Markt sucht Innovationen“ war es ein voller Erfolg – das lässt sich mit Fug und Recht behaupten

### Kooperationsworkshops in Planung

Die Möglichkeit sich als Forschungseinrichtung oder als junges Unternehmen direkt im Netzwerk der EDA-Forschungsgemeinde und der großen EDA-Tool-Anwender zu präsentieren, hat in diesem Jahr 13 Institutionen nach Hannover zum Ekompass-Workshop gelockt. Mit der Verdopplung der Teilnehmerzahl im Vergleich zum Vorjahr ist dies ein neuer und erfreulicher Rekord für den Kooperationsmarkt.

Die Stimmung unter den Teilnehmern, die, ausgestattet mit Tisch & Plakatwand, Poster und Präsentationen, allen Anfragen in den Pausen rege Rede und Antwort standen, war gut und hoffnungsvoll – waren doch für Viele die Veranstaltung und der Ekompass-Workshop neu.

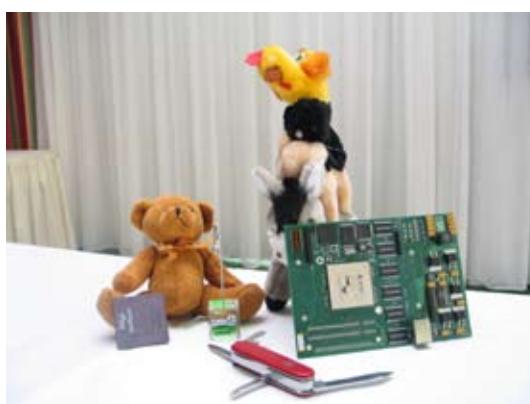

Die erfrischende Vorstellung der Aussteller (s. Abbildung E.03) anhand einer am Firmensitz orientierten virtuellen Deutschlandkarte vermittelte den Bezug zwischen Person und Institution. Dabei nutzten einige Aussteller die Gelegenheit mit einem „Mitbringsel“ (s. Abbildung E.04) besondere Aufmerksamkeit zu erregen. Beides hat sicherlich dazu beigetragen, den einen oder anderen lockeren Erstkontakt zu ermöglichen.

Abbildung E.03:

Abbildung E.04

Mit der AMO GmbH war in diesem Jahr auch wieder ein Start-up-Unternehmen beteiligt. Mentor stellte sein Business-Förderungsprogramm „Cre8 Venture“ für junge Unternehmen vor und brachte damit eine Neuheit in den Kooperationsmarkt. Aber auch „alte Hasen“ wie die TU München, die Uni Bremen und OFFIS zeigten sich wieder in voller Stärke in der Ausstellung (siehe Abbildung E.05)

Am Ende des Kooperationsmarkts konnten sowohl Teilnehmer als auch Organisatoren mit Stolz behaupten: „Ziel erreicht“. Eine Rundfrage bei den Ausstellern am zweiten Tag war eindeutig und gleichlautend: Die Teilnahme hat sich gelohnt. Die Stände wurden gut besucht und vor allem der erste Tag war erfüllt von Gesprächen und viel Interesse an den vorgestellten Themen. Zudem zeigten einige Kontakte einen deutlichen „Nachknüpfungscharakter“.

Abbildung E.05

Auch der vom edacentrum für die Teilnehmer erstellte Flyer zum Kooperationsmarkt fand wie schon im letzten Jahr große Resonanz. Alle Aussteller haben den Flyer in größerer Zahl zur „Zweitverwertung“ mitgenommen. Bleibt zu hoffen, dass eine Verteilung in den Hochschulkreisen neue Teilnehmer für den nächsten Kooperationsmarkt interessiert. Die Idee, beim eda-Workshop 2007 einen Call for Papers durchzuführen und dadurch wissenschaftliche Beiträge zu ermöglichen, kam unter den Ausstellern durchweg gut an. Es ist also auch in Zukunft mit regen Diskussionen und Fachbeiträgen zu rechnen. (CH, NM)

Abbildung E.05:

Der Kooperationsmarkt im Rahmen der Posterausstellung stimulierte manchen Kontakt.

Abbildung E.03:

Persönliche Vorstellung der Teilnehmer des Kooperationsmarktes durch Niklas Möller

Abbildung E.04:

Stilleben aus den persönlichen Mitbringsel der Teilnehmer des Kooperationsmarktes mit lokalem oder Firmenbezug

Kont@kt:

Dr. Cordula Hansen

+49 711 2807956

hansen@edacentrum.de

# Ekompass-Workshop 2006

Teilnehmer am

Kooperationsmarkt 2006

## Brandenburgische Technische Universität Cottbus

Lehrstuhl für Programmiersprachen und Compilerbau

Postfach 101344

03013 Cottbus

www-pscb.informatik.tu-cottbus.de

Prof. Dr. Peter Bachmann

Tel.: 0355 - 69 3886, Fax: 0355 - 69 3830

Peter.Bachmann@informatik.tu-cottbus.de

## Universität Siegen

Institut für Mikrosystemtechnik

Hölderlinstraße 3

57076 Siegen

www.rs.uni-siegen.de

Prof. Dr. Rainer Brück

Tel.: 0271 740 2375,

Fax: 0271 740 2473

rainer.brueck@uni-siegen.de

## Technische Universität Berlin

Inst. f. Technische Informatik und Mikroelektronik, FG Rechnertechnologie

FR 3-9, Franklinstr. 28/29

10587 Berlin

http://rt.cs.tu-berlin.de

Prof. Dr.-Ing. Hans-Ulrich Post

Tel.: 030-314-73410

Fax: 030-314-22943

hupost@cs.tu-berlin.de

## OFFIS - Institut für Informatik

Institut für Informatik

Escherweg 2

26121 Oldenburg

http://www.offis.de/hs

Dr. Jens-E. Appell

Tel.: 0441 / 9722-235

Fax: 9722-282

jens.appell@offis.de

## Universität Bremen

Arbeitsgruppe Rechnerarchitektur (AGRA)

Bibliothekstr. 1

28359 Bremen