## Projektspiegel

ASDESE: Application Specific Design for ESD and Substrate Effects

## Marktbeobachtung

EDA-Industrie verzeichnet im ersten Quartal 2004 ein Wachstum von 6% gegenüber dem Vorjahr.

## Veröffentlichungsanalyse der Ekompass-Projekte 2000-2003

Das Ergebnis zeigt eine große Akzeptanz der Projektbeiträge auf großen Konferenzen.

# Editorial

Liebe Leserinnen und Leser,

die ruhige Ferienzeit, so heißt es, sei gerade richtig, um insbesondere beim Forschen voranzukommen. Es gibt weniger „Störungen“ der eigenen Tätigkeit durch Anrufer und Kollegen, obwohl ja nicht mal alle gleichzeitig im Urlaub sind. Aber dennoch, oft wird nichts aus der „ruhigen Zeit“, in der man sich den Dingen widmen könnte, die sonst zu kurz kommen. Und das liegt nur daran, dass man gerade in dieser Zeit zusätzlich noch die Dinge angehen will, die neu sind, etwas Neues stimulieren oder schaffen.

So ist es auch in diesem Sommer am edacentrum. So konnte der Ihnen vorliegende Newsletter 03 2004 nicht so zügig auf den Weg gebracht werden wie es geplant war, weil auch noch andere Arbeiten anlagen. Unser Blick ist in diesem Sommer nicht nur früher als im letzten Jahr auf das edaForum (9. und 10. Dezember 2004 in Dresden) gerichtet, sondern es gilt für uns auch, die Zukunft des edacentrum zu sichern: Zum 3. Ekompass-Workshop im Mai und im letzten Newsletter haben wir auf die neuen Leistungen hingewiesen, die das edacentrum jetzt anbietet. Mit diesen Leistungen wollen wir unseren Auftraggebern einen Mehrwert bieten und uns gleichzeitig eine Einnahmequelle schaffen. Dadurch wird das edacentrum auch über den Förderzeitraum hinaus existieren können, um Ihnen weiterhin die geschätzten Dienste und Informationen bieten zu können.

Die Ihnen bisher gelieferten Fakten zu unserem Leistungsangebot sind zwar konzeptionell sorgfältig ausgearbeitet, lassen aber inhaltlich noch einige Fragen offen. Genau an dieser Stelle findet sich die Ursache dafür, dass dieser Sommer nicht so ruhig ist, wie manch einer sich vielleicht gewünscht hätte: Am edacentrum wird fleißig Material erstellt, anhand dessen wir Ihnen und allen anderen potentiellen Kunden

die geweckte Neugier befriedigen und die noch offenen Fragen beantworten wollen. Mitte September wollen wir endgültig für Ihre Fragen gerüstet sein, haben Sie bitte solange noch Geduld.

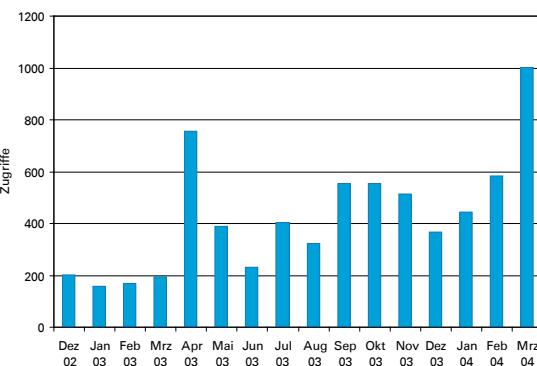

In der Zwischenzeit bieten wir Ihnen nicht nur Informationen zum edaForum, dessen Programm sie vor Kurzem erreicht haben sollte, sondern auch den vorliegenden Newsletter. Dass dieser zum ersten Mal weniger Seiten als seine Vorgängerausgabe besitzt, wird an der oben genannten Ferienzeit liegen. Die bisherige Struktur mit den fünf Rubriken und den beiden herausnehmbaren Kalendarien wurde beibehalten. Sonderrubriken sind in dieser Ausgabe einer auf die Ekompass-Projekte bezogenen Publikationsanalyse, der Umfrage zum DAC-Trendbericht 2003 und der Zugriffsstatistik des Konferenzkalenders zugeschlagen.

An dieser Stelle bedanken wir uns für die nicht selbstverständliche aber hoch willkommene Hilfe aller Autorinnen und Autoren, ohne die dieser Newsletter deutlich dünner und sicher nicht so reich an Informationen wäre.

Ihnen, liebe Leserinnen und Leser, wünschen wir abschließend eine informative und unterhaltsame Lesezeit mit diesem Newsletter und natürlich, dass Sie einen schönen Urlaub, oder wenigstens eine ruhige Ferienzeit gehabt haben!

Dipl.-Ing. Ralf Popp für das edacentrum

```

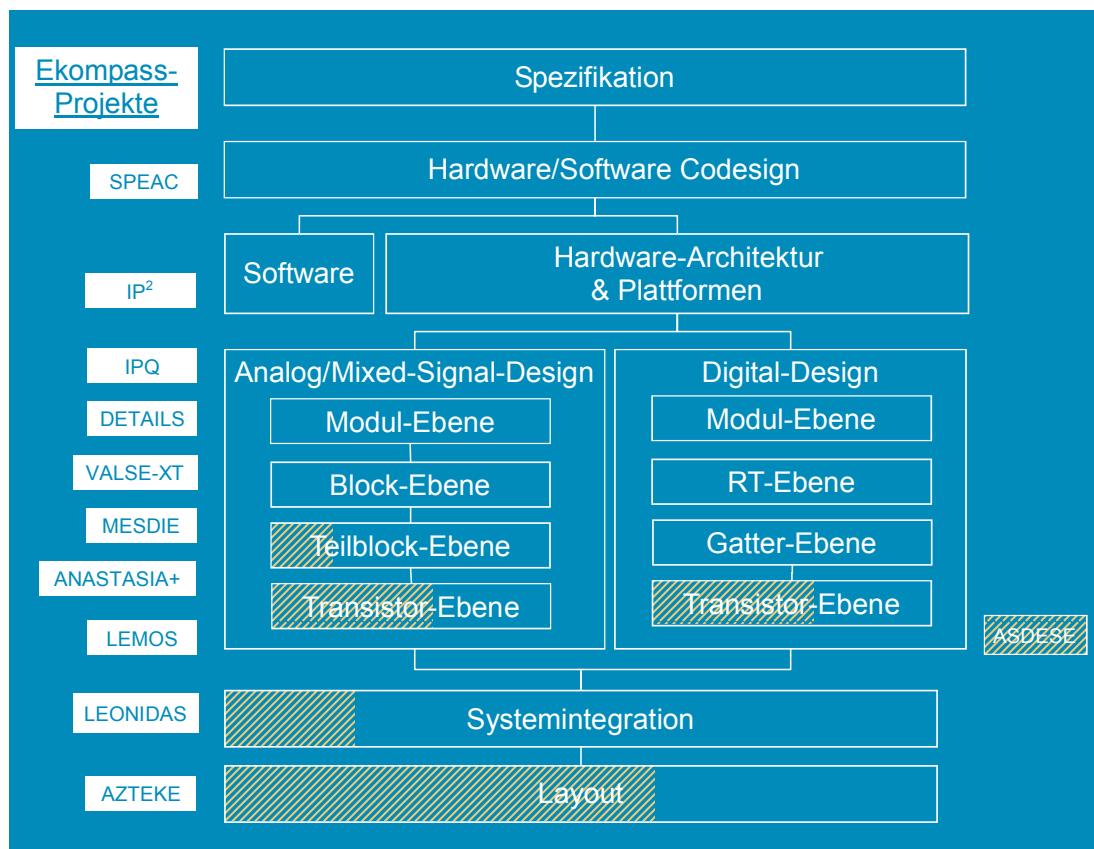

case visual_Clear_current is

when Clear =>

if (Mode = StartMeter) then

RunCount := 1;

MeterData.Bec <= 1;

visual_Clear_current <= Clear;

else

visual_Clear_current <= Clear;

end if;

when Hold =>

if (Mode = StartMeter) then

RunCount:=(RunCount+1) mod 10;

MeterData.Bec <= RunCount;

visual_Clear_current <= Run;

else

RunCount:=(RunCount+1) mod 10;

visual_Clear_current <= Hold;

end if;

```

**Vertiefende Inhalte, Ergänzungen und weiterführende Links finden Sie auf unserer mitgliederinternen Newsletterseite unter: [www.edacentrum.de/newsletter](http://www.edacentrum.de/newsletter)**

# 1

## Projektspiegel

Das BMBF hat den Förderschwerpunkt „Entwurfsplattformen für komplexe angewandte Systeme und Schaltungen“ (Ekompass) eingerichtet, um Deutschlands führende Rolle in diesem Gebiet zu festigen. Ziel ist es, durch ein gemeinsames Vorgehen von Industrie, Forschung und öffentlicher Hand, in den für Deutschland (und für Europa) wichtigen Bereichen neue Entwurfsmethoden zu entwickeln, um die Komplexität zukünftiger Chipsysteme qualitätsgerecht und effektiv beherrschen zu können. Dabei wird der Fokus auf solche Themen gelegt, denen für die Wettbewerbsfähigkeit der deutschen Industrie die größte Bedeutung zukommt.

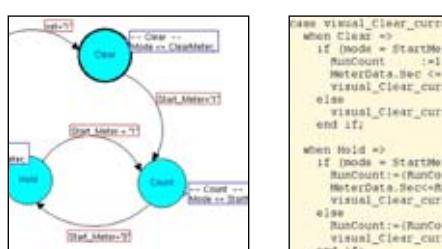

Abbildung 1:

Überblick über die Projekte

des Förderschwerpunktes

**Ekompass:** Das Bild zeigt die verschiedenen Entwurfsvorgänge beim Schaltungsentwurf und die Schwerpunkte der jeweiligen Ekompass-Projekte. Das Projekt ASDESE ist hervorgehoben, weil der Newsletter des edacentrum in loser Folge über die betreuten Projekte berichtet, und sich das Projekt ASDESE in dieser Ausgabe präsentiert.

Abbildung 1

# ASDESE: Application Specific Design for ESD and Substrate Effects

## Projektziele

Das Projekt ASDESE wurde im Rahmen der BMBF-Förderinitiative Ekompass vom März 2001 bis Juni 2003 durchgeführt. Es war durch die Notwendigkeit motiviert, die Entwicklungszeiten von integrierten Schaltungen (ICs) zu reduzieren und die robuste Funktion zukünftig zu entwickelnder ICs abzusichern. Technisches Ziel war es, simulationsgestützte Entwurfsmethoden zu entwickeln, die die Festigkeit von ICs gegen elektrostatische Entladungen (Electrostatic Discharge, ESD) absichern und Substrateffekte beherrschen lassen.

Elektrische Entladungen von oder auf ICs können während der Herstellung oder beim Kunden auftreten. Um Schäden auf den ICs durch diese Entladungen zu verhindern, müssen für jeden IC-Pin ESD-Schutzstrukturen integriert werden, die Strompulse im Ampere-Bereich in sehr kurzen Zeiten auf dem Chip sicher ableiten. Über den Schutz gegen ESD-Belastungen nach dem ‚klassischen‘ Human Body Model (HBM) hinaus zielte die Entwicklungsarbeit auf das immer wichtiger werdende ‚Charged Device Model (CDM)‘. Ziel war es, für CDM die Messtechnik auszubauen und auf physikalischer Bauelementssimulation und Schaltungssimulation basierende Entwurfsmethoden zu entwickeln.

Überkopplungen von Störungen über das Substrat von ICs können die Funktion gefährden und müssen daher beherrscht werden. Die Partner zielten darauf, Methoden zur Beschreibung der komplexen Kopplungen innerhalb des Substrats und des Substrats mit seiner Umgebung (z.B. Verdrahtung) auszubauen. Der Schwerpunkt des Interesses lag auf der Integration mehrerer Simulationswerkzeuge in eine kommerziell erhältliche Designumgebung. Darüber hinaus sollten hierarchische Methoden entwickelt werden, die komplexere Probleme in mehrere Abstraktionsebenen unterteilen. Ziel war es, den Frequenzbereich bis 40 GHz abzudecken.

Das Konsortium verifizierte die genannten Entwurfsmethoden und Werkzeuge für verschiedene Technologien (Smart-Power-, Deep-sub- $\mu$ -CMOS-, SOI-, sowie BiCMOS-, und SiGe-Prozesse für RF-Anwendungen). Für Schaltungsentwickler zielte das Projekt darauf, Entwurfshinweise zu erarbeiten. Diese ermöglichen bereits zu einem frühen Zeitpunkt des Entwurfs, wirksame Maßnahmen zu ergreifen, um teure Re-Designs zu vermeiden.

## Ergebnisse:

Das ASDESE-Projekt wurde erfolgreich abgeschlossen. Die wichtigsten Ergebnisse zum Entwurf von ESD-Schutzstrukturen sind folgende:

Zunächst wurde erstmals eine funkenfreie, und damit reproduzierbare Charakterisierungsmethode für CDM-Tester entwickelt, die für die Modellierung genutzt und in die Standardisierung eingebracht wurde. Mittels physikalischer Bauelementssimulation wiesen die Partner erstmals den großen Einfluss von bisher für CDM-ESD vernachlässigten physikalischen Effekten nach (z. B. ‚Forward Recovery‘, ‚Transient Reverse Overshoot‘). Deren Relevanz wurde auch durch Messung unter ultrakurzen Pulsen (very-fast Transmission Line Pulsing) belegt. Schaltungssimulation lieferte wichtige Erkenntnisse über Entladepfade, deren Auswirkung auf die CDM-Festigkeit, und sie führte zu Entwurfshinweisen. Vorgehensweise und Anwendungsbeispiele werden weiter unten beschrieben.

Zur Beherrschung von Substratkopplungen erzielte das Projekt folgende zentrale Ergebnisse:

Die Partner integrierten Substratsimulatoren mit unterschiedlichen Anwendungsprofilen (hohe Komponentenzahl, mittlere Genauigkeit oder hohe Genauigkeit für RF bei beschränkter Komponentenzahl) in eine gemeinsame Entwurfsumgebung (Cadence). Anwendungsbeispiele belegen eindrucksvoll das Potential der Simulationswerkzeuge bis hin zu sehr hohen Frequenzen. Unten wird über eine Studie an einem 30 Gbit/s Transimpedanzverstärker berichtet. Darüber hinaus entwickelten die Partner eine Methode, die eine - bisher nicht existierende - hierarchische Behandlung von Substratkopplungen erlaubt.

Die Partner veröffentlichten während des ASDES Projekts zum Teil gemeinsam mehr als 20 Beiträge zu Konferenzen und Workshops sowie Artikel in Fachzeitschriften. Darunter befanden sich auch einige eingeladene Beiträge, die das Interesse an den Ergebnissen des Asdese Projektes belegen.

## Arbeitspaket 1, ESD

In diesem Arbeitspaket lag der Schwerpunkt der Arbeiten auf dem immer wichtiger werdenden CDM-Belastungs-Modell. Mit diesem Modell wird die Entlade-Festigkeit von ICs getestet, nachdem diese selbst elektrostatisch aufgeladen worden sind. Es bildet damit realistische Bedingungen nach, wie sie z. B. in der Fertigung oder bei der Montage durch

## Zusammensetzung des Projektkonsortiums

### Partner:

- » Atmel Germany GmbH

- » Cadence Design Systems GmbH

- » Infineon Technologies AG

- » Philips Semiconductors GmbH

- » Robert Bosch GmbH

- » X-Fab Semiconductor Foundries

### Unterauftragnehmer:

- » Fraunhofer Gesellschaft IZM

- » Fachhochschule Osnabrück

- » Universität Hannover

- » Ruhr-Universität Bochum

- » IMMS gGmbH

- » Melexis GmbH

### Förderkennzeichen:

01 M 3053

### Laufzeit des Vorhabens:

01.03.2001 bis 30.06.2003

### Schlüsselworte:

Charged-Device-Model, Deep-Sub-Micron, ESD, High-Frequency Processes, Human-Body-Model, Silicon-On-Insulator, Smart Power, Substrateffekte

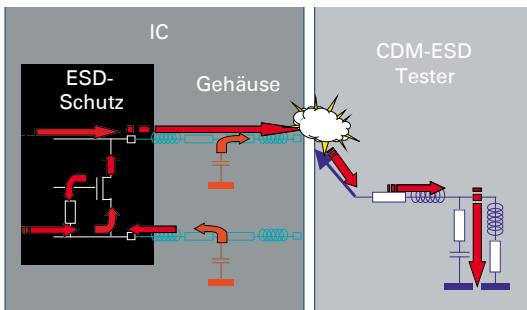

Reibungselektrizität oder Influenz auftreten können. Die Partner entwickelten neue Methoden in der ESD-Charakterisierung und bauten physikalische Baulementssimulation und Schaltungssimulation im CDM-relevanten Zeitbereich aus. Zunächst konzentrierte sich die Charakterisierung auf funkenfreie, und damit sicher reproduzierbare HF-Messungen der CDM-Testercharakteristik, um aus diesen Daten ein Ersatzschaltbild zu extrahieren. Dieses Ersatzschaltbild bildete eine wichtige Grundlage für die Simulation. Weiterhin wurden Charakterisierungsmethoden wie ‚very-fast‘ Transmission-Line-Pulsing und das optische Rasterverfahren ausgebaut, um das transiente Verhalten aktiver Bauelemente zu erfassen. Die von den Partnern gemeinsam entwickelte Simulationsmethodik ist in **Abbildung 2** dargestellt.

Abbildung 2

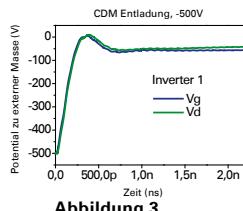

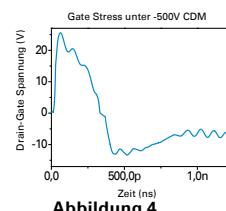

Die beim CDM-Test auf dem IC gespeicherte Ladung fließt im Moment der Entladung in extrem kurzer Zeit ( $\sim 1$  ns) über aktive Bauelemente auf dem Chip. Die hohen Ströme ( $\sim 5\text{--}10$  A) erzeugen lokale Spannungsabfälle, die zu bewerten sind. Ein hinreichend funktionierender ESD-Schutz sollte diese Ströme so niederohmig ableiten, dass keine gefährlichen Überspannungen an den integrierten Bauelementen entstehen. Die bereits genannten, unter CDM relevanten, bisher nicht beachteten physikalischen Effekte konnten mittels physikalischer Baulementssimulation aufgedeckt werden. Sie wurden an Messungen verifiziert und in Modelle für die Schaltkreissimulation eingebunden. Das Vorgehen bei der Auswertung der Simulation ist in **Abbildung 3** für den NMOS-Transistor in einem Inverter dargestellt. Bei einer CDM-Entladung steigt das Potenzial aller Knoten in extrem kurzer Zeit (sub-Nanosekunden-Bereich) vom Wert der Vorladespannung (hier  $-500$  V) auf nahezu Testermasse an. Geringfügige Phasenverschiebungen führen zu lokalen Spannungsüberhöhungen, die empfindliche Anschlüsse integrierter Bauelemente (z.B. Gates) zerstören können. Es treten, wie in **Abbildung 4** gezeigt, kurzzeitig Spannungswerte von über 20 V zwischen Drain und Gate auf. Solche Überspannungen können dann, in Abhängigkeit von Technologie und Bauelementtyp, auf Risiko von Drift oder Total-

Abbildung 3

Abbildung 4

ausfall bewertet werden. Damit erlaubt die Simulation die Optimierung des Einsatzes von Schutzstrukturen, bevor Silizium gefertigt werden muss.

Die Partner verifizierten die Simulationsergebnisse erfolgreich durch Messungen an Teststrukturen. Eines der wichtigsten Ergebnisse für die Partner ist das neu gewonnene Verständnis für die halbleiterphysikalischen Effekte, die unter CDM-ESD zusätzlich wichtig werden. Dieses Verständnis floss direkt in Entwurfs hinweise ein, die für die Entwicklung neuer ICs genutzt werden. Auch die einzelnen Komponenten der in ASDESE entwickelten Design-Unterstützung werden für neue Technologien genutzt. Dies sind die erfolgreich entwickelten CDM-Teststrukturen, das neue CDM-Tester-Modell, sowie die ESD-Simulation. Die Methode der funkenfreien CDM-Tester-Charakterisierung wurde in die Standardisierung (ESD Association, Working Group 5.2) eingebracht. Die Partner veröffentlichten eine Reihe wissenschaftlicher Artikel, u. a. im Rahmen weltweit angesehener Fachkonferenzen.

### Arbeitspaket 2, Substrat-Effekte

Unerwünschte Kopplungen über das Substrat gefährden die Funktion von ICs im Analog- und Mixed-Signal-Entwurf. So können z. B. schaltende Endstufen über Fluktuationen des Substratpotentials in unerwünschter Weise auf hochohmige analoge Eingänge zurückkopeln. Diese Substrateffekte müssen bereits im Entwurf beherrscht werden, um Redesigns zu vermeiden. Das Arbeitspaket 2 zielte darauf, Substratsimulations-Werkzeuge mit unterschiedlichen Stärken in eine einheitliche Entwurfsumgebung zu integrieren. Weiterhin demonstrierten die Partner Anwendungen bis hin zu sehr hohen Frequenzen und haben neue Ansätze für die hierarchische Behandlung von Überkopplungen im Substrat entworfen.

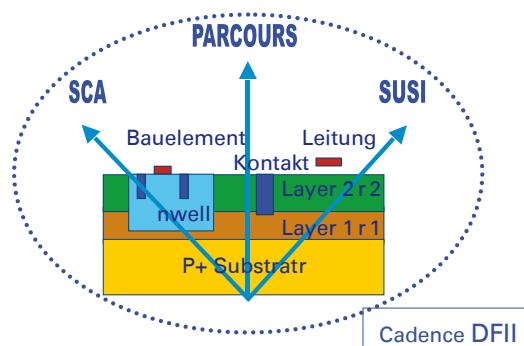

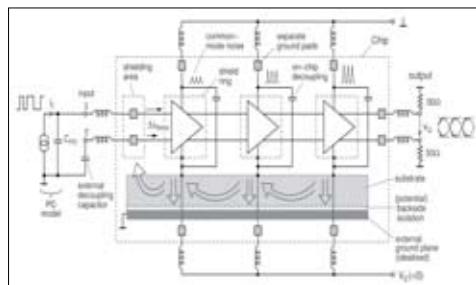

Die Integration von Substratsimulatoren mit unterschiedlichen Anwendungsprofilen (große Anzahl von Bauelementen, wählbarer Vereinfachungsgrad oder hohe Genauigkeit bei eingeschränkter Anzahl der Bauelemente) ist in **Abbildung 5** dargestellt. Im Ein-

Abbildung 5

zelnen wurden die zu Beginn des ASDESE-Projekts unabhängigen Substratsimulatoren SCA (Cadence), PARCOURS (Philips/Universität Hannover) und SUSI (Atmel, Universität Bochum) in die DFII Designumgebung von Cadence integriert. In dieser Entwurf-

Abbildung 2:

Schematische Darstellung der in ASDESE entwickelten Methode zur Simulation von CDM-ESD. Das IC (links) umfasst den Chip mit ESD-Schutz (links, schwarzer Hintergrund) und dem Gehäuse (R, L, C Ersatzschaltbild in grün). Kapazitäten der Strukturen auf dem Chip und der Gehäusepins werden auf die CDM-Vorladespannung geladen. Die gespeicherte Ladung (rot) fließt über aktive Bauelemente und den Entladepin (R, L, C Ersatzschaltbild in grün, oben) hin zum CDM-ESD-Tester (rechts). Der Tester ist durch das in ASDESE neu entwickelte Ersatzschaltbild dargestellt (blau).

Abbildung 3:

CDM-Entladung eines NMOS-Transistors in einem Inverter als Funktion der Zeit, Vorladespannung  $-500$  V. Simulation des Potentials von Gate (V<sub>g</sub>) und Drain (V<sub>d</sub>) gegenüber der externen Masse (Tester-Masse).

Abbildung 4:

Lokale Spannungsdifferenz V<sub>d</sub>-V<sub>g</sub> am NMOS unter Bedingungen wie in Abbildung 3, jedoch mit höher aufgelöster Spannungs- und Zeitskala.

Abbildung 5:

Schematische Darstellung der Integration unterschiedlicher Substratsimulatoren.

Im Zentrum ist, stellvertretend für das zu simulierende Substrat, ein vereinfachter Querschnitt eines Substratausschnitts mit einem Bauelement, einem Kontakt und einer Leitung dargestellt.

sumgebung wurden sie genutzt, um Hinweise zur Vermeidung von Substratkopplungen abzuleiten, die gegenüber Teststrukturen verifiziert worden sind.

Als Anwendung bei hohen Frequenzen wurde die Substratkopplung in einem 30 Gbit/s Transimpedanzverstärker untersucht. Das Blockschaltbild ist in **Abbildung 6** dargestellt.

**Abbildung 6:**

Vereinfachtes Blockschaltbild des Transimpedanzverstärkers. Das Substrat ist grau hinterlegt. Die Rückwirkung über das Substrat auf den Eingang ist durch Pfeile angedeutet.

**Abbildung 6**

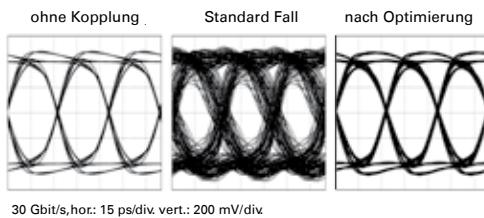

Für RF-Anwendungen ist der Simulator SUSI besonders geeignet. Daher wurde er für diese Anwendung genutzt, um Rückkopplungen über das Substrat zu untersuchen. Hierfür wurde der Verstärker durch eine (zufällige) 30 Gbit/s Wortsequenz am Eingang getrieben. Versorgungs- und Masseleitungen der drei Verstärkerstufen koppeln kapazitiv oder direkt an das Substrat. Das Substrat koppelt die resultierenden Störungen zurück an den Eingang. Ein Maß für die Störungen ist die Qualität des „Augen“-Diagramms des Ausgangs. Dies ist in **Abbildung 7** für drei verschiedene Fälle dargestellt

**Abbildung 7:**

Simuliertes „Augen“-Diagramm des Ausgangs des Verstärkers aus Abbildung 6.

**Links:** ohne Berücksichtigung von Substratkopplung,

**Mitte:** mit Substratkopplung, vor Optimierung,

**Rechts:** mit Substratkopplung nach Optimierung

**„Augen“-Diagramme**

**Abbildung 7**

Der Entwurf wurde durch mehrere Maßnahmen verbessert. Dies waren z. B. eine gute Anbindung der Rückseite an die externe Masse, Vermeiden von Channel-Stopper und Minimierung parasitärer (Bonddraht) Induktivitäten. Die Wirksamkeit der Optimierung wird eindrucksvoll durch die enorme Verbesserung des Ausgangs-, „Augen“-Diagramms (Fig. 6, rechts gegenüber Mitte) belegt.

Zwischenzeitlich haben die beteiligten Partner die Substrat-Analyse Werkzeuge in ihre Entwurfsumgebung eingebunden. Ein erprobter simulationsgestützter Entwurfsablauf steht zur Verfügung. Die Partner nutzen die Hinweise, um Substratkopplungen bereits im Entwurf zu berücksichtigen und zu beherrschen. Cadence bietet das Framework für die Substratsimulationswerkzeuge in Ergänzung zu seinen Standardlösungen auf Anfrage kommerziell an (als sogenanntes VCAD-IP Modell).

Für den Cadence Standort München war das ASDESE-Projekt darüber hinaus eine wichtige Basis, um in dieser Technologie-nahen, kundenspezifischen Thematik Support und Entwicklung zu stärken, sowie weitere Kunden für die neuen Werkzeuge zu gewinnen.

## Berichte von den Partnern

### » Robert Bosch GmbH

Bosch nutzt die Ergebnisse des ASDESE Projekts schwerpunktmäßig, um seine ICs für Anwendungen in der Automobilelektronik gegen CDM-ESD zu härten. Die für Kraftfahrzeugeanwendungen spezifischen Anforderungen, wie z.B. Verpolfestigkeit, erfordern Technologien (Smart Power) und Gehäuse (z.B. mit Rückseitenmetallisierung), die zu einem unerwarteten Verhalten unter CDM führen könnten. So konnte mittels der in ASDESE erarbeiteten Methoden aufgedeckt werden, warum entscheidende Komponenten zum CDM-Schutz von IC-Eingängen für die von Bosch genutzten Technologien ein ungewöhnliches Skalierungsverhalten zeigen. Als zusätzlicher Schutz wird zwischen Pad und Eingang, neben einem aktiven ESD-Element, ein diffundierter Widerstand eingefügt. Mittels physikalischer Bauelementssimulation und Schaltungssimulation in Kombination mit Substratsimulation konnte erstmals detailliert erklärt werden, warum die CDM-Festigkeit solcher Eingangsschutzstrukturen mit zunehmendem Widerstandswert nicht, wie eigentlich erwartet, durchgängig zunimmt. Der Grund sind parasitäre Anteile der Widerstandswanne, die durch Ladungen aus dem Substrat gespeist werden. Es ist geplant, eine Studie dieses Phänomens auf der ESD/EOS Konferenz 2004 zu veröffentlichen.

### » Infineon Technologies AG

Schutz vor „CDM-ähnlichen“ Entladungen sind für praktisch alle integrierten Schaltungen in den typischen Anwendungsbereichen bei Infineon von großer Bedeutung. In ASDESE wurde die Grundlage geschaffen, durch Messungen, Bauelementesimulation und Schaltkreissimulation Entwurfshinweise für CDM-robustes IC-Design zu definieren. Dazu wurde gemeinsam mit den Partnern in ASDESE ein Satz von geeigneten Teststrukturen entwickelt, die in einer 0.13-µm-CMOS-Technologie prozessiert und mit verschiedenen experimentellen Methoden charakterisiert wurden. TCAD- und Schaltungssimulation dieser Teststrukturen führten zu einem grundlegenden Verständnis der physikalischen Vorgänge in Bauelementen und einfachen Schaltungsblöcken (z. B. Eingangsstufen) in einer modernen deep-sub-µ-CMOS-Technologie während einer schnellen elektrostatischen Entladung. Aus den Messungen und Simulationen konnten beispielsweise die schädliche Rolle von parasitären Widerständen im Entladepfad auf die CDM-Festigkeit nachgewiesen werden; als wichtiger Entwurfshinweis für das Design und Layout von I/O-Strukturen konnte somit ein maximal zulässiger Höchstwert für Leiterbahnwiderstände abgeleitet werden. Diese Ergebnisse

wurden in die ESD-Entwurfsrichtlinien für die 0.13-µm- und die 90-nm-CMOS-Technologie aufgenommen.

In vielen Anwendungsbereichen von Infineon ist die Vermeidung von unerwünschten Substratkopplungen in empfindliche Schaltungsteile wesentlich für die Realisierung der integrierten Schaltungen. In ASDESE wurde ein Substratanalyse-Werkzeug bereitgestellt, das im Entwurfsablauf von den Schaltungsentwicklern einfach benutzt werden kann. Dieser Punkt wurde in enger Zusammenarbeit mit den Partnern erarbeitet. Mit einem Testchip wurde das Übersprechen von HF-spezifischen Schaltungselementen in einer BiCMOS-Technologie untersucht und das Substratanalyse-Werkzeugs verifiziert. Ein neues Konzept, das eine Abstraktion bzw. eine vereinfachte Beschreibung für das Substrat zulässt, wurde erarbeitet. Außerdem kann das wichtige Thema „Wiederverwendung von Teilblöcken“, die hinsichtlich des Substratübersprechens optimiert sind, mit diesem neuen Konzept realisiert werden. Es ist geplant, die Substratanalyse in einer nächsten Release des Infineon Full-Custom Design-Flows anzubieten und somit Infineon-weit zur Verfügung zu stellen.

#### » Philips Semiconductors GmbH

In Deep Submicron (DSM) Technologien spielen die Verkopplungen von Bauelementen über das gemeinsame Substrat eine immer stärker werdende Rolle. Insbesondere für die Designer von Hochfrequenz (HF) Schaltungen in Mixed-Signal Prozessen ist das Problem des Übersprechens der hochaktiven digitalen Schaltungsblöcke auf die sensiblen analogen Bereiche über das gemeinsame Substrat eine große Herausforderung. Abschirmmaßnahmen gegen solche unerwünschten Substrateinflüsse, wie z.B. das Einfügen zusätzlicher Substratkontakte, konnten bisher mit bestehenden Simulationswerkzeugen nicht nachvollzogen werden. Eine Modellierung des Substratbereichs war nicht in ausreichendem Maße möglich. Daher ist es das Ziel dieses Beitrags gewesen, dem Entwickler Hilfestellungen, Designhinweise und ein entsprechendes Werkzeug an die Hand zu geben, das eine Extraktion und Modellierung des Substratbereichs in seiner vertrauten Designumgebung erlaubt. Das in ASDESE weiterentwickelte Werkzeug PARCOURS (PARasitic COUpling model geneRator for Substrate) ermöglicht nun die Berücksichtigung von Substratkontakten, ist in das Design Framework einbindbar und erlaubt durch seine grafische Darstellung der Substratstörungen eine Optimierung des Schaltungsentwurfs bereits vor der Erstellung der Hardware. Dies hat bereits dazu geführt, dass auf der Basis der mit PARCOURS erzielten Ergebnisse das Redesign einer aktuellen Schaltung vermieden werden konnte. Damit leisten die Ergebnisse dieser Arbeiten auch einen wichtigen Beitrag dazu, dass die großen technologischen Anforderungen moderner Sub-100nm Prozesse überhaupt erfüllt werden können.

#### » Atmel Germany GmbH

Die im ASDESE-Projekt erarbeiteten Ergebnisse tragen wesentlich zum tieferen Verständnis des Bauelementverhaltens für neue Smart-Power Technologien auf SOI-Material bei. Auf diesem Wege konnten mit wesentlich geringerem finanziellem und personellem Aufwand geeignete ESD-Schutzstrukturen und -konzepte entwickelt werden. Darüber hinaus konnten grundsätzliche Testverfahren im Einvernehmen mit allen Partnern definiert werden, um eine deutlich bessere Vergleichbarkeit der Charakterisierung des ESD-Schutzes zu erreichen. Darauf aufbauend wurden allgemeine ESD-Richtlinien erarbeitet, mit deren Hilfe ein geeigneter ESD-Schutz für neue Produkte schneller und zuverlässiger entwickelt werden kann. Mit den ermittelten Modellparametern für den Device Simulator steht weiterhin ein Werkzeug zur Verfügung, mit dem auch für die zukünftigen Technologiegenerationen der SOI-Smart-Power-Familie eine effektive Basis zur Entwicklung optimaler ESD-Schutzelemente aufgebaut werden konnte. Damit wird die Entwicklungszeit dieser Technologien deutlich reduziert.

Des Weiteren konnten durch die Projektarbeiten verschiedene Maßnahmen gegen das Auftreten von Substrateneffekten in HF-Schaltungen ergriffen werden. Die Einführung des Substratsimulators SCA in den Designflow, sowie die Einrichtung von SUSI als Referenzwerkzeug zur genaueren Analyse von Substrateneffekten, führten zu einer spürbaren Reduzierung von Redesigns. Im Fokus der Arbeiten stand hierbei besonders die Einflussanalyse von Bond-Induktivitäten auf Substratkopplungen und die Gewinnung erweiterter Substratmodelle. Mittels daraus abgeleiteter Richtlinien sind Schaltungsentwickler jetzt in der Lage, Substratverkopplungen gezielt zu minimieren. Während bei HF-Schaltungen die Erfolge der Substratanalyse zu einer Verminderung der Redesigns führen, scheitert bei Mixed-Signal-Schaltungen eine genauere Substratanalyse oft an der Komplexität der Designs. Hier soll in Zukunft eine hierarchische Analyse, die durch Arbeiten in diesem Projekt vorbereitet wurde, Abhilfe schaffen. Auf diese Weise sollen in Zukunft auch große Designs von der Substratanalyse profitieren.

#### » X-FAB AG

Die Ergebnisse des ASDESE Projektes werden von X-FAB zur Optimierung des ESD-Schutzes in den X-FAB Design Kits verwendet. Innerhalb des Projektes wurde erstmals systematisch das ESD-Verhalten von DMOS-Transistoren in der 0.8µm Hochvolt-CMOS-Technologie von X-FAB untersucht. Das ESD-Verhalten der verschiedenen DMOS-Transistoren und der aktiven Schutzschaltungen, die solche DMOS-Transistoren verwenden, konnte mittels Bauelemente- und Schaltungssimulation erklärt werden. Kompaktmodelle für die Elemente einer aktiven ESD-Schutzschaltung wurden in die Cadence-Affirma-Simulationsumgebung integriert. Damit konnte erstmalig die TLP-Belastung einer aktiven ESD-Schutzschaltung in der 0.8

um HV-CMOS-Technologie von X-FAB innerhalb der Cadence-Entwicklungsumgebung simuliert werden. Es ist geplant ESD-Modelle zur Durchführung von ESD-Simulationen von ESD-Schutzschaltungen in Design Kits von X-FAB zu integrieren.

#### » Cadence

Zur Adressierung von technologienahen Themen wie Substratkopplungsanalyse ist eine Zusammenarbeit zwischen Softwareherstellern und Halbleiterherstellern unabdingbar. Durch das enge Zusammenwirken des Projekt-Konsortiums konnten wesentliche Erkenntnisse gewonnen werden, die von Cadence Design Systems Deutschland genutzt werden. Der Schwerpunkt dieser Ergebnisse liegt bei der Validierung vorhandener Werkzeuge, deren korrekter Einbindung in den Design-Flow und bei der Weiterentwicklung neuer Produkte. Durch die von den Projektpartnern gefertigten und vermessenen Testschaltungen konnte ein direkter Vergleich zwischen Realität und Simulation gezogen werden, der eine Validierung der Produkte, der Anbindung an den Entwurfsflow und der zugrundeliegenden Methodik ermöglicht. Eine solche Zusammenarbeit von verschiedenen Halbleiterfirmen mit einem Softwarehersteller und verschiedenen Universitäten wäre ohne ein Verbundprojekt wie ASDESE sicherlich nicht zustande gekommen. Als konkretes Beispiel ist hier die Erkenntnis über den Gehäuseeinfluss auf die Substratverkopplung zu nennen, die z.B. bei den Untersuchungen zum Transimpedanzverstärker (siehe

**Abbildung 5**) gewonnen wurde. Die erarbeiteten Methoden, gewonnenen Erfahrungen und Anforderungen der Projektpartner zu Substratanalyse-Werkzeuge fließen in die aktuellen Entwicklungen einer neuen Lösung von Cadence ein, dem Substrate Noise Analyzer (SNA), der auf den bestehenden Lösungen (SCA, Seismic und SubstrateStorm) basiert. Dabei konnte sich die deutsche Niederlassung durch das in ASDESE gewonnene Know-how und die guten Kontakte zu den Projektpartnern aus der Industrie (Anwender) aktiv in der Spezifikations- und Evaluierungsphase etablieren.

#### Ausblick und Perspektiven

Das ASDESE-Projekt hat mit ESD und Substrateffekten zwei technologienahen Themenfelder bearbeitet. Für die zukünftige Technologieentwicklung erwarten wir eine unvermindert fortschreitende Miniaturisierung integrierter Bauelemente mit weiter zunehmender Systemintegration auf ICs. Damit werden die Strukturen immer empfindlicher. Daher hat das Projekt Know-how von strategischer Bedeutung für den Entwurf zuverlässiger ICs erarbeitet. Dessen Bedeutung wird in Zukunft noch weiter zunehmen. Das ASDESE-Projekt hat erstmals eine fundierte, halbleiterphysikalische Simulation des CDM-ESD-Verhaltens von Bauelementen ermöglicht. Ein in Zukunft wichtiger innovativer Schritt wird die Absicherung des Gesamt-ESD-Schutzes auf Chip-Ebene sein. Die Ergebnisse des ASDESE-Projekts bilden die notwendige Basis, um diese technisch enorm komplexe Fragestellung angehen zu können.

#### Kontakt:

Wolfgang Wilkening

Robert Bosch GmbH

AE/DIC1

PO. Box 13 42

72703 Reutlingen

fon: 07121 35 1533

FAX: 07121 35 37 1533

wolfgang.wilkening2@de.bosch.com

Weitere Informationen sind unter [www.edacentrum.de/ekompass/projekte/asdese.html](http://www.edacentrum.de/ekompass/projekte/asdese.html) zu finden.

## Veröffentlichungsanalyse der Ekompass 2000 - 2003

[www.edacentrum.de/newsletter](http://www.edacentrum.de/newsletter)

Um eine Übersicht über die wissenschaftlichen Arbeiten und deren Ergebnisse im Ekompass-Programm zu erhalten, hat das edacentrum Ende letzten Jahres damit begonnen, die Veröffentlichungen der Ekompass-Projekte für den Zeitraum 2000 bis 2003 zu erfassen. In den folgenden Abschnitten präsentieren wir Ihnen das Ergebnis dieser Arbeit. Zuvor möchten wir uns an dieser Stelle bei den Projektleitern und deren Mitarbeitern für die tatkräftige Unterstützung bedanken, die die hier beschriebene Analyse der Projektveröffentlichungen erst möglich gemacht hat. Ihnen allen vielen Dank!

#### Vorüberlegungen

Der Umgang mit Daten und deren Auswertung ist eine kritische Angelegenheit. Wir haben uns bemüht, den meisten Fallstricken auszuweichen, aber eine gewisse Unsicherheit besteht aus folgenden Gründen:

#### » Erfassung der Daten

Wir haben mit allen Projektleitern eng zusammengearbeitet, um die Veröffentlichungen der Projekte möglichst vollständig zu erfassen. Da eine solche Aktion zum ersten Mal durchgeführt wurde, gab es keine einheitliche Meinung darüber, welche Veröffentlichungen als nennenswert zu beurteilen sind. Auch mussten wir zunächst Erfahrungen sammeln, auf welchen Veranstaltungen und in welchen Medien die Projekte ihre Ergebnisse präsentieren. Die unterschiedliche Beurteilung von Veröffentlichungen bezog sich vor allem auf Veranstaltungen wie nationale Workshops oder Kolloquien. Wir haben an den Stellen nachgehakt, an denen uns Unterschiede auffielen, und uns bemüht, den Projekten durch Rückmeldungen einen Überblick zu geben. Eine Garantie für die Vollständigkeit können wir allerdings nicht geben.

Bei Ekompass-Projekten, die in einem europäischen MEDEA+-Projekt eingebettet sind, wurden nur die Veröffentlichungen berücksichtigt, an denen deutsche Partner beteiligt waren. Die auf der Grundlage von Projektarbeiten entstandenen Dissertationen und Habilitationen wurden miterfasst, Studien- und Diplomarbeiten hingegen wurden nicht aufgenommen.

#### » Kategorisierung der Daten

Die Anzahl der Veröffentlichungen eines Projektes ist an sich nicht aussagekräftig. Interessant wird es, wenn der Schwerpunkt deutlich wird, den ein Projekt für seine Veröffentlichungen wählt. Macht es z.B. bei der Wahl der Konferenzen tatsächlich etwas aus, ob ein Projekt mehr oder weniger technologie-lastig ist? Die Antwort darauf hängt nicht nur von den Veröffentlichungen ab, sondern auch davon, wie diese kategorisiert werden. Wir haben 9 Kategorien festgelegt:

- Hauptkonferenzen: DATE, DAC, ASP-DAC, EMC, ITC, ICCAD, ISCAS

- Konferenzen: z.B. FDL, FPL

- Workshops, international: z.B. IEEE Workshops

- Workshops, national: z.B. ANALOG, E.I.S.

- Kolloquien, international: z.B. South European Test Seminar

- Kolloquien, national: z.B. Fachworkshops, Ekompass

- Journale, Magazine: z.B. IEEE Transaction on ...

- Bücher

- Dissertationen und Habilitationen

Die Kategorie „Dissertationen und Habilitationen“ muss mit Vorsicht bewertet werden, da die Laufzeit dieser Arbeiten oft länger ist als die der Projekte, der Ausgangspunkt aber oft in den Projektarbeiten liegt.

#### » Analyse der Daten

Die Analyse der Daten war der bei weitem kniffligste Teil. Die Ekompass-Projekte haben nicht die gleiche Anzahl und das gleiche Verhältnis von Projektpartnern und Unterauftragnehmern. Das Projektvolumen ist unterschiedlich. Der Erfassungszeitpunkt der Veröffentlichungen kam für die Projekte nicht in der jeweils gleichen Projektphase: Es gab Projekte, die bereits abgeschlossen waren, und solche, die erst vor einem Jahr bewilligt wurden. Außerdem ist zu bedenken, dass in der ersten Hälfte der Projektlaufzeit mit weniger Veröffentlichungen zu rechnen ist als in der Schlussphase. Wir haben die Daten daher auf die bis 2003 abgerufenen Personenjahre bezogen. Dabei haben wir auf die Daten der Vorhabenbeschreibungen zurückgegriffen, d.h. hier ist mit einer Differenz zum tatsächlichen Abruf zu rechnen. Auch wurde keine Unterscheidung getroffen zwischen den Personenjahren in der Industrie und denen in der Forschung.

#### Ergebnisse

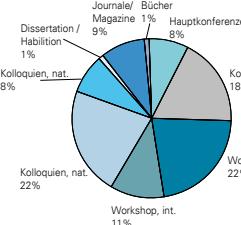

In absoluten Zahlen veröffentlichten die 13 Projekte Anastasia+ (I/II), Asdese, Azteke, HG-DAT, IP2, IPQ, Leonidas, MESDIE, Speak/SpeAC und Valse/Valse-XT in dem Zeitraum 2000 bis 2003 zusammen 452 Beiträge. Von diesen Projekten waren bis 2003 sieben Projekte abgeschlossen: Anastasia+ (I), Asdese, HG-DAT, IPO, Leonidas, Speak und Valse, die zusammen 320 der 452 Beiträge lieferten.

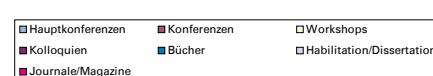

Die **Abbildung 8** zeigt die Verteilung der erfassten Veröffentlichungen auf die 9 Kategorien.

**Abbildung 8**

Es entfallen 8% auf die Hauptkonferenzen und 9% auf Journale und Magazine. Auf die Kategorien Konferenzen, nationale Workshops und nationale Kolloquien entfallen jeweils etwa 20%, auf internationalen Workshops und Kolloquien entfallen 11 %, während der Rest sich auf Dissertationen und Bücher verteilt.

Ein genauerer Blick auf die Veröffentlichungen auf den Hauptkonferenzen (**Abbildung 9**) zeigt, dass die von nahezu allen Projekten bevorzugte Konferenz die DATE mit 41% ist. Auf die Projekte umgerechnet bedeutet das, dass im Schnitt von jedem Projekt 3% der Veröffentlichungen dort erscheinen.

Berücksichtigt man nur die bereits abgeschlossenen Projekte, erschienen sogar 4% der Veröffentlichungen auf der DATE. Bei der EMC, auf der mit 30% auch ein hoher Anteil veröffentlicht wird, liegt der Fall etwas anders. Auf dieser Konferenz wird, entsprechend ihrer

**Abbildung 9**

Thematik, nur von technologienahen Projekten wie MESDIE und ASDESE veröffentlicht.

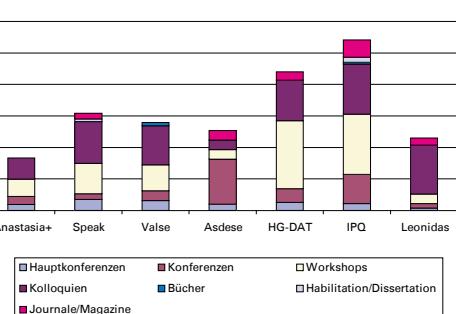

In **Abbildung 10** ist dargestellt, wie sich die Veröffentlichungen nach Kategorien auf die einzelnen Projekte aufteilen. Auf der x-Achse sind die abgeschlossenen Ekompass-Projekte aufgeführt. Die Werte auf der y-Achse entsprechen der Zahl der Projektveröffentlichungen bezogen auf die Gesamtzahl der Personenjahre im Projekt. Aus Gründen der Übersicht wurden

**Abbildung 8:** zeigt die Verteilung der erfassten Veröffentlichungen auf die 9 Kategorien.

**Abbildung 9:** Verteilung der Veröffentlichungen aller Ekompass-Projekte auf die Hauptkonferenzen.

**Abbildung 10:** Veröffentlichungen der bis 2003 abgeschlossenen Ekompass-Projekte (bezogen auf die Personenjahre).

**Abbildung 10**

einige Kategorien, wie z.B. nationale und internationale Workshops, zusammengefasst.

### Ergebnisse zu den abgeschlossenen Projekten

Die folgenden Ausführungen beziehen sich nur auf die bis 2003 bereits abgeschlossenen Projekte.

Die Projekte veröffentlichten im Durchschnitt 7% ihrer Arbeiten auf Hauptkonferenzen; der höchste Prozentsatz an Publikationen, der von einem Projekt auf Hauptkonferenzen veröffentlicht wurde, liegt bei 11% und zwar bei den Projekten Anastasia+, Speak und Valse. Pro Jahr wurden von den Projekten im Schnitt 20 Publikationen veröffentlicht. Dies bedeutet umgerechnet auf die Gesamtanzahl der Personenjahre, dass für die Arbeiten, die in einer Veröffentlichung präsentiert werden, im Schnitt 1,6 Personenjahre aufgewendet wurden. Der niedrigste Aufwand lag dabei bei knapp einem Personenjahr, der höchste bei 3 Personenjahren. Dabei bleibt unberücksichtigt, dass in dieser Zeit nicht nur an dem gearbeitet wird, was sich später in einer Veröffentlichung niederschlägt. Zum Beispiel werden in Projekten auch Arbeiten durchgeführt, deren Ergebnisse aus Geheimhaltungsgründen nicht veröffentlicht werden können, z.B. wenn zu diesen Arbeiten Patente angemeldet werden sollen.

Abbildung 11:

Veröffentlichungen der bis 2003 abgeschlossenen Ekopass-Projekte (bezogen auf die Personenjahre), ohne Kolloquien.

Abbildung 11

Abbildung 12:

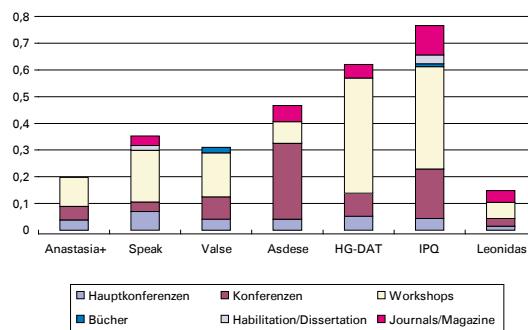

Veröffentlichungen der zurzeit laufenden Ekopass-Projekte (bezogen auf die Personenjahre).

**Tabelle 1:** Verhältnis zwischen Anzahl der Industriepartner (IP) und der Anzahl der Forschungspartner (FP) in den Projekten.

In **Abbildung 11** sind noch einmal die Veröffentlichungen der Projekte nach Kategorien dargestellt, nur wurden die Ergebnisse jetzt konzentriert und Kolloquien nicht berücksichtigt. Interessant ist es in diesem Zusammenhang, sich das Verhältnis zwischen der Anzahl der Industriepartner (IP) und der Anzahl der Forschungspartner (FP) in den einzelnen Projekten vor Augen zu führen (**Tabelle 1**).

| IP zu FP (in %) | Projekt                              |

|-----------------|--------------------------------------|

| 60 zu 40        | Anastasia+, Asdese, HG-DAT, Leonidas |

| 50 zu 50        | IPQ, Speak                           |

| 40 zu 60        | Valse                                |

Tabelle 1

IP zu FP

(in %) Projekt

60 zu 40 Anastasia+, Asdese, HG-DAT, Leonidas

50 zu 50 IPQ, Speak

40 zu 60 Valse

Vor der Analyse bestand am edacentrum die Vermutung, dass eine höhere Anzahl von Projektteilnehmern aus der Forschung zu einer höheren Anzahl von Projektveröffentlichungen führt – vor allem bei den Hauptkonferenzen. Diese Vermutung wird jedoch durch die Analyse nicht bestätigt. Unter Berücksichtigung der pro Projekt zur Verfügung stehenden Personenjahre liegen z.B. Anastasia+, IPQ und Valse gleichauf in der Anzahl ihrer Veröffentlichungen auf Hauptkonferenzen. Auch bei den weiteren Konferenzen kann keine Korrelation zwischen einem hohen Anteil an Forschungsteilnehmern und einer hohen Anzahl von Veröffentlichungen gefunden werden, wie am Beispiel von HG-DAT und Valse deutlich wird. Somit hat die Anzahl der beteiligten Forschungsinstitute anscheinend keinen entscheidenden Einfluss auf die Anzahl der Veröffentlichungen.

### Ergebnisse zu den nicht abgeschlossenen Projekten

#### Projekten

In **Abbildung 12** sind die bis Ende 2003 publizierten Veröffentlichungen der zurzeit laufenden Projekte dargestellt. Die Veröffentlichungen wurden hier ebenfalls bezogen auf die bis Ende 2003 laut Vorhabenbeschreibung abgerufenen Personenjahre. Dabei waren zu diesem Zeitpunkt bei den Projekten Azteke, IP2 und Mesdie mehr als 50% der Projektlaufzeit vorbei, bei den restlichen Projekten knapp 25%. An der Grafik ist sehr gut zu erkennen, dass mit Veröffentlichungen auf Hauptkonferenzen erst im weiteren Verlauf der Projektarbeit zu rechnen ist. Erste Veröffentlichungen auf der DATE und der ITC gibt es bei den Projekten IP2 und Azteke; bei Mesdie wurden bereits mehrere Arbeiten auf der EMC veröffentlicht. Die übrigen drei Projekte Anastasia+ (II), SpeAC und Valse-XT sind noch im Anfangsstadium und mit Veröffentlichungen auf Hauptkonferenzen ist daher zu diesem Zeitpunkt noch nicht zu rechnen.

Abbildung 12

Insgesamt können die Ekopass-Projekte mit ihren Ergebnissen sehr zufrieden sein. Im Schnitt 8% der Veröffentlichungen auf großen Konferenzen, knapp 48% auf internationaler Ebene und 1,6 Personenjahre Aufwand pro Veröffentlichung – das ist eine sehr gute Ausbeute.

# Nachrichten von den Projekten

[www.edacentrum.de/newsletter](http://www.edacentrum.de/newsletter)

## Zweites Clusterforschungsprojekt gestartet

Das Clusterforschungsprojekt FEST „Funktionale Verifikation von Systemen“ hat sich zum Ziel gesetzt, Lösungen zu erforschen, die eine einheitliche Verifikation von SoCs ermöglichen. Hierzu werden, ausgehend von einer Systembeschreibung, bis hinunter zur elektrischen Ebene, Methoden und Verfahren erforscht, die vorhandene Verifikationslücken schließen.

Im Vordergrund stehen die Probleme, aus denen sich ein hohes Verbesserungspotenzial ergibt. Dazu werden neue Verifikationsverfahren unter industriellen Gesichtspunkten erforscht. Die Vernetzung verschiedener neuartiger Ansätze wird dabei durch die Umsetzung als Verbundprojekt ermöglicht. Die Integration der verschiedenen Verifikationsansätze wird auf der Basis einer gemeinsamen Plattform durchgeführt, um einerseits eine einheitliche Verifikationsmethodik zu ermöglichen und andererseits unabhängig von einzelnen Lösungswerkzeugen zu sein.

Das Projekt ist am 1.7.2004 gestartet und läuft über drei Jahre. Das Projektconsortium setzt sich aus Wissenschaftlern von 6 Universitäten zusammen: Prof. Dr. Hans Eveking (Technische Universität Darmstadt), Prof. Dr. Wolfgang Fengler (Technische Universität Ilmenau), Prof. Dr. Wolfgang Kunz (Universität Kaiserslautern), Prof. Dr. Bernd Becker (Universität Freiburg), Prof. Dr. Lars Hedrich (Universität Frankfurt) und Dr. Thomas Kropf (Universität Tübingen). Die Projektleitung erfolgt durch Dr. Volker Schöber, edacentrum.

## Projekt DETAILS bewilligt

Das Projektziel des Vorhabens DETAILS (HF Design Technologie für präzise analoge IP-basierte Front-End Lösungen in höchstintegrierten HDÜ-Systemen) ist der Aufbau einer effizienten HF-Entwurfstechnologie für wiederverwendbare hochintegrierte HF-Komponenten (Antennenschnittstelle) in zukünftigen hochkomplexen mobilen Kommunikationssystemen. Diese soll einerseits die Entwicklungszeit deutlich absenken und andererseits die Planungssicherheit erhöhen. Zentraler Punkt ist die Bereitstellung von neuen Verfahren zur präzisen Systemplanung und Konzeptionierung in einem geschlossenen automatisierten HF-Design-Flow, der deutlich mehr Design-Freiheitsgrade und zusätzliche hierarchische Entwurfsebenen unterstützt als bisher bekannte Konzepte. Mit besonderer Berücksichtigung der Schnittstellen zwischen System-

konzeptionierung, Schaltungsentwicklung und Prozess-technologie mittels geeigneter Präzisionsmodelle soll es möglich werden, für eine ausgewählte Prozesstechnologie eine optimale Systemarchitektur effizient und sicher zu entwickeln.

Das Projekt ist gestartet am 1.4.2004 mit einer Projektlaufzeit von 3 Jahren. Das Projektconsortium setzt sich zusammen aus der Nokia GmbH, der Infineon Technologies AG, der Atmel Germany GmbH, der Cadence Design Systems GmbH, der Melexis GmbH und der CST GmbH. Forschungsunteraufträge wurden an die Technische Universität Dresden, die Universität Ulm, das Fraunhofer Institut IIS/EAS in Dresden und die IMMS gGmbH in Erfurt vergeben.

Weitere Informationen bei Dr. Volker Schöber, 0511 762-19688, [schoeber@edacentrum.de](mailto:schoeber@edacentrum.de)

## Projekt LEMOS bewilligt

„Low-Power Entwurfsmethoden für mobile Systeme“ lautet der Titel des für drei Jahre geförderten BMBF-Projektes mit dem Kürzel LEMOS. Bei OFFIS in Oldenburg wurden im Rahmen eines Projektmeetings geplante und bereits begonnene Arbeiten vorgestellt und mit dem Projektträger (DLR) und den Partnern diskutiert.

Das Hauptziel des Projektes ist die wesentliche Steigerung der Entwurfseffektivität und -produktivität verlustleistungskritischer, mobiler Systeme. Dazu bündelt das LEMOS-Konsortium die deutschen Kompetenzen im Bereich der elektronischen Entwurfsautomation (EDA) sowohl auf Seiten des Entwurfs mobiler Systeme als auch im Bereich der Verlustleistungsanalyse und -optimierung. Die Projektpartner und Unterauftragnehmer Bosch, Catena, ChipVision, Fachhochschule Pforzheim, Infineon, Nokia, OFFIS, Ruhr-Universität Bochum, Technische Universität Cottbus, Technische Universität München und Universität der Bundeswehr München forschen seit Anfang des Jahres an einer durchgehenden Low-Power-Methodik, die bereits auf hoher Abstraktionsebene beginnt. Die erwarteten Vorteile dieses Herangehens sind

Weitere Informationen bei Dr. Jens Appell, OFFIS, 0441 9722-235, [appell@offis.de](mailto:appell@offis.de)

- » die Verringerung der Zahl der verlustleistungsbedingten Re-Designs, dadurch Verkürzung der Entwicklungszeit um mehr als ein Drittel,

- » die Verschiebung der Grenze des bislang aus Verlustleistungsgründen technisch nicht Machbaren und

- » die drastische Senkung des Energieverbrauchs.

Weitere Informationen bei Reimund Wittmann, Nokia GmbH, 0234 984-3480, [reimund.wittmann@nokia.com](mailto:reimund.wittmann@nokia.com)

In den konkreten Anwendungsbereichen ist es das Ziel von LEMOS, die für die Fahrzeugsicherung relevanten Bordgeräte eines Kraftfahrzeugs aus der Batterie drei Monate operativ zu erhalten, sowie die Leistungsaufnahme von Mobiltelefonen um mehr als 50% zu senken. Die gewonnenen Erkenntnisse fließen bereits während des Projektes in die Chipentwicklung in Form der Demonstratoren ein. Entstandene prototypische Werkzeuge werden direkt angewendet und innerhalb der EDA-Unternehmen ChipVision Design Systems

AG und Catena Software GmbH der Produktverwertung zugeführt. Die entstandenen Methoden werden zusätzlich durch die beteiligten Universitäten und Forschungsinstitute in ihr Lehrprogramm integriert.

Weitere Informationen bei Prof. Wolfram Büttner, Infineon Technologies AG, 089 234-46310, wolfram.buettner@infineon.com

Das Treffen bildete desweiteren den Ausgangspunkt für projektübergreifende Kooperationen z.B. in den Bereichen Power-Charakterisierung für IPs, Bus-Modellierung, Bibliotheken, sowie zum Thema Low-Power-Design-Flow. Hier ergeben sich auch Ideen für Anknüpfungspunkte zu anderen Projekten, wie z.B. SPEAK.

Weitere Informationen zum Projekt sowie Kontaktmöglichkeiten sind zu finden unter <http://lemos.offis.de>. Interessierte haben auch die Möglichkeit, sich auf dem BMBF-Forum „Mobiles Internet 2010“ in Königswinter bei Bonn am 14./15.09.2004 über LEMOS zu informieren.

#### **Mitarbeiter für das Projekt LEMOS gesucht**

Für Arbeiten innerhalb des Forschungsprojektes LEMOS sind von der Chipvision Design Systems AG Stellen ausgeschrieben worden. Chipvision ist Projektpartner im Projekt LEMOS, welches sich die Analyse und Reduzierung der Verlustleistung eingebetteter Systeme zum Ziel gesetzt hat (s. o.).

Weitere Einzelheiten finden Sie unter [www.chipvision.com/careers/LEMOS-ad.pdf](http://www.chipvision.com/careers/LEMOS-ad.pdf)

Das Stellenangebot richtet sich an Absolventinnen und Absolventen der Informatik, Elektrotechnik und verwandter Gebiete, die am Standort Oldenburg anwendungsorientierte Forschung im Bereich Software zur Unterstützung des ASIC-Entwurfs betreiben wollen.

#### **Erstes FALSE-XT-Review erfolgreich durchgeführt**

Am 9. Juli 2004 fand mit großem Erfolg das erste Review des Projektes Valse-XT in Erfurt statt. Das Projekt stellte seine Arbeiten in einer sehr guten Arbeitsatmosphäre dar, in der Fragen offen und kompetent beantwortet wurden. Besonders lobten die Reviewer das sehr gute Management des Projektes und bekraftigten die Wichtigkeit des Arbeitsgebietes. Zusätzlich erachteten die Reviewer die Ergebnisse als im höchsten Grade vermarkungswürdig und empfahlen, einen Marketing-Experten mit der Vermarktung der Ergebnisse zu beauftragen.

## 2 **Neues vom edacentrum**

#### **Programm edaForum04 steht fest**

<http://www.edacentrum.de/edaforum>

Das Programm des edaForum04 am 9. und 10. Dezember 2004 in Dresden wurde anfang September verschickt. Alle darin enthaltenen Informationen sowie aktuelle Entwicklungen sind auf den Internetseiten abrufbar.

Ansprechpartner ist Ralf Popp,

0511 762 19697, [popp@edacentrum.de](mailto:popp@edacentrum.de)

Weiterhin gibt es unter [www.edacentrum.de/](http://www.edacentrum.de/) newsletter eine Internetseite exklusiv für Mitglieder, in der vertiefende Inhalte zu jedem Newsletter dargestellt sind.

#### **Termine und Formalien für neue Projekte**

[www.edacentrum.de/projekttermine](http://www.edacentrum.de/projekttermine)

Die nächsten Termine für die Einreichung von Projekt- skizzen und Vorhabenbeschreibungen nähern sich. Um den Ablauf der Einreichungen für alle möglichst reibungslos zu gestalten und überflüssigen Aufwand zu vermeiden, bittet das Steuerungsgremium darum die Formalien zur Einreichung einzuhalten und weist darauf hin, dass Projektskizzen und Vorhabenbeschreibungen bei formalen Mängeln nicht berücksichtigt werden. Die Formalien betreffen einerseits die Termintreue und andererseits die Einhaltung der angegebenen Grenzen für den Umfang. Dies gilt insbesondere für die Projektskizze, die der Darstellung von Idee, Arbeitsplan und Verwertung des Vorhabens dient und die einen Umfang von 16 Seiten nicht überschreiten darf.

Ankündigung einer Einreichung:

**31. 08.2004**

Abgabe der ersten Version:

**14. 09.2004**

Abgabe der letzten Version:

**28. 09.2004**

Ansprechpartnerin zum Thema ist

Frau Dr. rer. nat. Cordula Hansen, 0711 2 30 57 68,

[hansen@edacentrum.de](mailto:hansen@edacentrum.de)

Die Workshop-Unterlagen stehen für Mitarbeiter der an MESDIE beteiligten Partnerunternehmen und Forschungseinrichtungen auf Anfrage (office@mesdie.org) zur Verfügung. Weitere Informationen bei Heiko Köhne, FhG-IZM, 030 46403-145, koehne@izm.fhg.de

Weitere Informationen sind beim Projektleiter Werner John, fon 05251 5402-100, office@mesdie.org und unter [www.mesdie.org](http://www.mesdie.org) erhältlich.

## MESDIE präsentiert seine Ergebnisse auf dem Workshop „IC basierte Elektromagnetische Verträglichkeit von Mikrosystemen“

Für die Betrachtung von Fragestellungen der Elektromagnetischen Verträglichkeit bei elektronischen Systemen spielen Integrierte Schaltkreise sowohl als Störquelle als auch als Störsenke eine wichtige Rolle. Schaltvorgänge auf ICs führen zu leitungsgebundenen Störungen, welche auf Gehäuse und Leiterplattenebene zu Fehlfunktionen bzw. zu elektromagnetischen Emissionen führt. Umgekehrt können eingestrahlte oder leitungsgebundene Störungen Fehlfunktionen, bzw. sogar irreversible Schäden in ICs hervorrufen.

Im Rahmen eines ganztägigen Workshops, der von dem MESDIE-Projektpartner Fraunhofer Institut für Zuverlässigkeit und Mikrointegration (Fraunhofer IZM) am 17. Juni 2004 in Paderborn veranstaltet wurde, wurden den Teilnehmern aus Industrie und Wissenschaft Forschungsschwerpunkte und Lösungsansätze zu dem Thema „IC basierte Elektromagnetische Verträglichkeit von Mikrosystemen“ aufgezeigt. Die Veranstaltung fand im Heinz Nixdorf Forum in Paderborn statt. Dem Teilnehmerkreis, bestehend aus Universitätsprofessoren, Mitarbeitern aus klein- und mittelständischen Unternehmen und Mitarbeitern von sog.

Großunternehmen, wurden im Wesentlichen Inhalte zur Störemission von ICs, dem Schutz vor ESD und zur Störfestigkeitsanalyse von analogen ICs vermittelt. Als Vortragende fungierten zwei Gastredner aus der Industrie sowie Wissenschaftler des Fraunhofer IZM. Begleitend zu den Vorträgen wurde darüber hinaus auch ein Aufbau zur leitungsgebundenen Emissionsmessung von ICs auf Chipebene sowie nach IEC Norm vorgestellt.

## MESDIE führt erfolgreich sein zweites Statusseminar durch

Vom 6.-7. Juli 2004 führte das MESDIE-Projekt sein Medea+-Review kombiniert mit seinem zweiten Statusseminar erfolgreich durch. Beide Veranstaltungen waren optimal geplant und strukturiert und ließen genug Raum für Fragen und Diskussionen. Ergänzt wurde die sehr gute Durchführung durch umfangreiches Unterlagenmaterial. Besonders lobenswert sind in diesem Zusammenhang auch die gute Vorbereitung der Partnerpräsentationen sowie die Vorführung der Ergebnisse mit Demonstratoren und Postern.

### Standardisierung

[www.edacentrum.de/standardisierung](http://www.edacentrum.de/standardisierung)

Im August 2004 ist der Rundbrief zur Standardisierung an unsere Mitglieder verschickt worden. Interessierte Mitglieder haben die Möglichkeit, sich in den Email-Verteiler aufnehmen zu lassen. Zusätzlich stehen alle Rundbriefe im Internet zur Verfügung.

Ansprechpartnerin zum Thema ist Frau Dipl.-Ing. Katrin Meßmer, 0511 762-19686, [messmer@edacentrum.de](mailto:messmer@edacentrum.de)

### Publikationen

[www.edacentrum.de/pressepiegel](http://www.edacentrum.de/pressepiegel)

Die Zeitschrift „Elektronik“ hat in Ihrer Ausgabe 15 vom 27. Juli eine zusammenfassende Darstellung der edaForum03-Keynote von Prof. Dr. Giovanni De Micheli unter dem Titel „Unschärferelation könnte Chipentwurf revolutionieren“ veröffentlicht. .

Ansprechpartner hierzu ist Herr Dipl.-Ing. Ralf Popp, 0511 762-19697, [popp@edacentrum.de](mailto:popp@edacentrum.de)

### Trendbericht

[http://www.edacentrum.de/mitglieder\\_intern/trendberichte/dac04.html](http://www.edacentrum.de/mitglieder_intern/trendberichte/dac04.html)

Der DAC 2004 Trendbericht ist am 9.8.2004 erschienen und wurde an die Mitglieder des edacentrum verteilt. Sie können sich den Bericht ebenfalls von den internen Mitgliederseiten des edacentrum herunterladen.

Ansprechpartner zum Trendbericht ist Ralf Popp, 0511 762 19697, [popp@edacentrum.de](mailto:popp@edacentrum.de)

### Mitgliederversammlung 2004

<http://www.edacentrum.de>

Die edacentrum-Mitgliederversammlung 2004 findet am 16. September von 12.00 bis 15.30 statt. Themen sind unter anderem die geplante Gründung der edacentrum GmbH. Aktuelle Informationen inklusive der Anfahrtsbeschreibung und des Anmeldeformulars finden sie auf den Internetseiten des edacentrum.

Ansprechpartner ist Ralf Popp, 0511 762 19697, [popp@edacentrum.de](mailto:popp@edacentrum.de)

# Panorama

## Meldungen

[www.edacentrum.de/newsletter](http://www.edacentrum.de/newsletter)

[Heise Newsticker 25.8.2004](#)

### **Gartner: Weltweite Halbleiter-Umsätze ziehen weiter an**

Als eine der Lehren aus dem Scheitern der Chipfabrik in Frankfurt (Oder) zieht der Ausschussvorsitzende Heinz Vietze, dass künftige Großvorhaben vorab intensiver geprüft werden müssen.

[Heise Newsticker 18.8.2004](#)

### **Abschlussbericht: Regierung trägt Mitschuld an Chipfabrik-Pleite**

Der Umsatz mit Halbleitern in Deutschland lag im Juli gleichauf mit dem Vormonat. Im Jahresvergleich stieg er indessen um 14 Prozent. Das Book-to-Bill-Verhältnis rutschte im Juli in die ‚rote Zone‘.

[EETimes.de 11.8.2004](#)

### **Halbleitermarkt im Juli: Stagnation auf hohem Niveau**

Der Umsatz mit Halbleitern in Deutschland lag im Juli gleichauf mit dem Vormonat. Im Jahresvergleich stieg er indessen um 14 Prozent. Das Book-to-Bill-Verhältnis rutschte im Juli in die ‚rote Zone‘.

[EETimes.de 4.8.2004](#)

### **IBMs eFuse-Verfahren erlaubt rekonfigurierbare Chips**

Mit einer neuen Chiptechnologie von IBM lassen sich adaptierbare Schaltkreise herstellen: Chips, die sich selbst an vorgegebene Parameter anpassen und optimieren.

[EETimes.de 4.8.2004](#)

### **Infineon Nummer eins bei Leistungshalbleitern**

Im Markt für Leistungshalbleiter hat Infineon die Pole Position errungen – gegen starke Konkurrenz, wie das Marktforschungsinstitut IMS Research ermittelt hat. Knapp geschlagen landeten auf den Plätzen zwei und drei die Hersteller International Rectifier und STMicroelectronics.

[Heise Newsticker 3.8.2004](#)

### **Globaler Chipverkauf legt um 40 Prozent zu**

Unter anderem seien DRAM-Preise angesichts der starken Nachfrage und des limitierten Angebots nicht mehr weiter gesunken, meinte der Halbleiterverband Semiconductor Industry Association.

[Heise Newsticker 27.7.2004](#)

### **Wearable für den „modebewussten Mann“**

Infineon und der Bekleidungshersteller Rosner haben eine Jacke vorgestellt, bei der Elektronik ein „integraler Bestandteil“ der Kleidung ist.

[EETimes.de 21.7.2004](#)

### **Bei Herstellern von Chip-Testern gärt es**

Wenn das Semiconductor Test Consortium (STC) mit seinen neuen Standardvorschlägen Erfolg hat, dürfen nicht nur die Kosten des Chiptestens sinken. Der Vorschlag dürfte auch in der gesamten ATE-Industrie (Automatic Test Equipment) für Unruhe sorgen. Es geht nämlich nicht nur um neue Test-Interfaces, sondern auch um neue Probe-Card-Standards.

[Heise Newsticker 21.7.2004](#)

### **Hightech-Branche rätselt über Dauer des Aufschwungs**

Nach jahrelanger Flaute läuft es derzeit eigentlich rund für die weltweite Hightech-Branche.

[channel-e 19.7.2004](#)

### **Atmel erweitert Design Center in Dresden**

Atmel stockt sein Design Center, das im Dezember 2001 eröffnet wurde, mit 32 neuen Entwicklern auf.

[Heise Newsticker 15.7.2004](#)

### **Höfliche Software steigert Zufriedenheit der Nutzer**

„Software-Designer müssen die Haltung entwickeln, dass der Nutzer immer Recht hat“, meint der taiwanische Wissenschaftler Jeng-Yi Tzeng.

[channel-e 14.7.2004](#)

### **Halbleiterumsatz Deutschland: Juni 2004**

Der Umsatz für Halbleiter in Deutschland lag laut ZVEI im Juni unter dem des Vorjahrs.

[Computerwoche 9.7.2004](#)

### **Gartner: Investitionen in Chipfertigungs-Equipment ziehen an**

Nach neuesten Schätzungen von Gartner wird der Markt für Chipfertigungs-Equipment im laufenden Jahr um 64 Prozent auf 37,3 Milliarden Dollar anwachsen.

EETimes.de 8.7.2004

### Analogmarkt wächst im High end

Ein starkes Wachstum von mehr als 30 % sagt das US-Marktforschungsinstitut Databaseans dem Hochleistungssektor der Analogtechnik voraus. Für das vergangene Jahr schätzen die Experten das weltweite Marktvolumen auf 8,2 Milliarden US-Dollar.

EETimes.de 5.7.2004

### Chipfabriken schießen wie Pilze aus dem Boden

Der Bau neuer Halbleiterfabriken hat im zweiten Quartal einen neuen Rekord erreicht – und zwar sowohl was die Anzahl der Bauprojekte angeht als auch deren Wert. Die aktivsten Fabrikbauer waren in Japan zu finden.

channel-e 2.7.2004

### Weltweiter Halbleitermarkt Mai 2004

Der globale Halbleiterumplatz betrug laut Semiconductor Industry Association (SIA) im Mai 17,32 Mrd. US\$. Gegenüber dem Vormonat ist das ein Plus von 2,1%. Gemessen am Mai 2003 beträgt die Steigerung 36,9%.

channel-e 1.7.2004

### Neuer Entwicklungschef bei Barcelona Design

Der neue Mann für Forschung und Entwicklung beim Analog-Designspezialist Barcelona Design heißt Anthony Luk. Luk kommt von Cadence und verfügt über eine 18jährige Erfahrung in der EDA-Branche.

Heise Newsticker 11.6.2004

### Halbleiterbranche erwartet starkes Umsatzwachstum

Bis 2007 erwartet der Verband der Halbleiterindustrie ein jährliches Durchschnittswachstum von 10,4 Prozent.

Heise Newsticker 11.6.2004

### US-Chiphersteller wollen Förderung für Nanoelektronik-Forschung

Die Industrievereinigung der US-Chiphersteller Semiconductors Industry Association befürchtet, die USA könnten innerhalb der nächsten 20 Jahre ihre Technologieführerschaft verlieren.

Heise Newsticker 11.6.2004

### Nanotech-Visionär beruhigt Kritiker

Eric Drexler, Pionier und Visionär der molekularen Nanotechnologie, hat in einem Aufsatz für das Fachmagazin Nanotechnology Kritiker der Nanotechnologie beruhigt.

Heise Newsticker 8.6.2004

### Neues Forschungszentrum für Nanoelektronik in Dresden geplant

Der Bund, der Freistaat Sachsen, die Fraunhofer-Gesellschaft sowie die Mikroelektronik-Unternehmen AMD und Infineon sollen das Projekt vorbereiten.

EEDesign 8.6.2004

### Mentor purchases 0-in, boosts verification suite

Mentor Graphics kauft 0-In Design Automation, ein Unternehmen, das Verifikationstools für ASIC-Lösungen und Systems on Chip anbietet.

EE Times 4.6.2004

### IC-Markt: Asien/Pazifik und Europa überholen

#### Japan

Die aktuellen Daten der World Semiconductor Trade Statistics (WSTS) enthalten eine Überraschung: Neben dem asiatisch-pazifischen Wirtschaftsraum gehört auch Europa zu den Wachstumsträgern. Beide Bereiche werden in diesem Jahr den bisherigen Spitzenreiter Japan beim Halbleiter-Absatz überrunden.

channel-e 3.6.2004

### Technikchef bei Philips Halbleiter ernannt

Philips Halbleiter hat René Penning de Vries zum Senior Vice President und Chief Technology Officer ernannt. In dieser Position arbeitet er mit Theo Claassen zusammen, den er Mitte 2005 ablösen wird, wenn dieser seine Tätigkeit wie angekündigt beenden wird.

Computerwoche 3.6.2004

### Der Chipmarkt legt wieder mächtig zu

2004 sollen die weltweiten Umsätze mit integrierten Schaltkreisen aller Art von 177,2 Milliarden Dollar im Vorjahr um 28,4 Prozent in die Höhe schnellen.

channel-e 2.6.2004

### Weltweiter Halbleitermarkt April 2004

Die SIA (Semiconductor Industry Association) meldet für April einen weltweiten Umsatz mit Halbleitern in Höhe von 16,94 Mrd.US\$. Dieser Wert liegt 4,1% über dem März-Ergebnis und 36,6% über der Marke für April 2003.

EE Times 25.5.2004

### Cadence eröffnet F&E-Center in Moskau

Der Anbieter von EDA-Software setzt damit seine strategischen Investitionen in Russland fort. Die neue Einrichtung ist gleichzeitig das erste EDA-Forschungs- und Entwicklungszentrum, das in Russland von einem ausländischen Unternehmen betrieben wird.

# Von unseren Partnern im Ausland

## **EDA Consortium: Die Fortsetzung der Studie von Handel Jones im Internet verfügbar**

Die Fortsetzung der Studie von Handel Jones ist inzwischen verfügbar. Das EDA Consortium und das edacentrum e.V. haben eine Neuauflage und Aktualisierung der Studie „Analysis of the Relationship between EDA Expenditures and Competitive Positioning of IC Vendors“ von Dr. Handel Jones, CEO von International Business Strategies Inc., in Auftrag gegeben. Darin wird eine Aktualisierung der bereits 2002 zum ersten Mal erstellten Untersuchung der Abhängigkeit zwischen Investitionen in Entwurfstechnologie und der Marktposition von Firmen fortgeschrieben.

Die über mehrere Jahre vertraulich aufgenommenen Daten der Kunden von IBS belegten schon in der ersten Studie, dass System- und Halbleiterfirmen, die in Designtechnologie investieren, deutlich erfolgreicher sind, als die Firmen, die eher die Fertigungstechnologie fördern. Erstmals zeigte damit eine unabhängig erstellte Studie einen positiven Zusammenhang zwischen Investitionen in Entwurfsautomatisierung und Profitabilität von Halbleiterfirmen.

[Den vollständigen Bericht \(53 Seiten\) zu der Studie aus dem Jahr 2004 finden Sie unter:](#)

[www.edacentrum.de/

mitglieder](http://www.edacentrum.de/mitglieder)

Für Manager aus der Halbleiterindustrie wird die Neuauflage der Studie neues erweitertes „hartes Zahlenmaterial“ zur Argumentation liefern: Damit kann ein Weg aufgezeigt werden, wie der eigene Marktanteil und die Rentabilität von Produkten während des nächsten wirtschaftlichen Aufschwunges erhöht werden kann, nämlich durch Investitionen in Entwurfstechnologie! Außerdem bieten die Ergebnisse eine gute Grundlage für die Investoren und Analytiker der Halbleiterbranche, die Kriterien suchen, nach denen fortschrittliche Unternehmen auszuwählen sind.

## **EDA Consortium wählt leitende Angestellte und Mitglieder des Vorstandes**

Das EDA Consortium hat die Wahl eines neuen neunköpfigen Vorstandes bekannt gegeben, welches bis April 2006 amtierien wird. Dr. Walden C. Rhines, CEO der Mentor Graphics Corporation, wurde dabei als Vorsitzender bestätigt. Als weitere Mitglieder des Vorstandes des EDA Consortium sind gewählt:

- » Moshe Gavrielov, CEO von Verisity Design,

- » Bernard Aronson, CEO von Synplicity,

- » Dr. Jacques Benkoski, CEO von Monterey Design Systems,

- » Ray Bingham, Chairman des „Board of Directors“ von Cadence Design Systems

- » Dr. Aart de Geus, CEO von Synopsys,

- » Jim Douglas, CEO von ReShape,

- » Kathryn Kranen, CEO von Jasper Design Automation.

- » Alan Naumann, CEO von CoWare,

[Weitere Informationen über das EDA Consortium finden Sie unter \[www.edac.org\]\(http://www.edac.org\).](#)

Als „Executive Director“ wird Pamela Parrish ihre Aufgaben weiterhin wahrnehmen. Während der kommenden Jahre will das EDA Consortium seine Aufmerksamkeit verstärkt auf das allgemein bekannte Problem der Software-Piraterie richten, bemerkte Rhines. Außerdem wolle man sich der EDA-Roadmap für Betriebssysteme und der Hilfestellung für Mitglieder bei Problemen mit dem Export von Entwurfssoftware zuwenden.

Ansprechpartner zu dieser

Rubrik:

Ralf Popp,

fon: 0511 762-19697,

[popp@edacentrum.de](mailto:popp@edacentrum.de)

# Zum Thema Standardisierung

[www.edacentrum.de/standardisierung](http://www.edacentrum.de/standardisierung)

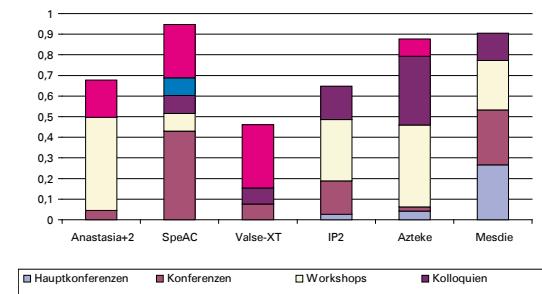

## Konferenzanalyse zur Standardisierung international

Veröffentlichungsanalyse der Ekompass-ProDie Konferenzanalyse wurde mit dem Ziel durchgeführt zu ermitteln, welche Veröffentlichungen zu Standardisie-

Standardisierungsveröffentlichungen

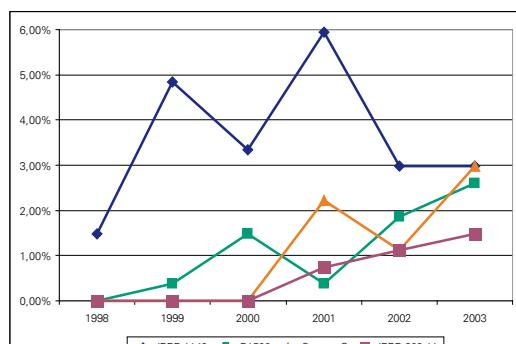

Abbildung 13

rungsthemen auf Konferenzen vorgestellt wurden und welche Konferenzen sich besonders als Plattform für Veröffentlichungen von Standardisierungsaktivitäten eignen. Analysiert dazu wurden die fünf großen Konferenzen im Bereich EDA (DAC, DATE, ICCAD, ITC und ASPDAC) für den Zeitraum 1998 bis 2003.

Bei der Analyse wurden vor allem folgende Fragestellungen verfolgt: Welche neuen Standards werden veröffentlicht, welche Arbeiten zu Standards (Wei-

terentwicklungen oder Einbeziehung von Standards) werden durchgeführt und welche neuen Standardentwicklungen werden angestrebt.

Insgesamt wurden 4258 Konferenzbeiträge untersucht. 6,3% dieser Veröffentlichungen hatten den Schwerpunkt Standards und Standardisierungsaktivitäten.

**Abbildung 13** zeigt die Entwicklung der Veröffentlichungen zum Thema Standardisierung nach Jahren. Es ist zu erkennen, dass die Publikationen im Jahre 1998 von ca. 30 auf ca. 60 im Jahre 2003 gestiegen sind.

Alle zwei Jahre ist ein Einbruch bei den Veröffentlichungen zur Standardisierung zu erkennen, insgesamt nehmen die Veröffentlichungen aber kontinuierlich zu. Interessant ist auch, dass vier Standards sehr häufig Gegenstand von Publikationen waren (**Darstellung in**

**Abbildung 14**). Die am meisten verwendeten Standards sind der Standard IEEE 1149 für Mixed-Signal Test Bus, der Standard IEEE 802.11 für Wireless Local Access Network, der Standard P1500 für Embedded Core Test (SECT) und der Sprachstandard SystemC.

Grundsätzlich zeigt sich bei dieser Analyse, dass Standardisierung ein wichtiges Thema bei Veröffentlichungen auf Konferenzen ist. Vergleicht man die Konferenzen untereinander, stellt sich heraus, dass auf den asiatischen Konferenzen weniger Veröffentlichungen zu Standardisierungsthemen vorgestellt werden.

Es ist davon auszugehen, dass, wie durch die Bilder untermauert, die Zahl der Standardisierungsveröffentlichungen in den nächsten Jahren weiter steigen wird.

Abbildung 14

**Abbildung 13:**

Standardisierungs-

veröffentlichungen 1998-2003.

**Abbildung 14:**

Standardisierungs-

veröffentlichungen 1998-2003.

Ansprechpartnerin zu dieser

Rubrik:

Karin Messmer,

fon: 0511 762-19697,

messmer@edacentrum.de

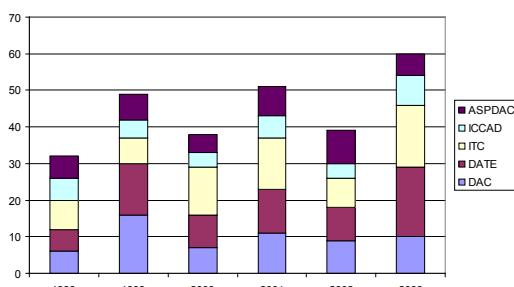

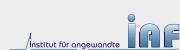

## EDA-Industrie verzeichnet im ersten Quartal 2004 ein Wachstum von 6 % gegenüber dem Vorjahr.

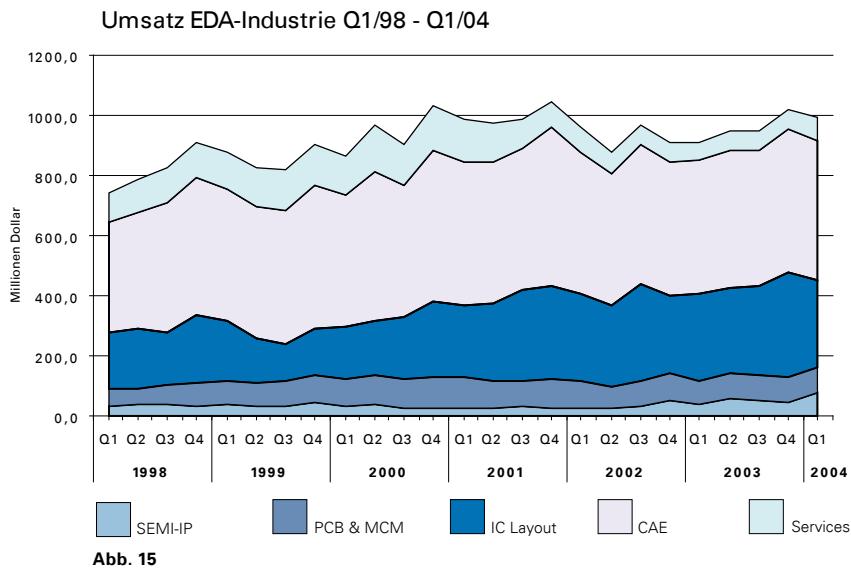

Umsatz EDA-Industrie Q1/98 - Q1/04

Abb. 15

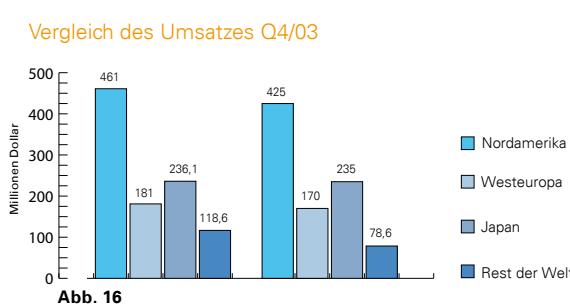

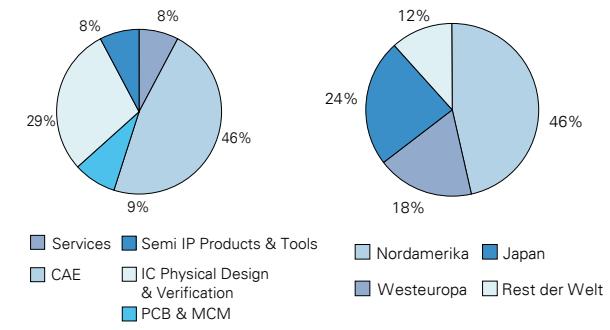

In der vom EDA Consortium am 02.08.2004 veröffentlichten Marktstatistik (MSS) wird berichtet, dass der Umsatz der EDA-Industrie in Q1/2004 995 Millionen Dollar betrug, was einem Anstieg um 6 % gegenüber demselben Vorjahresquartal entspricht. Der Umsatz bei den EDA-Services schoss gegenüber Q1/2003 um 31 % auf 76 Millionen Dollar in die Höhe. Im EDA-Branchen-Bereich der Semiconductor-Intellectual-Property (SIP) zeigte sich ein Anstieg um 15 % gegenüber dem gleichen Vorjahresquartal auf 71 Millionen Dollar.

„Der Umsatzanstieg bei Service und SIP ist ein guter Indikator für die wiedererstarkte Entwurfsaktivität“ sagte Walden C. Rhines, Chairman des EDA Consortium sowie Chairman und CEO bei Mentor Graphics Corp. Er ergänzte, dass dies irgendwann zu weiteren Tool-Verkäufen führen sollte.

Der Umsatz im Bereich EDA-Produkte und Wartung (ohne EDA-Services) belief sich auf 840 Millionen Dollar in Q1/2004 (3 % mehr als in Q1/2003) und machte 84 % des Gesamtumsatzes der EDA-Industrie in diesem Zeitraum aus. Computer Aided Engineering (CAE), die größte Kategorie im Bereich EDA-Produkte und Wartung, erreichte Umsätze in Höhe von 470 Millionen Dollar in Q1/2004 und damit 6 % mehr als im gleichen Zeitraum 2003. In der Kategorie PCB- und MCM-Layout wurden 85 Millionen Dollar in Q1/2004 umgesetzt, 5 % mehr als in Q1/2003. Die Umsätze bei IC Physical Design & Verification betrugen 285 Millionen Dollar

in Q1/2004, was einem geringen Rückgang von 2 % gegenüber den 288 Millionen Dollar in Q1/2003 entspricht.

Nach Regionen stiegen die Umsätze in Nordamerika um 5 % auf 461 Millionen Dollar. Europa und Japan verloren 4 % auf 181 Millionen Dollar bzw. 2 % auf 236 Millionen Dollar. Ein starker Anstieg von 36 % gegenüber Q1/2003 entfiel auf den Rest der Welt, wo ein Umsatz von 116 Millionen Dollar erzielt wurde. Im ersten Quartal 2004 waren 19.700 Mitarbeiter im EDA-Bereich angestellt, 3 % mehr als in Q1/2003. Dies ist die höchste Zahl seit Beginn der Datenerfassung im Jahre 2000.

Die vollständigen Marktstatistik-Berichte können gegen eine jährlich anfallende Gebühr bezogen werden. Sie werden in jedem Quartal vom EDA Consortium verteilt, und enthalten jeweils die Zahlen des vorausgegangenen Quartals. Die Statistiken sind aufgeschlüsselt nach Umsatzarten (Produkt- und Lizenzumsatz, Umsatz in Consulting- und Design-Service und weitere Umsätze), Anwendungsarten (CAE, PCB/MCM Layout, IC Layout, SIP), Betriebssystemen (UNIX, Windows), und Regionen (Nordamerika, Westeuropa, Japan und andere Länder), wobei zahlreiche Unterkategorien aufgeschlüsselt werden.

Umsatz Q4/03 nach Kategorien Umsatz Q4/03 nach Regionen

Abb. 16

Abb. 17

Abb. 18

# Umfrage zum DAC-Trendbericht 2003

Im letzten Jahr haben wir kurz nach dem Versenden des Trendberichts zur DAC 2003 eine Email-Umfrage zu diesem Bericht durchgeführt, deren Ergebnis an dieser Stelle bekannt gegeben werden soll.

Bei der Umfrage wurden sechs Aussagen (multiple-choice) zum DAC-Trendbericht erbeten, die Aufschluss über die Zufriedenheit der Leser geben sollten. Von den etwa 250 Empfängern von Trendbericht und Fragebogen antworteten genau 50 Personen. Die statistische Basis des Ergebnisses dieser Umfrage ist somit 20 % der Befragten, was als relativ hoch angesehen werden kann. Die 80 % der Befragten, die sich nicht geäußert haben, kann man als zustimmende oder missbilligende Mehrheit sehen, was allerdings beides als nicht seriös gelten würde. Daher wurden diese 80 % der Befragten bei dieser Auswertung nicht weiter berücksichtigt.

Nachfolgend werden die Ergebnisse im Einzelnen dargestellt.

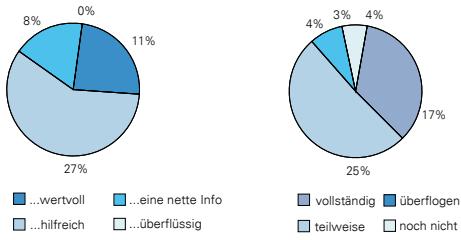

Die erste Frage zielte auf den Nutzen des Berichts ab und ist in **Abbildung 19** wiedergegeben.

Der Bericht ist für mich ...

Abb. 19

Abb. 20

Aus den Zahlen lässt sich erkennen, dass mehr als drei Viertel der Antwortenden einen nennenswerten Nutzen in dem Trendbericht sehen, was auch in zusätzlichen Kommentaren wiederzufinden war. So kam es zu Aussagen wie „schöner Überblick“, „außerordentlich hilfreich“, „sehr wertvoll“, „Bericht genossen“, „...beeindruckt, wie viel Inhalte...“ oder „gute Zusammensetzung.“

Die nächste Aussage sollte einen Überblick darüber geben, wie viel von dem Bericht gelesen wird, was in **Abbildung 20** dargestellt ist.

Dabei ergab sich, dass eine überwältigende Mehrheit der Antwortenden (25) den Bericht zumindest teilweise und immerhin noch ein Drittel (17) den Bericht vollständig gelesen hat.

Der Umfang des Berichts wurde von knapp einem Drittel (16) als zu lang und von über 50 % (28) als gerade richtig empfunden. Lediglich einer der Antwortenden hätte es gerne noch ausführlicher gehabt.

Für zwei Drittel der Antwortenden (33) bot der Bericht einen guten Überblick über die Ereignisse auf der DAC während er für ein Viertel lediglich eine Orientierung gab. Dass keiner der Antwortenden den Bericht für „viel zu lückenhaft“ ansah, wurde am edacentrum beruhigt registriert.

Der Schreibstil des Berichts wurde als angenehm empfunden. Ein Viertel der Antwortenden (12) gaben an, der Bericht lese sich ausgezeichnet, während zwei Drittel davon sprachen, dass er sich „gut“ lesen lasse.

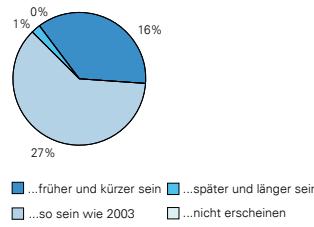

Auch der Trade-Off zwischen Umfang und Erscheinungszeitpunkt wurde von der Mehrheit der Antwortenden mit Zustimmung bewertet, was in **Abbildung 21** dargestellt ist.

Während 55 % (27) mit der Situation im Jahr 2003 zufrieden waren, wünschten sich immerhin 32 % (16), dass der Bericht lieber früher und mit geringerem Umfang erscheinen sollte.

Kombination von Zeitpunkt und Umfang:

Der Bericht sollte ...

Abb. 21

**Abbildung 19:** Mögliche Aussagen zum Nutzen des DAC-Trendberichts mit der statistischen Verteilung der Antworten.

**Abbildung 20:** Mögliche Aussagen zum Leseumfang des DAC-Trendberichts mit der statistischen Verteilung der Antworten.

**Abbildung 21:** Mögliche Aussagen zum Trade-Off zwischen Umfang und Erscheinungsdatum des DAC-Trendberichts mit der statistischen Verteilung der Antworten.

Generell wurde das Konzept gelobt, nicht technisch detailliert vorzugehen, sondern in den Podiumsdiskussionen nach Kontroversen zwischen Wettbewerbern zu suchen. Dies ist insbesondere vor dem Hintergrund verständlich, dass firmeninterne Zusammenfassungen von DAC-Besuchen oft auf neue Details spezieller EDA-Software und auf Roadmaps fokussiert sind, was aber auch von den EDA-Anbietern direkt erfragt werden könnte. Im Gegensatz dazu gebe es wenig Möglichkeiten etwas über das allgemeine Stimmungsbild zu erfahren, was der DAC-Bericht des edacentrum hingegen sehr schön herausarbeite.

Mit dem über die Umfrage erhaltenen Feedback sind wir am edacentrum, vor allem aber natürlich dessen Autor, sehr zufrieden gewesen. Die Botschaft eines kräftigen „Weiter so!“ ist angekommen und hat uns bei der Erstellung des diesjährigen DAC-Berichts gut motiviert – auch wenn das leider nicht zu einem frühzeitigerem Erscheinungstermin geführt hat, aber das hat andere Gründe, wie Sie, liebe Leserinnen und Leser, bereits dem Vorwort entnehmen konnten.

Ansprechpartner zu dieser Rubrik: Ralf Popp, 0511 762-19697, [popp@edacentrum.de](mailto:popp@edacentrum.de)

## Mitglieder für Mitglieder

### Nachrichten von unseren Mitgliedern

In dieser Rubrik geben wir unsren Mitgliedern die Möglichkeit, Hinweise und Neuigkeiten innerhalb des Vereins bekannt zu machen, um so einen intensiveren Informationsaustausch zwischen den Mitgliedern zu ermöglichen.

Ansoft GmbH:

#### **Ansoft kündigt Global Seminars 2004 an: Elektro-mechanik-Serie und Aufruf für Präsentationen**

Pittsburgh, Pennsylvania / München - 23. Juli 2004

- » Wer: Ansoft Corporation (NASDAQ: ANST)

- » Was: GSEM ,04: 2004 Global Seminars - Electromechanical Simulation Series und Call for Presentations

- » Wann: Oktober bis November

- » Wo: An Orten in Asien und Europa

#### **Über die Veranstaltungen**

GSEM ,04: 2004 Global Seminars - Electromechanical Series vermittelt einen realistischen Überblick über den Stand der Technik im Bereich des Designs und der Simulation elektromechanischer Systeme. Ebenso werden Lösungen präsentiert, die auf die künftigen Anforderungen der Bereiche Elektrotechnik, Automotive Systeme, Leistungselektronik und Antriebstechnik zugeschnitten sind. Die Seminarteilnehmer lernen, wie Industriefachleute die Simulation nutzen, um beim Design moderner elektromechanischer Funktionseinheiten mehr Effizienz zu erreichen, wie u. a. elektrisch betriebene Lenkhilfen, Pumpen und Lüfter, elektromechanische Aktuatoren oder Power-Processing-Elemente. Die Veranstaltung in Deutschland wird am 21. Oktober 2004 im Stuttgart-Marriott-Hotel in Sindelfingen stattfinden.

#### **Präsentationen:**

Interessierte können eine 100 Worte umfassende Inhaltsangabe ihrer Präsentation einreichen (per E-Mail unter [gsem04@ansoft.com](mailto:gsem04@ansoft.com)).

*how big can you dream?"*

Cadence Design Systems:

#### **Cadence stellt First Encounter Global Physical Synthesis vor**

Cadence stellt mit Cadence First Encounter Global Physical Synthesis (GPS) ein neues Produkt vor, das ein virtuelles Halbleiter-Prototyping und eine globale physikalische Synthese-Technologie der zweiten Generation in einer einzigen Umgebung integriert. Mit First Encounter GPS können Entwickler - gegenüber den bisherigen Methoden - sehr viel größere Chips erstellen. Die neue Technologie vervollständigt das Core-Technologieportfolio der Cadence Encounter digitalen IC-Designplattform in der Encounter Version 4.1.