# Workload-basierte Verlässlichkeitsanalyse für eingebettete Prozessoren

Oliver Bringmann, <u>Stefan Stattelmann</u>, Björn Sander

Universität Tübingen / FZI Forschungszentrum Informatik

#### Outline

Embedded Software: Power & Temperature

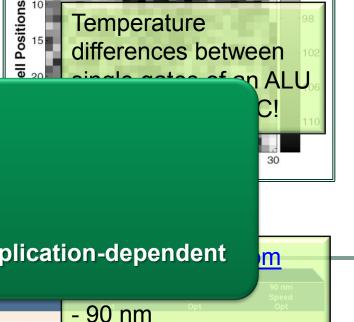

System-Level Simulation of Non-Functional Properties by Host-Compiled Execution

Application-Dependent Power and Temperature Simulation

Framework

Areas of Application

# Challenges: Automotive Electronics

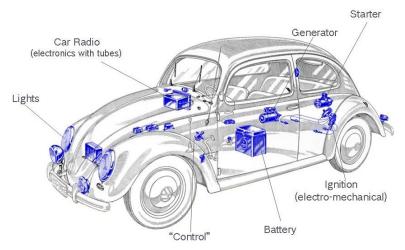

#### Yesterday ...

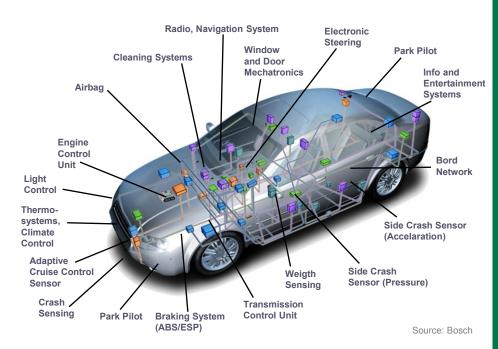

#### ... and today

|                  | <b>A8</b> | <b>A4</b> | A8 new |

|------------------|-----------|-----------|--------|

| Number of ECUs   | 68        | 65        | 85     |

| Number of Busses | 6         | 6         | 7      |

| Software (Mbyte) | 60        | 90        | >230   |

Source: Audi

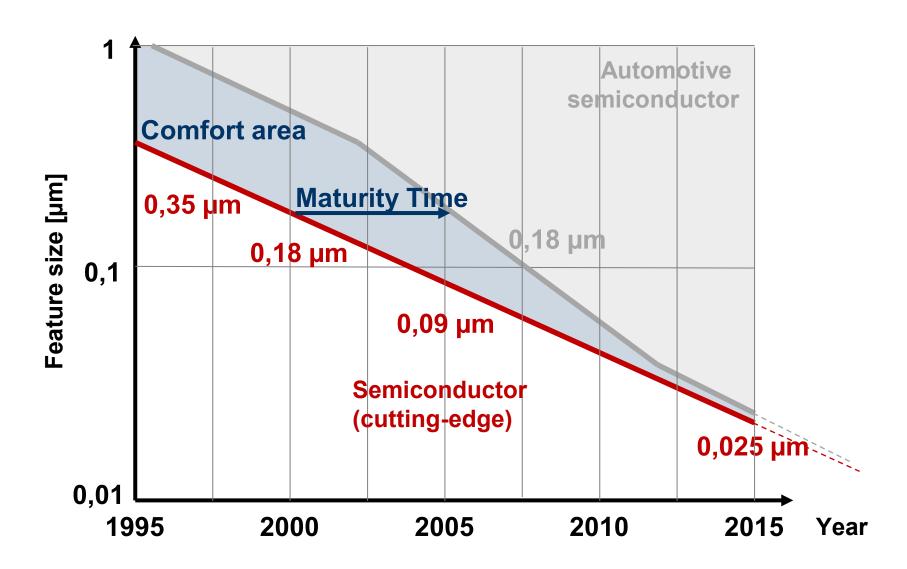

## Automotive Electronics – Reducing Comfort Area

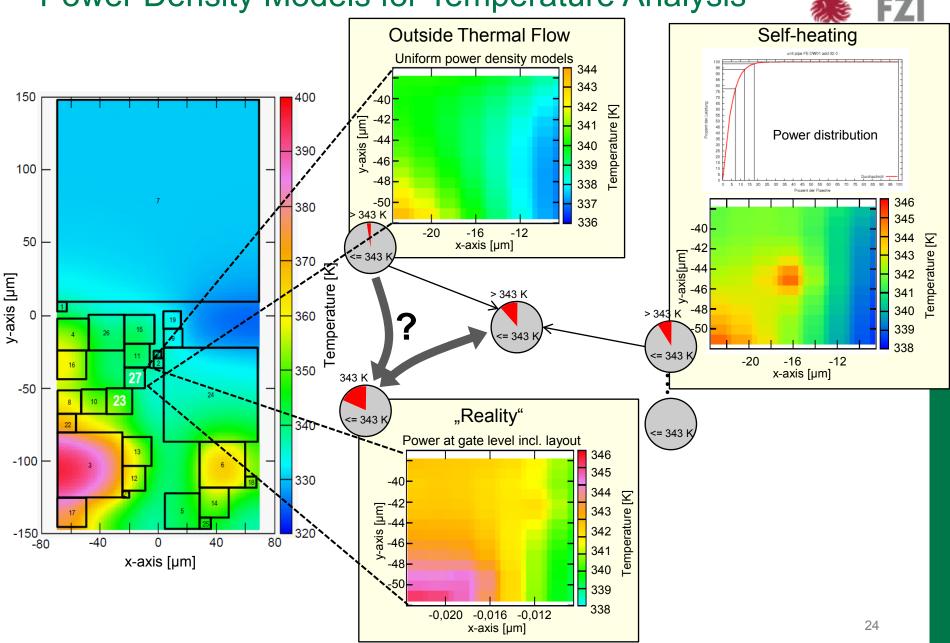

## Temperatures: Dominated by Local Power Effects

"...thermal modeling at finer granularity level i.e., transistor level or logic gate level is required for more accurate estimation of local hot spots." Bansal et al., ASP-DAC 2006

hat anota tone of migramators in

#### **Conclusion:** Non-Functional Properties

- Performance

- **Energy and Power Consumption**

- Temperature and Power Densities

have to be considered and are strongly application-dependent

Frequency\* (MHz)

Power † (mW/MHz)

silicon; 90nm process

† Typical case conditions

- Example: ARM7TDMI

- Power RUN state: 1.3 mW => Power density: 3.9 W/cm<sup>2</sup>

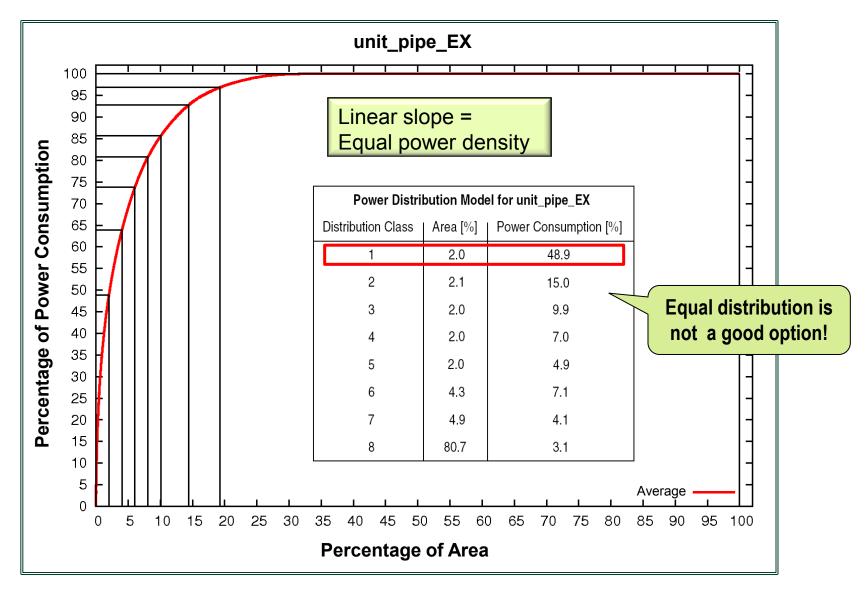

**Assuming an equal distribution** is probably not accurate

- 236 MHz

- 0.18 mm<sup>2</sup>

- 0.03 mW/MHz

Temperature Map for alu4

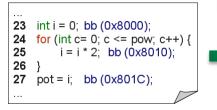

# Example: Power Simulation at Different Levels of Abstraction

• ARM7TDMI, 90 nm, 236 MHz, 0.18 mm<sup>2</sup>

Accuracy insufficient. System model disregards the number of branches in the application.

|                                                 |                           | gcd                                                       |                                              | ellip             |                      |

|-------------------------------------------------|---------------------------|-----------------------------------------------------------|----------------------------------------------|-------------------|----------------------|

| Functional<br>Representation                    | Power<br>Model            | Simulation Factor<br>(Simulation Time<br>/Simulated Time) | Average Power -<br>Error (comp. to<br>MS+PC) | Simulation Factor | Average Fower -<br>E |

| <b>Task Graph,</b> CDG,<br>CFG                  | Average                   | << 1                                                      | 4.17 uW - 81 %                               | << 1              | 4.17 uW -541 %       |

| Instrum. Source-Code                            | Instruction-<br>Dependent | 0.5                                                       | 5.8 uW - 31 %                                | 0.1               | 0.39 uW - 66 %       |

| Static BinaryTransl., Dynamic Binary Transl.    | Data-<br>Dependent        | 75                                                        | 9.69 uW - 28 %                               | 10                | 0.70 uW - 7 %        |

| Netlist: ModelSim (MS)<br>+ Power Compiler (PC) | PC Internal               | > 1010                                                    | 7.57 uW                                      | > 1010            | 0.65 uW              |

Data-dependent power model leads to a small error. But usually some kind of RTL simulation is necessary to calculate input stimuli of the components.

Simulation speed and appearing error are acceptable. Efficient link with information from binary level could be very promising.

# SYSTEM-LEVEL SIMULATION OF NON-FUNCTIONAL PROPERTIES BY HOST-COMPILED EXECUTION

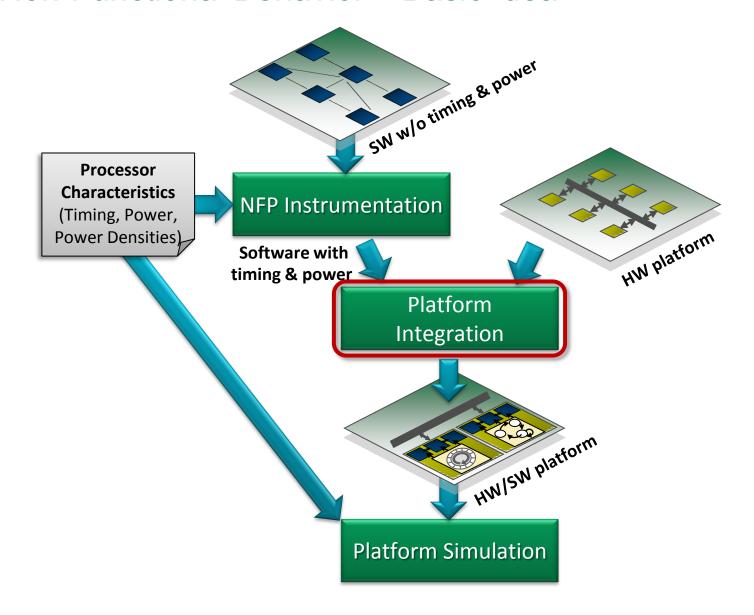

# Simulation of Functional and Non-Functional Behavior – Basic Idea

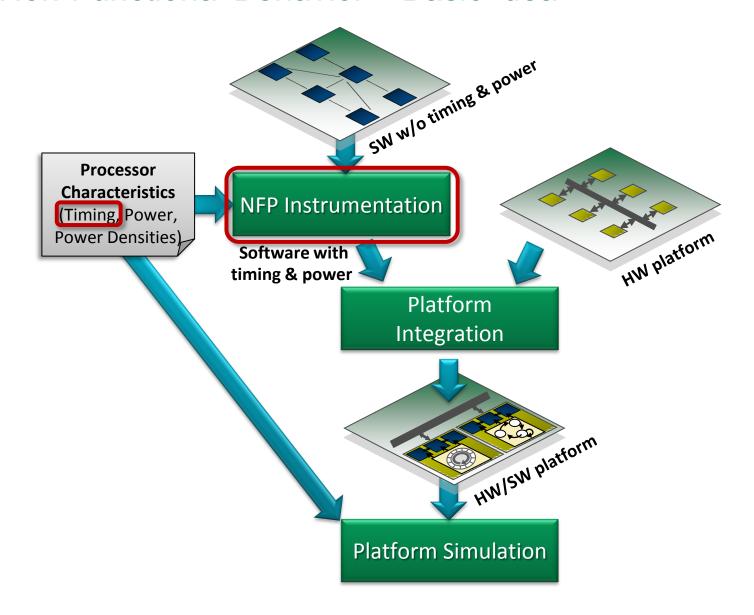

# Basic Idea: Source-Level Timing Instrumentation

# Proposed Hybrid Approach

- Compilation into binary code

- Static execution time analysis w.r.t. architectural details

Back-annotation of analyzed timing information into the source code

- Simulation by host-compiled execution

```

int c, int d)

{

int res;

res = (a + b) << c - d;

delayn( Besms );

}

00000000 <f>:

; int f( int a, int b;

; int c,

; int c,

; {

3 ms

```

int f(int a, int b,

#### **Important**

Compilation

- Requires accurate relation between source code and binary code

- Run-time models for branch prediction and caching have to be incorporated

## **Compiler Optimizations**

- Structure of source code and binary code can be completely different

- Function Inlining adds basic blocks

- Loop Unrolling modifies execution count of basic blocks

- ...

- Compilers don't generate accurate debug information for optimized code

- → No 1:1 relation between source-level and binary-level basic blocks

- → Simply annotating delay attributes for source-level timing simulation does not work

How to match structure of source code and machine instructions?

10

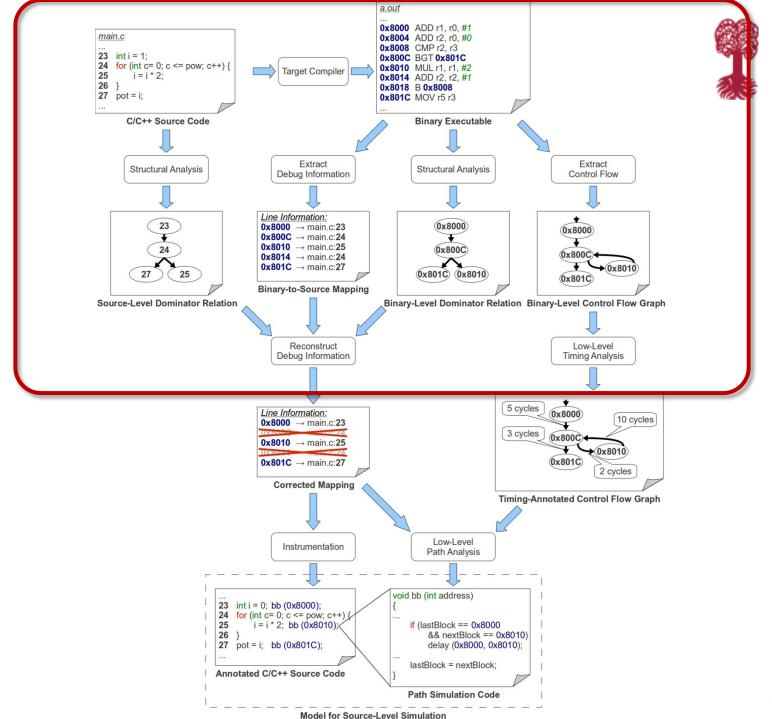

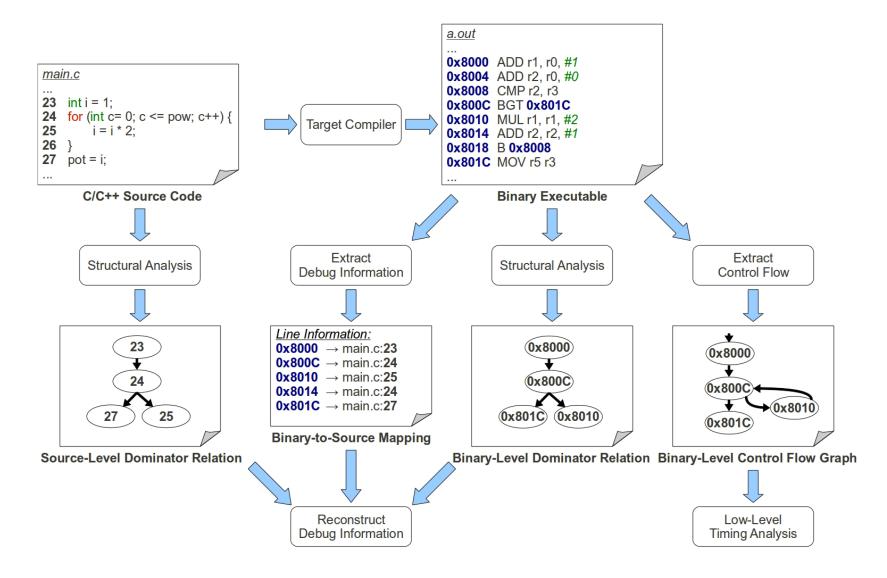

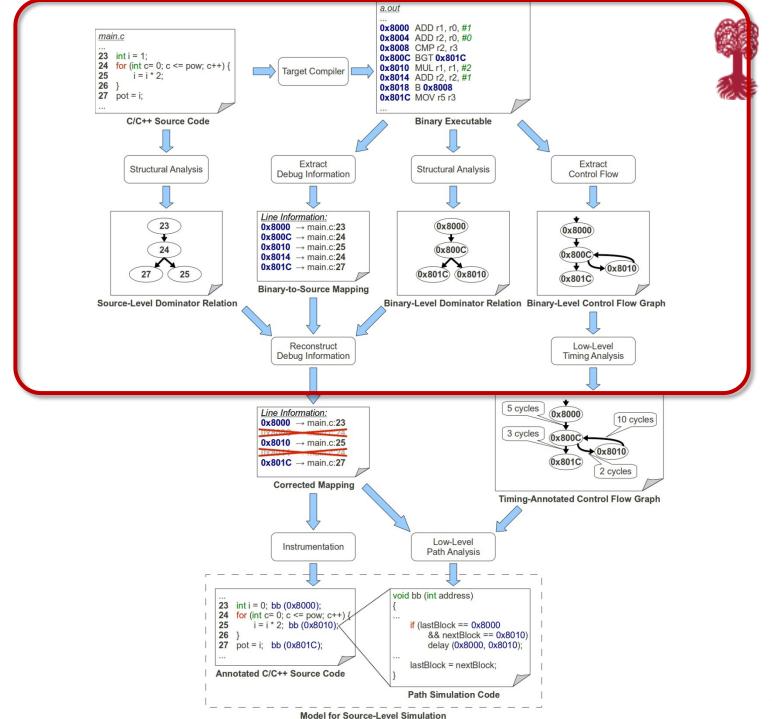

# Structural Analysis and Code Matching

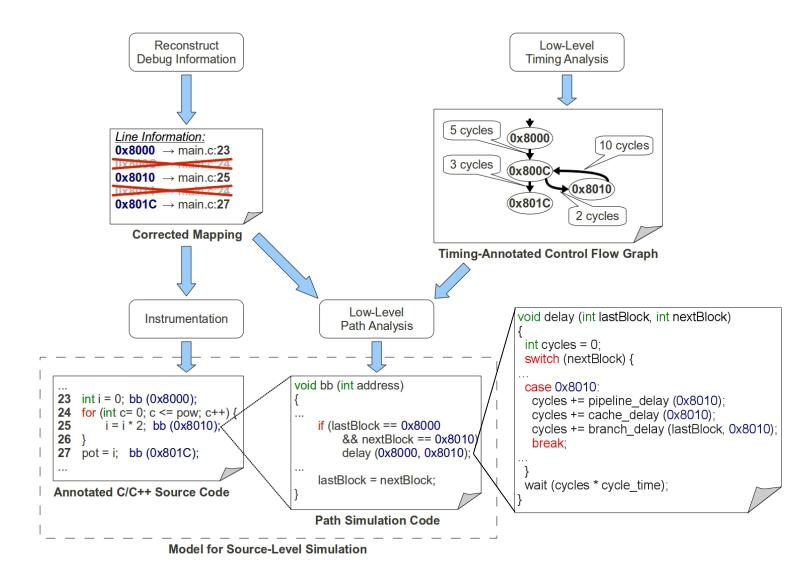

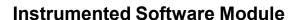

#### Annotation and Path Simulation Code Generation

# Simulation of Functional and Non-Functional Behavior – Basic Idea

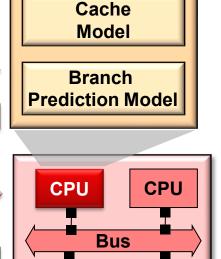

# **Platform Model Integration**

**Architectural Model**

**Virtual Platform**

1/0

**CPU**

**TLM-2.0 Loosely Timed Simulation**

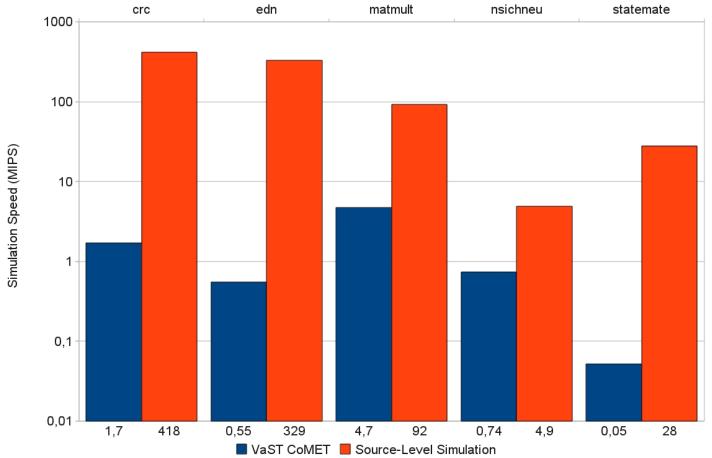

## **Experimental Results**

- Experiments conducted for an ARM processor

- Improved simulation performance compared to high-performance ISS based on just-in-time compilation

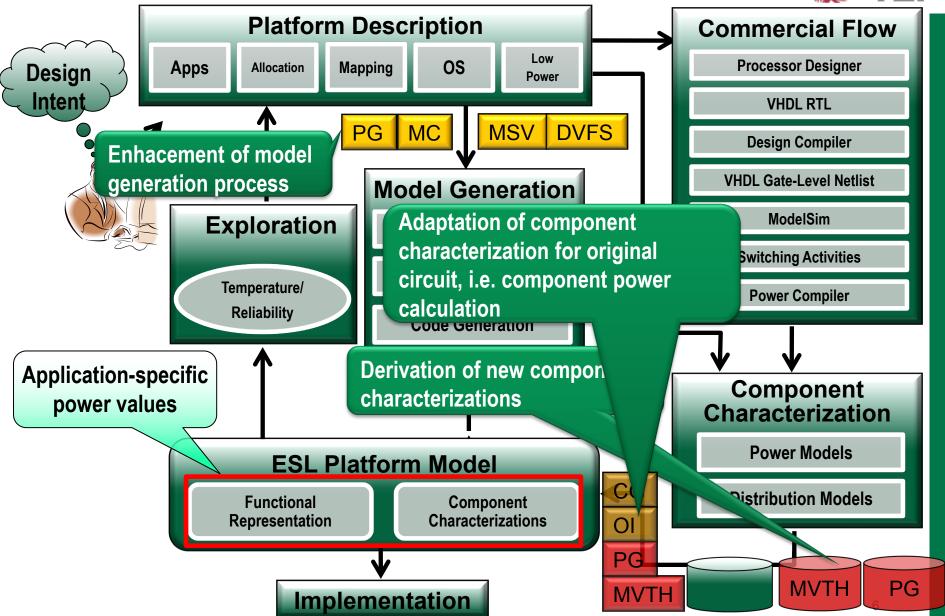

# APPLICATION-DEPENDENT POWER AND TEMPERATURE SIMULATION FRAMEWORK

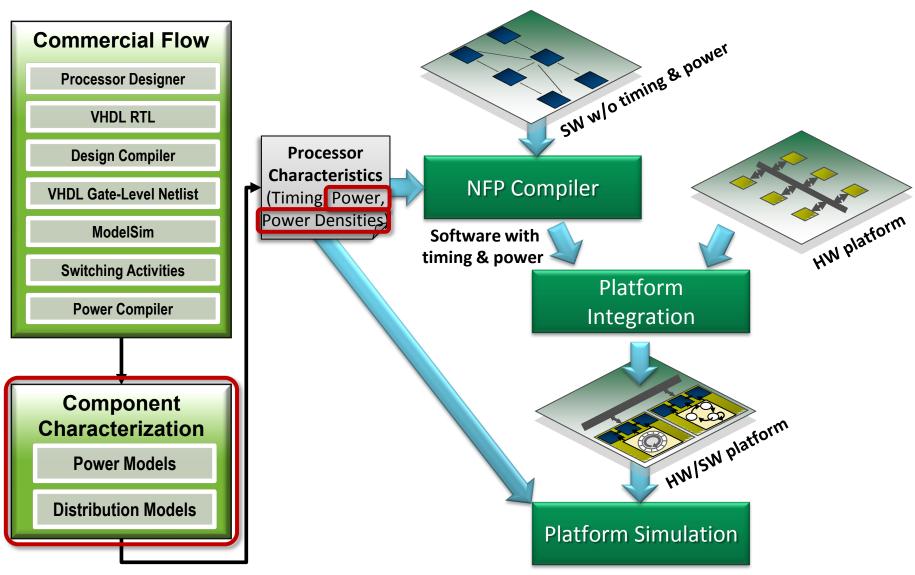

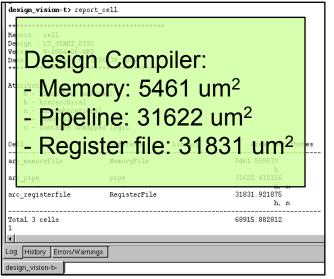

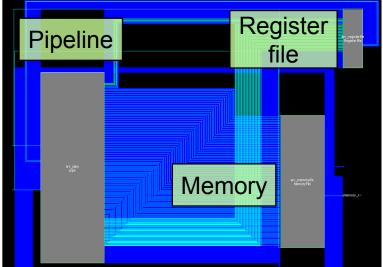

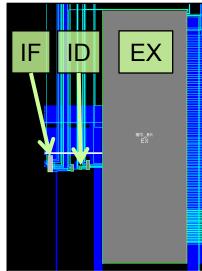

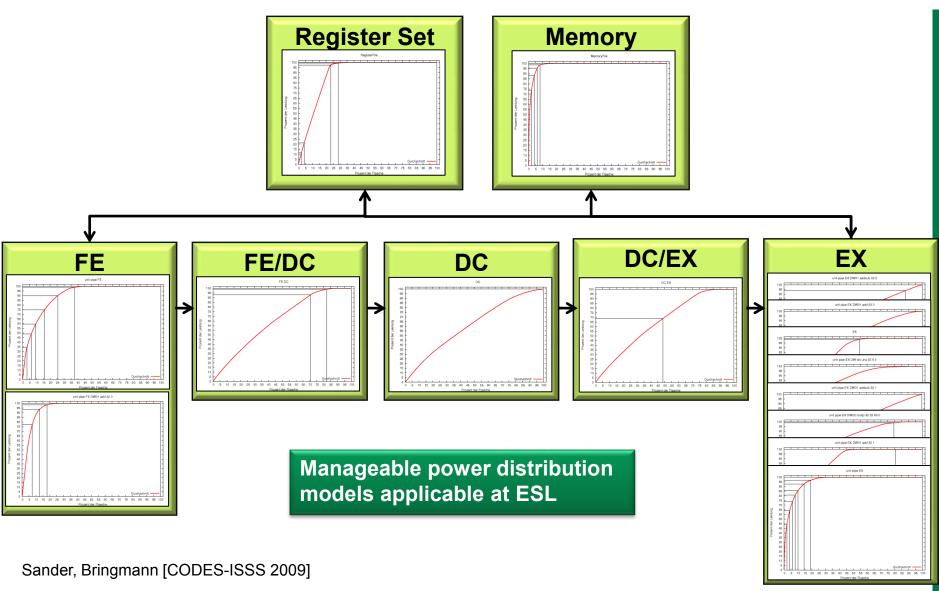

# Power and Power Density Characterization

#### Characterization: Power Distribution Models

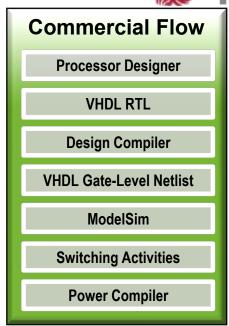

#### **Starting Point:**

- Commercial Tool Chain

- ARM-like processor design

- Used to create accurate power measurements for processor components

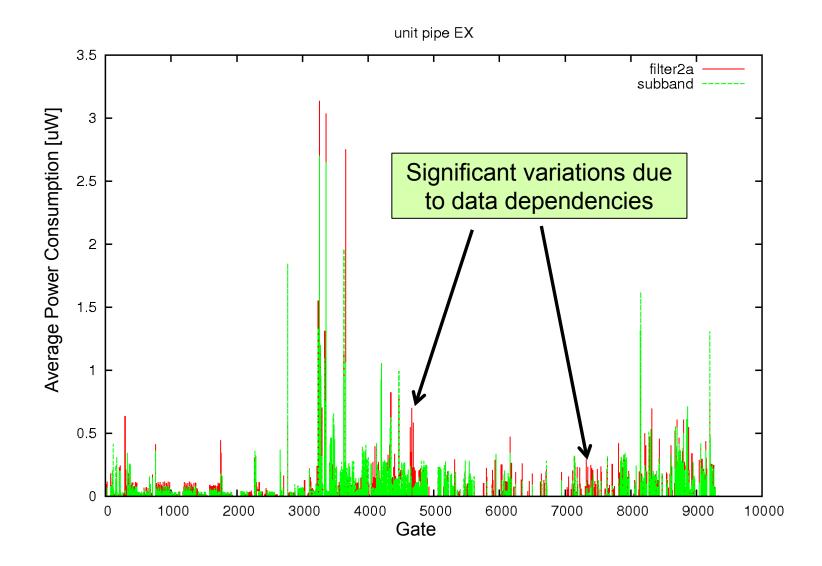

# Gate Average Power Consumption

#### Characterization: Power Distribution Models

#### Characterization: Power Distribution Models

Power Density Models for Temperature Analysis

## Low Power Design: What can be done...

| Low Power Technique                          | Description                                                                     |                                                                  |  |  |

|----------------------------------------------|---------------------------------------------------------------------------------|------------------------------------------------------------------|--|--|

| Multi-Voltage Threshold (MVTH)               | Individual logic gates use transistors with low threshold voltages              | Low Vth (High Speed) - Normal Vth cell - High Vth (Low Leakages) |  |  |

| Clock Gating (CG)                            | Disable registers                                                               |                                                                  |  |  |

| Operand Isolation (OI)                       | Datapath blocks are prevented from swichting (keep in pute constant)  For syste | Combinational Logic m model integration 3 different classes of   |  |  |

| Multiple Operator Voltages (MOV)             | low powe                                                                        | r techniques can be identified:                                  |  |  |

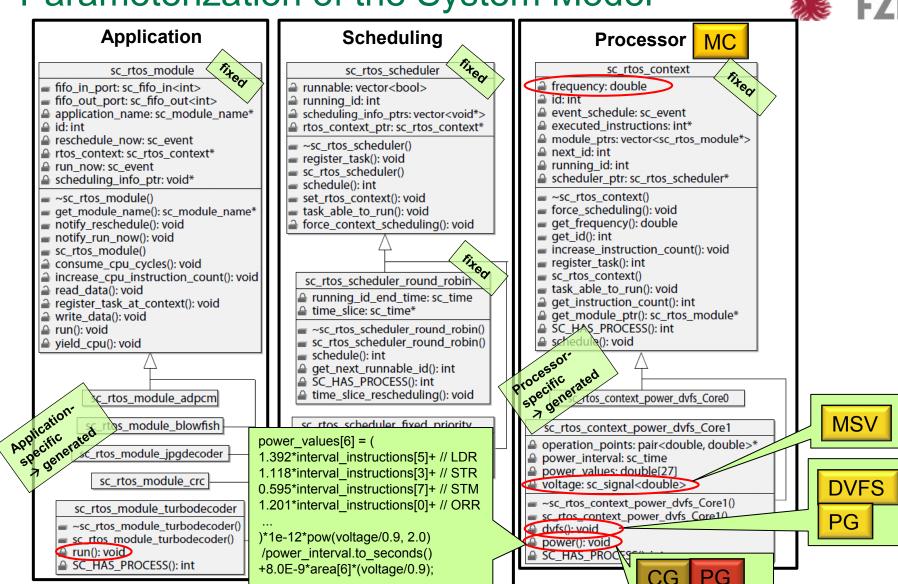

| Multiple Supply Voltages (MSV)  MSV          | Blocks operate with dif supply voltages                                         | "Original circuit " is changed                                   |  |  |

| Dynamic Voltage and Frequency Scaling (DVFS) | A divertical tensor and fine                                                    | Additional hardware is used                                      |  |  |

| DVFS DVFS)                                   | Adjust voltage and fred the fly depending on the                                | Architectural measures                                           |  |  |

| Power Gating (PG) PG PG                      | Torn of supply voltage when not in use                                          | Sleep VCC VCC VCC VCC VCD VCD VCD VCD VCD VCD                    |  |  |

| Multi-Core (MC)  MC                          | Distribute functionality to more than a single processor                        | Functionality on 2 processors => f/2, 0,7*V => power cut in half |  |  |

# Incorporation of Low Power Techniques

# Parameterization of the System Model

<del>■ print trace into(), volu</del>

MTHV

# **AREAS OF APPLICATION**

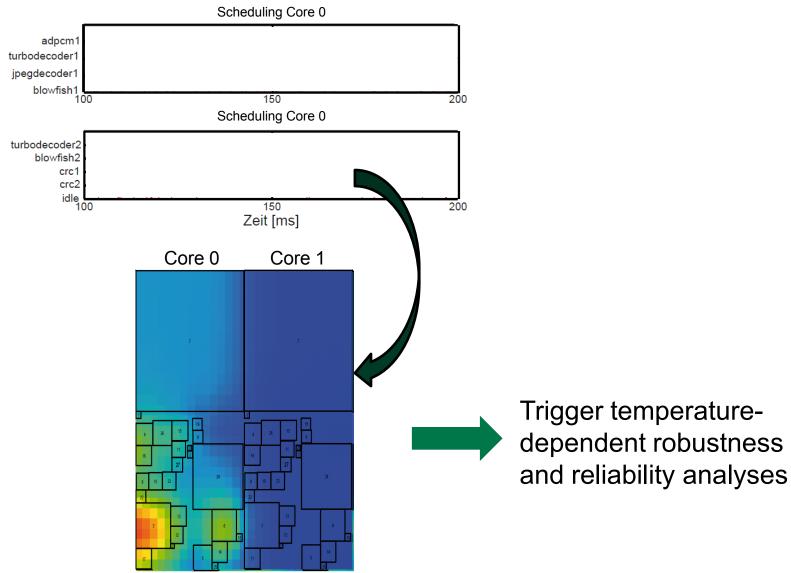

#### **Thermal Simulation**

# Triggering of RT / Gate Level Aging Models

#### **Operating Conditions**

#### Workload

Annotated C/C++ Source Code

#### **Modeled Effects**

- NBTI

- HCI

#### **Aged Component Model**

- gate delay

- output slope

- → aged critical path

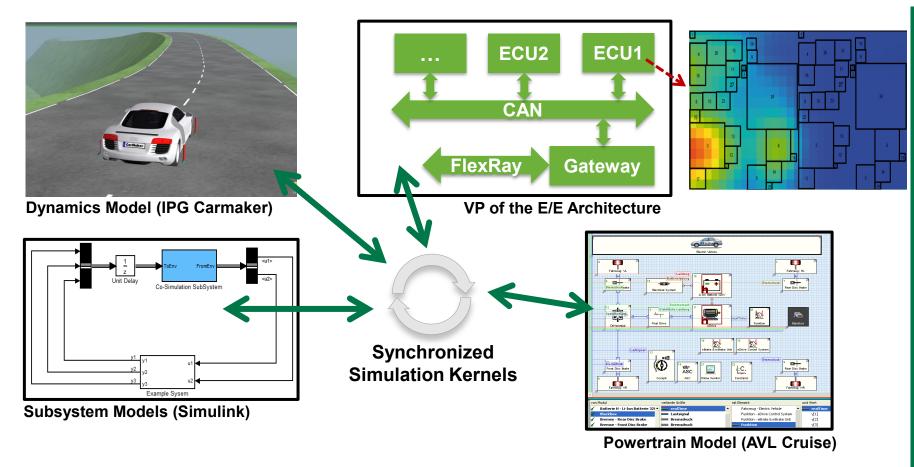

# Platform for Fast Holistic Vehicle Analysis

- Fast co-simulation to cover application and environment context

- Virtual prototype (VP) reflects timing/power/temperature behavior

- Foundation for application/environment-driven robustness analysis

#### Conclusion

- Non-functional properties important issue in embedded SW design

- Real-time simulation possible using source code instrumentation

- Timing and power characteristics are annotated

- Impact of data-dependencies and access to shared resources are solved by dynamic execution

- Highly scalable in terms of the number of processors/processor cores

- Applicable to other non-functional properties like determination of thermal distributions and application-dependent reliability analysis

- Foundation for efficient simulation of heterogeneous HW/SW systems including sensors and actors

#### Thank you very much for your attention!

#### **Questions?**

#### **Oliver Bringmann**

FZI Forschungszentrum Informatik Intelligent Systems and Production Engineering (ISPE) Email: bringmann@fzi.de